# DIGITAL ELECTRONICS

Part if of the text dealt with analog electronic circuits. Part III deals with digital electronics, another important category of electronics.

Chapter 16 examines field-effect transistor digital circuits. MOSFET digital circuits have revolutionized digital electronics, with the CMOS technology producing high-density, low-power digital circuits. Initially, we analyze basic NMOS and CMOS inverters, and then we develop NMOS and CMOS logic gates. Finally in this chapter, we analyze FET shift registers and flip-flops.

Bipolar digital circuits are considered in Chapter 17. We initially examine emitter-coupled logic, which is primarily used in specialized high-speed applications. Then, because transistor-transistor logic (TTL) circuits were the mainstay of logic design for many years, we analyze basic TTL and low-power Schottky TTL circuits, in order to obtain a good comparison between the FET and bipolar digital technologies.

CHAPTER

16

# **MOSFET Digital Circuits**

### 16.0 PREVIEW

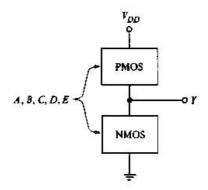

This chapter presents the basic concepts of MOSFET digital integrated circuits, which is the most widely used technology for the fabrication of digital systems. The small transistor size and low power dissipation of CMOS circuits allows for a high level of integration for logic and memory circuits. We initially examine NMOS logic circuits, which contain only n-channel transistors, and then complementary MOS, or CMOS, logic circuits, which contain both n-channel and p-channel transistors. JFET logic circuits are very specialized and are therefore not considered here.

The discussion of NMOS logic circuits will serve as an introduction to the analysis and design of digital circuits. This technology deals with only one type of transistor (n-channel) and therefore makes the analysis more straightforward than dealing with two types of transistors in the same circuit. This discussion will also serve as a baseline to point out the advantages of CMOS technology.

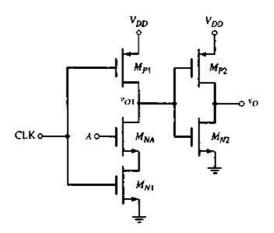

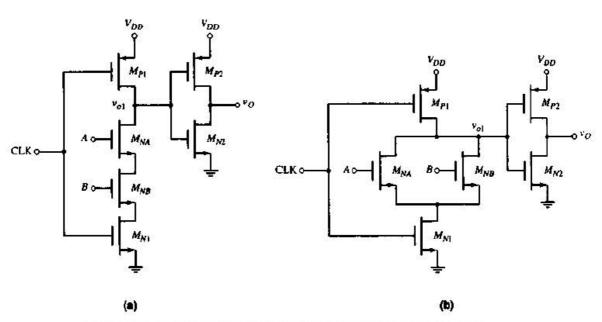

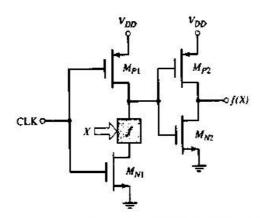

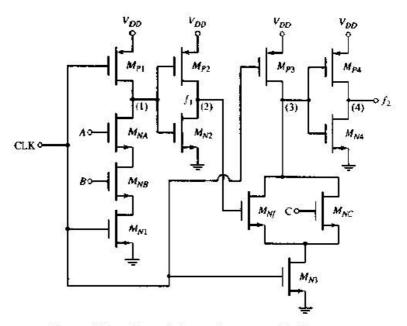

The CMOS inverter is the basis of CMOS logic gates. We will analyze the inverter dc voltage transfer characteristics and will determine the power dissipation in the CMOS inverter, demonstrating the principal advantage of CMOS circuits over NMOS circuits. The CMOS inverter leads to the basic CMOS NOR and NAND logic gates. We also look at more advanced clocked CMOS logic circuits, which eliminate almost half of the transistors in a conventional CMOS logic design while maintaining the lower power advantage of the CMOS technology.

In addition to the basic logic gates that are discussed, we consider additional logic circuits such as flip-flops, shift registers, and adders. Finally, a whole class of digital systems, called memories, is considered. Static memory cells, dynamic memory cells, and read-only memory cells are analyzed. Sense amplifiers and read/write circuitry are briefly discussed.

### 16.1 NMOS INVERTERS

The inverter is the basic circuit of most MOS logic circuits. The design techniques used in NMOS logic circuits are developed from the dc analysis results for the MOS inverter. Extending the concepts developed from the inverter to NOR and NAND gates is then direct. Alternative inverter load elements are

compared in terms of power consumption, packing density, and transfer characteristics. The transient analysis and switching characteristics of the inverters give an indication of the propagation delay times of NMOS logic circuits.

#### 16.1.1 n-Channel MOSFET Revisited

We studied the structure, operation, and characteristics of MOS transistors in Chapter 5. In this section, we will quickly review the n-channel MOSFET characteristics, emphasizing specific properties important in digital circuit design.

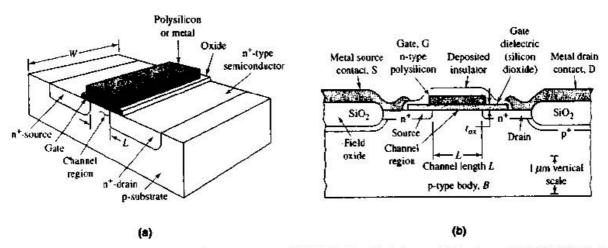

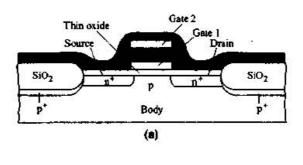

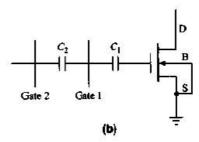

A simplified n-channel MOSFET is shown in Figure 16.1(a). The body, or substrate, is a single-crystal silicon wafer, which is the starting material for circuit fabrication and provides physical support for the integrated circuit. The active transistor region is the surface of the semiconductor and comprises the heavily doped  $n^+$  source and drain regions and p-type channel region. The channel length is L and the channel width is W. Normally, in any given fabrication process, the channel length is the same for all transistors, while the channel width is variable.

Figure 16.1(b) shows a more detailed view of the n-channel MOSFET. This figure demonstrates that the actual device geometry is more complicated than that indicated by the simplified cross section.

Figure 16.1 (a) n-channel MOSFET simplified view and (b) n-channel MOSFET detailed cross section

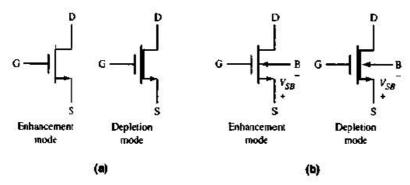

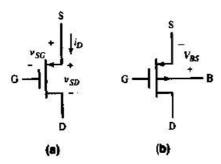

Figure 16.2(a) shows the simplified circuit symbols for the n-channel enhancement- and depletion-mode devices. When we explicitly consider the body or substrate connection, we will use the symbols shown in Figure 16.2(b).

In an integrated circuit, all n-channel transistors are fabricated in the same p-type substrate material. The substrate is connected to the most negative potential in the circuit, which for digital circuits, is normally at ground potential or zero volts. However, the source terminal of many of the transistors will not be at zero volts, which means that a reverse-biased pn junction will exist between the source and substrate.

Figure 16.2 (a) Simplified circuit symbols for n-channel MOSFETs and (b) circuit symbols, showing substrate or body terminal

When the source and body terminals are connected together, the threshold voltage, to a first approximation, is independent of the applied voltages. However, when the source and body voltages are not equal, as when transistors are used for active loads, for instance, the threshold voltage is a function of difference between these voltages. We can write

$$V_{TN} = V_{TNO} + \frac{\sqrt{2e\varepsilon_s N_a}}{C_{ox}} \left[ \sqrt{2\phi_{fp} + V_{SB}} - \sqrt{2\phi_{fp}} \right]$$

$$= V_{TNO} + \gamma \left[ \sqrt{2\phi_{fp} + V_{SB}} - \sqrt{2\phi_{fp}} \right]$$

(16.1)

where  $V_{SB}$  is the source-to-body voltage, and  $V_{TNO}$  is the threshold voltage for zero source-to-body voltage or  $V_{SB}=0$ . The parameter  $N_{\sigma}$  is the p-type substrate doping concentration,  $\varepsilon_{s}$  is the semiconductor permittivity,  $C_{\sigma x}$  is the oxide capacitance per unit area,  $\phi_{fp}$  is a potential related to the substrate doping concentration, and  $\gamma$  is the body-effect coefficient.

**Example 16.1 Objective:** Determine the threshold voltage change due to a source-to-body voltage.

Consider a silicon n-channel MOSFET with the following parameters:  $N_a = 1 \times 10^{16} \,\text{cm}^{-3}$ ,  $t_{ox}$  (oxide thickness) = 500 Å, and  $\phi_{fp} = 0.347 \,\text{V}$ .

Solution: The oxide capacitance is

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = \frac{(3.9)(8.85 \times 10^{-14})}{500 \times 10^{-8}} = 6.9 \times 10^{-8} \text{ F/cm}^2$$

The change in threshold voltage is therefore

$$\begin{split} \Delta V_{TN} &= V_{TN} - V_{TNO} = \frac{\sqrt{2e\varepsilon_1 N_a}}{C_{or}} \Big[ \sqrt{2\phi_{fp} + V_{SB}} - \sqrt{2\phi_{fp}} \Big] \\ &= \frac{\sqrt{2(1.6 \times 10^{-19})(11.7)(8.85 \times 10^{-14})(1 \times 10^{16})}}{6.9 \times 10^{-8}} \Big[ \sqrt{0.694 + V_{SB}} - \sqrt{0.694} \Big] \\ &= 0.834 \Big[ \sqrt{0.694 + V_{SB}} - \sqrt{0.694} \Big] \end{split}$$

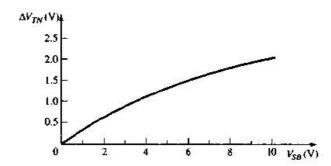

For this case, the body-effect coefficient is  $\gamma = 0.834 \, V^{1/2}$ . The threshold voltage change resulting from a source-to-body voltage  $V_{SB}$  is shown in Figure 16.3.

Figure 16.3 Change in threshold voltage versus source-to-body voltage for n-channel MOSFET in Example 16.1

**Comment:** The threshold voltage change with a change in  $V_{SB}$  will alter the current-voltage characteristics of the device and can alter the output voltage of an inverter.

The current-voltage characterisics of the n-channel MOSFET are functions of both the electrical and geometric properties of the device. When the transistor is biased in the nonsaturation region, for  $v_{GS} \ge V_{TN}$  and  $v_{DS} \le (v_{GS} - V_{TN})$ , we can write

$$i_D = K_n [2(v_{GS} - V_{TN})v_{DS} - v_{DS}^2]$$

(16.2(a))

In the saturation region, for  $v_{GS} \ge V_{TN}$  and  $v_{DS} \ge (v_{GS} - V_{TN})$ , we have

$$i_D = K_n (v_{GS} - V_{TN})^2$$

(16.2(b))

The transition point separates the nonsaturation and saturation regions and is the drain-to-source saturation voltage, which is given by

$$v_{DS} = v_{DS}(\text{sat}) = v_{GS} - V_{TN}$$

(16.3)

The term  $(1 + \lambda v_{DS})$  is sometimes included in Equation (16.2(b)) to account for channel length modulation and the finite output resistance. In most cases, it has little effect on the operating characteristics of MOS digital circuits. In our analysis, the term  $\lambda$  is assumed to be zero unless otherwise stated.

The parameter  $K_n$  is the NMOS transistor conduction parameter and is given by

$$K_n = \left(\frac{1}{2}\mu_n C_{ox}\right) \left(\frac{W}{L}\right) = \frac{k_n'}{2} \frac{W}{L} \tag{16.4}$$

The electron mobility  $\mu_n$  and oxide capacitance  $C_{ox}$  are assumed to be constant for all devices in a particular IC.

The current-voltage characteristics are directly related to the channel width-to-length ratio, or the size of the transistor. In general, in a given IC, the length L is fixed, but the designer can control the channel width W.

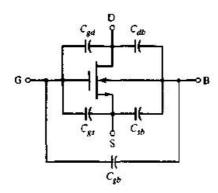

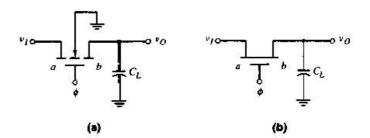

Since the MOS transistor is a majority carrier device, the switching speed of MOS digital circuits is limited by the time required to charge and discharge the capacitances between device electrodes and between interconnect lines and ground. Figure 16.4 shows the significant capacitances in a MOSFET. The capacitances  $C_{ab}$  and  $C_{ab}$  are the source-to-body and drain-to-body  $n^+p$  junction capacitances. The total input gate capacitance, to a first approximation, is a constant equal to

Figure 16.4 in-channel MOSFET and device capacitances

$$C_{g} = WLC_{ox} = WL\left(\frac{\varepsilon_{ox}}{t_{ox}}\right)$$

(16.5)

where  $C_{ax}$  is the oxide capacitance per unit area, and is a function of the oxide thickness. The parameter  $C_{ax}$  also appears in the expression for the conduction parameter.

#### Small Geometry Effects

The current-voltage relationships given by Equations (16.2(a)), (16.2(b)), and (16.3) are first-order approximations that apply to "long" channel devices. The tendency in device design is to make the devices as small as possible, which means the channel length is being reduced to values on the order of 0.25 µm or less. The corresponding channel widths are also being reduced. As the channel length is reduced, several effects alter the current-voltage characteristics. First, the threshold voltage becomes a function of the geometry of the device and is dependent on the channel length. This effect must be taken into account in the design of the transistor. Second, carrier velocity saturation reduces the saturation-mode current below the current value predicted by Equation (16.2(b)). The current is no longer a quadratic function of gate-to-source voltage, and tends to become a linear function of voltage. Channel length modulation means that the current tends to be larger than that predicted by the ideal equation. Third, the electron mobility is a function of the gate voltage so that the current tends to be smaller than the predicted value as the gate-to-source voltage increases. All of these effects complicate the analysis considerably.

We can, however, determine the basic operation and behavior of MOSFET logic circuits by using the first-order equations. We will use these first-order equations in our design of logic circuits. To determine the effect of small device size, a computer simulation may be performed in which the appropriate device models are incorporated in the simulation.

# 16.1.2 NMOS Inverter Transfer Characteristics

Since the inverter is the basis for most logic circuits, we will describe the NMOS inverter and will develop the dc transfer characteristics for three types of inverters with different load devices. This discussion will introduce voltage transfer functions, noise margins, and the transient characteristics of FET digital circuits.

#### NMOS Inverter with Resistor Load

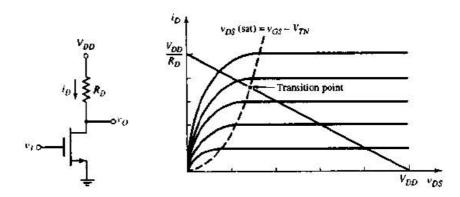

Figure 16.5(a) shows a single NMOS transistor connected to a resistor to form an inverter. The transistor characteristics and load line are shown in Figure 16.5(b), along with the parametric curve separating the saturation and non-saturation regions. We determine the voltage transfer characteristics of the inverter by examining the various regions in which the transistor can be biased.

Figure 16.5 (a) NMOS inverter with resistor load and (b) transistor characteristics and load line

When the input voltage is less than or equal to the threshold voltage, or  $v_I \leq V_{TN}$ , the transistor is cut off,  $i_D = 0$ , and the output voltage is  $v_O = V_{DD}$ . The maximum output voltage is defined as the logic 1 level. As the input voltage becomes just greater than  $V_{TN}$ , the transistor turns on and is biased in the saturation region. The output voltage is then

$$\mathbf{r}_O = V_{DD} - i_D R_D \tag{16.6}$$

where the drain current is given by

$$i_D = K_n (v_{GS} - V_{TN})^2 = K_n (v_I - V_{TN})^2$$

(16.7)

Combining Equations (16.6) and (16.7) yields

$$v_O = V_{DD} - K_n R_D (v_I - V_{TN})^2$$

(16.8)

which relates the output and input voltages as long as the transistor is biased in the saturation region.

As the input voltage increases, the Q-point of the transistor moves up the load line. At the transition point, we have

$$V_{OI} = V_{II} - V_{TN} ag{16.9}$$

where  $V_{Oi}$  and  $V_{Ii}$  are the drain-to-source and gate-to-source voltages, respectively, at the transition point. Substituting Equation (16.9) into (16.8), we determine the input voltage at the transition point from

$$K_n R_D (V_U - V_{TN})^2 + (V_U - V_{TN}) - V_{DD} = 0$$

(16.10)

As the input voltage becomes greater than  $V_{II}$ , the Q-point continues to move up the load line, and the transistor becomes biased in the nonsaturation region. The drain current is then

$$i_D = K_n [2(v_{GS} - V_{TN})v_{DS} - v_{DS}^2] = K_n [2(v_I - v_{TN})v_O - v_O^2]$$

(16.11)

Combining Equations (16.6) and (16.11) yields

$$v_O = V_{DD} - K_u R_D [2(v_I - V_{TN})v_O - v_O^2]$$

(16.12)

which relates the input and output voltages as long as the transistor is biased in the nonsaturation region.

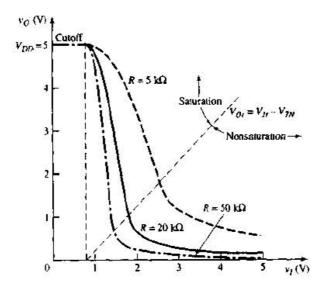

Figure 16.6 shows the voltage transfer characteristics of this inverter for three resistor values. Also shown is the line, given by Equation (16.9), which separates the saturation and nonsaturation bias regions of the transistor. The figure shows that the minimum output voltage, or the logic 0 level, for a high input decreases with increasing load resistance, and the sharpness of the transition region between a low input and a high input increases with increasing load resistance.

Figure 16.6 Voltage transfer characteristics, NMOS inverter with resistor load, for three resistor values

It should be noted that a large resistance is difficult to fabricate in an IC. A large resistor value in the inverter will limit current and power consumption as well as provide a small  $V_{OL}$  value. But it would also require a large chip area if fabricated in a standard MOS process. To avoid this problem MOS transistors can be used as load devices, replacing the resistor, as discussed in subsequent paragraphs.

Example 16.2 Objective: Determine the transition point and minimum output voltage of an NMOS inverter with resistor load.

Consider the circuit in Figure 16.5(a) with parameters  $V_{DD} = 5 \text{ V}$  and  $R_D = 20 \text{ k}\Omega$ . The transistor parameters are  $V_{TN} = 0.8 \text{ V}$  and  $K_n = 0.2 \text{ mA/V}^2$ .

**Solution:** The input voltage at the transition point is found from Equation (16.10). We have

$$(0.2)(20)(V_H - 0.8)^2 + (V_H - 0.8) - 5 = 0$$

which yields

$$V_{tt} - 0.8 = 1$$

or  $V_{tt} = 1.8 \text{ V}$

The output voltage at the transition point is

$$V_{Ot} = V_{It} - V_{TN} = 1.8 - 0.8 = 1 \text{ V}$$

When  $v_I$  is high at  $v_I = 5 \text{ V}$ , the output voltage is found from Equation (16.12). We find

$$v_O = 5 - (0.2)(20)[2(5 - 0.8)v_O - v_O^2]$$

which yields the output low level as

$$v_0 = V_{OL} = 0.147 \text{ V}$$

Only the negative root of the quadratic has physical significance because the positive root yields an output voltage greater than the supply voltage  $V_{DD}$ .

**Comment:** The level of  $V_{OL}$  is less than the threshold voltage  $V_{TN}$ ; therefore, if the output of this inverter is used to drive a similar inverter, the driver transistor of the load inverter would be cut off and its output would be high, which is the desired condition.

# **Test Your Understanding**

[Note: In the following exercise, assume  $k'_n = 35 \,\mu\text{A}/\text{V}^2$  for all NMOS transistors.]

**16.1** Consider the NMOS inverter with resistor load in Figure 16.5(a) biased at  $V_{DD} = 5 \, \text{V}$ . Assume transistor parameters of W/L = 5 and  $V_{TN} = 0.8 \, \text{V}$ . (a) Find the value of  $R_D$  such that  $v_O = 0.15 \, \text{V}$  when  $v_I = 5 \, \text{V}$ . (b) Using the results of part (a), determine the transition point for the driver transistor. (Ans. (a)  $R_D = 44.8 \, \text{k}\Omega$  (b)  $V_H = 1.8 \, \text{V}$ ,  $V_{Ot} = 1.0 \, \text{V}$ )

### NMOS Inverter with Enhancement Load

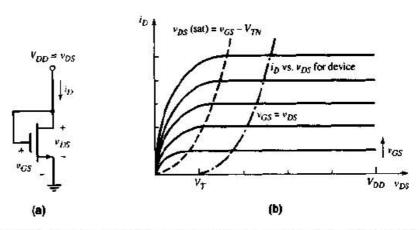

An n-channel enhancement-mode MOSFET with the gate connected to the drain can be used as a load device in an NMOS inverter. Figure 16.7(a) shows such a device. For  $v_{GS} = v_{DS} \le V_{TN}$ , the drain current is zero. For

Figure 16.7 (a) n-channel MOSFET connected as saturated load device and (b) current-voltage characteristics of saturated load device

$v_{GS} = v_{DS} > V_{TN}$ , a nonzero drain current is induced in the device. We can see that the following condition is satisfied:

$$v_{DS} > (v_{GS} - V_{TN}) = (v_{DS} - V_{TN}) = v_{DS}(\text{sat})$$

(16.13)

A transistor with this connection always operates in the saturation region when not in cutoff.

The drain current is

$$i_D = K_n (v_{GS} - V_{TN})^2 = K_n (v_{DS} - V_{TN})^2$$

(16.14)

We continue to neglect the effect of the output resistance and the  $\lambda$  parameter. The  $i_D$  versus  $v_{DS}$  characteristic is shown in Figure 16.7(b), which indicates that this device acts as a nonlinear resistor.

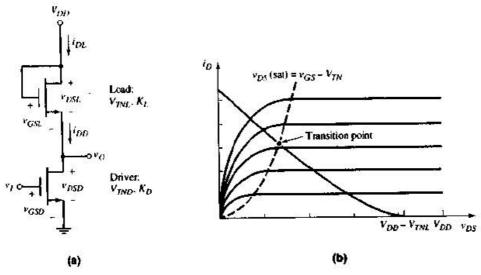

Figure 16.8(a) shows an NMOS inverter with the enhancement load device. The driver transistor parameters are denoted by  $V_{TND}$  and  $K_D$ , and the load transistor parameters are denoted by  $V_{TNL}$  and  $K_L$ . The substrate connections are not shown. In the following analysis, we neglect the body effect and we assume all threshold voltages are constant. These assumptions do not seriously affect the basic analysis, nor the inverter characteristics.

The driver transistor characteristics and the load curve are shown in Figure 16.8(b). When the inverter input voltage is less than the driver threshold voltage, the driver is cut off and the drain currents are zero. From Equation (16.14), we have

$$i_{DI} = 0 = K_I (v_{DSI} - V_{TNI})^2 ag{16.15}$$

From Figure 16.8(a), we see that  $v_{DSL} = V_{DD} - v_0$ , which means that

$$v_{DSL} - V_{TNL} = V_{DD} - v_O - V_{TNL} = 0$$

(16.16(a))

The maximum output voltage is then

$$v_{O,\text{max}} \equiv V_{OH} = V_{DD} - V_{TNL}$$

(16.16(b))

Figure 16.8 (a) NMOS inverter with saturated load and (b) driver transistor characteristics and load curve

For the enhancement-load NMOS inverter, the maximum output voltage, which is the logic 1 level, does not reach the full  $V_{DD}$  value. This cutoff point is shown in the load curve in Figure 16.8(b).

As the input voltage becomes just greater than the driver threshold voltage  $V_{TND}$ , the driver transistor turns on and is biased in the saturation region. In steady-state, the two drain currents are equal since the output will be connected to the gates of other MOS transistors. We have  $i_{DD} = i_{DL}$ , which can be written as

$$K_D(v_{GSD} - V_{TND})^2 = K_L(v_{GSL} - V_{TNL})^2$$

(16.17)

Equation (16.17) is expressed in terms of the individual transistor parameters. In terms of the input and output voltages, the expression becomes

$$K_D(\nu_I - V_{TND})^2 = K_L(V_{DD} - \nu_O - V_{TNL})^2$$

(16.18)

Solving for the output voltage yields

$$v_O = V_{DD} - V_{TNL} - \sqrt{\frac{K_D}{K_L}} (v_l - V_{TND})$$

(16.19)

As the input voltage increases, the driver Q-point moves up the load curve and the output voltage decreases linearly with  $v_I$ .

At the driver transition point, we have

$$v_{DSD}(\text{sat}) = v_{GSD} - V_{TND}$$

or

$$V_{Ot} = V_{tt} - V_{TND} ag{16.20}$$

Substituting Equation (16.20) into (16.19), we find the input voltage at the transition point, which is

$$V_{II} = \frac{V_{DD} - V_{TNL} + V_{TND} \left(1 + \sqrt{\frac{K_D}{K_L}}\right)}{1 + \sqrt{\frac{K_D}{K_L}}}$$

(16.21)

As the input voltage becomes greater than  $V_{II}$ , the driver transistor Q-point continues to move up the load curve and the driver becomes biased in the nonsaturation region. Since the driver and load drain currents are still equal, or  $i_{DD} = i_{DL}$ , we now have

$$K_D[2(v_{GSD} - V_{TND})v_{DSD} - v_{DSD}^2] = K_L(v_{DSL} - V_{TNL})^2$$

(16.22)

Writing Equation (16.22) in terms of the input and output voltages produces

$$K_D[2(v_I - V_{TND})v_O - v_O^2] = K_L(V_{DD} - v_O - V_{TNL})^2$$

(16.23)

Obviously, the relationship between  $v_I$  and  $v_O$  in this region is not linear.

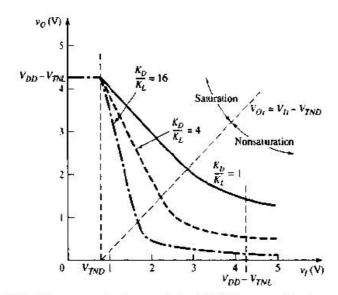

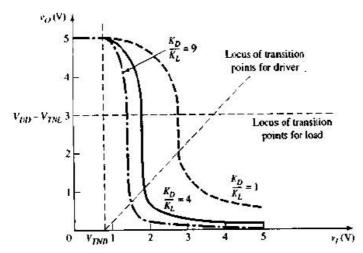

Figure 16.9 shows the voltage transfer characteristics of this inverter for three  $K_D$ -to- $K_L$  ratios. The ratio  $K_D/K_L$  is the aspect ratio and is related to the width-to-length parameters of the driver and load transistors.

The line, given by Equation (16.20), separating the driver saturation and nonsaturation regions is also shown in the figure. We see that the minimum

Figure 16.9 Voltage transfer characteristics, NMOS inverter with saturated load, for three aspect ratios

output voltage, or the logic 0 level, for a high input decreases with an increasing  $K_D/K_L$  ratio. As the width-to-length ratio of the load transistor decreases, the effective resistance increases, which means that the general behavior of the transfer characteristics is the same as for the resistor load. However, the high output voltage is

$$V_{OH} = V_{DD} - V_{TNL}$$

When the driver is biased in the saturation region, we find the slope of the transfer curve, which is the **inverter gain**, by taking the derivative of Equation (16.19) with respect to  $v_L$ . We see that

$$dv_O/dv_I = -\sqrt{K_D/K_L}$$

When the aspect ratio is greater than unity, the inverter gain magnitude is greater than unity. A logic circuit family with an inverter transfer curve that exhibits a gain greater than unity for some region is called a **restoring logic family**. Restoring logic is so named because logic signals that are degraded for some reason in one circuit can be restored by the gain of subsequent logic circuits.

**Design Example 16.3 Objective:** Design the aspect ratio  $K_D/K_L$  to produce a specified low output voltage, and determine the power dissipation in the inverter with enhancement load for a minimum W/L ratio for the load transistor. (Neglect the body effect.)

Consider the inverter shown in Figure 16.8(a) biased at  $V_{DD} = 5 \, \text{V}$ . The transistor parameters are:  $V_{TND} = V_{TNL} = 0.8 \, \text{V}$  and  $k_n' = 35 \, \mu \text{A/V}^2$ . Determine  $K_D/K_L$  such that  $v_0 = 0.10 \, \text{V}$  when  $v_I = \text{Logic I} = 4.2 \, \text{V}$ , and determine  $(W/L)_D$  and the power dissipation in the inverter for  $(W/L)_L = 0.5$  and  $v_I = 4.2 \, \text{V}$ .

**Solution:** For  $v_I = 4.2 \,\text{V}$ , the driver transistor is biased in the nonsaturation region. Using Equation (16.23), we have

$$\frac{K_D}{K_L} [2(4.2 - 0.8)(0.1) - (0.1)^2] \approx (5 - 0.1 - 0.8)^2$$

which yields

$$\frac{K_D}{K_L} = 25.1$$

Since

$$\frac{K_D}{K_L} = \frac{(W/L)_D}{(W/L)_L}$$

then

$$(W/L)_D = 12.6$$

when

$$(W/L)_L = 0.5$$

The power dissipated in the inverter is  $P = i_D V_{DD}$ , and the drain current can be found from the load transistor, as follows:

$$i_0 = K_L (V_{DD} - v_O - V_{TNL})^2 = \frac{k_n'}{2} \left( \frac{W}{L} \right)_L (V_{DD} - v_O - V_{TNL})^2$$

Therefore.

$$i_B = \left(\frac{35}{2}\right)(0.5)(5 - 0.1 - 0.8)^2 = 147 \,\mu\text{A}$$

The power dissipation is

$$P = i_D V_{DD} \approx (147)(5) = 735 \mu W$$

Comment: In the NMOS inverter with enhancement load, producing a relatively low output voltage  $V_{OL}$  requires a large difference in the sizes of the driver and load transistors. The load transistor size cannot be substantially reduced, so the power consumption also cannot be substantially reduced from the  $735\,\mu\text{W}$  value. If an IC contained a modest 100,000 inverters and all inverters were conducting, the total required current to the IC would be 14.7 A and the total power dissipated would be 73.5 W! We thus see the need to drastically reduce the power dissipation in each inverter.

# **Test Your Understanding**

[Assume  $k_n' = 35 \,\mu \text{A/V}^2$ .]

**16.2** The enhancement-load NMOS inverter shown in Figure 16.8(a) is biased at  $V_{DD} = 5 \text{V}$ . The threshold voltages are  $V_{TND} = V_{TNL} = 1 \text{ V}$ , and the width-to-length ratios are  $(W/L)_D = 16$  and  $(W/L)_L = 2$ . (a) Find  $v_O$  when: (i)  $v_I = 0$ , and (ii)  $v_I = 4 \text{ V}$ . (b) Calculate the power dissipated in the inverter when  $v_I = 4 \text{ V}$ . (Ans. (a)  $v_O = 4 \text{ V}$ ,  $v_O = 0.30 \text{ V}$  (b) P = 2.4 mW)

**D16.3** Consider the NMOS inverter with enhancement load, as shown in Figure 16.8(a), biased at  $V_{DD} = 5$ V. The transistor threshold voltages are  $V_{TND} = V_{TNL} = 0.8$ V. Design the width-to-length ratios such that the output voltage is 0.2V and the inverter power dissipation is 750 µW when  $v_I = 4.2$  V. (Ans.  $(W/L)_L = 0.536$ ,  $(W/L)_D = 6.49$ )

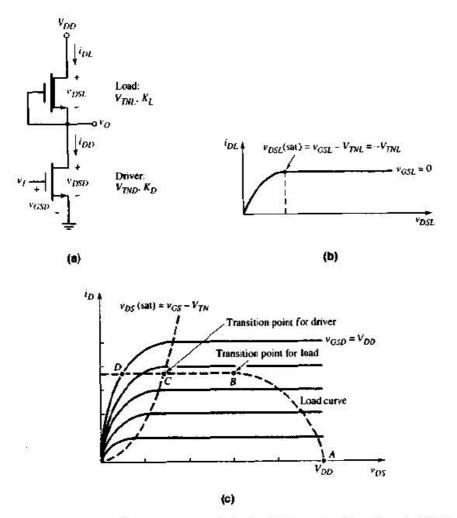

### NMOS Inverter with Depletion Load

Depletion-mode MOSFETs can also be used as load elements in NMOS inverters. Figure 16.10(a) shows the NMOS inverter with depletion load. The gate and source of the depletion-mode transistor are connected together. The driver transistor is still an enhancement-mode device. As before, the driver transistor parameters are  $V_{TND}(V_{TND} > 0)$  and  $K_D$ , and the load transistor parameters are  $V_{TNL}(V_{TNL} < 0)$  and  $K_L$ . Again, the substrate connections are not shown. The fabrication process for this inverter is slightly more complicated than for

Figure 16.10 (a) NMOS inverter with depletion load, (b) current-voltage characteristic of depletion load, and (c) driver translator characteristics and load curve

the enhancement-load inverter, since the threshold voltages of the two devices are not equal. However, as we will see, the advantages of this inverter make the extra processing steps worthwhile. This inverter has been the basis of many microprocessor and static memory designs.

The current-voltage characteristic curve for the depletion load, neglecting the body effect, is shown in Figure 16.10(b). Since the gate is connected to the source,  $v_{GSL} = 0$ , and the Q-point of the load is on this particular curve.

The driver transistor characteristics and the ideal load curve are shown in Figure 16.10(c). When the inverter input is less than the driver threshold voltage, the driver is cut off and the drain currents are zero. From Figure 16.10(b), we see that for  $i_D = 0$ , the drain-to-source voltage of the load transistor must be zero; therefore,  $v_O = V_{DD}$  for  $v_I \leq V_{TND}$ . An advantage of the depletion-load inverter over the enhancement-load inverter is that the high output voltage, or the logic 1 level, is at the full  $V_{DD}$  value.

As the input voltage becomes just greater than the driver threshold voltage  $V_{TND}$ , the driver turns on and is biased in the saturation region; however, the load is biased in the nonsaturation region. The Q-point lies between points A and B on the load curve shown in Figure 16.10(c). We again set the two drain currents equal, or  $i_{DD} = i_{DL}$ , which means that

$$K_D[v_{GSD} - V_{TND}]^2 = K_L[2(v_{GSL} - V_{TNL})v_{DSL} - v_{DSL}^2]$$

(16.24)

Writing Equation (16.24) in terms of the input and output voltages yields

$$K_D[\nu_I - V_{TND}]^2 = K_L[2(-V_{TNL})(V_{DD} - \nu_O) - (V_{DD} - \nu_O)^2]$$

(16.25)

This equation relates the input and output voltages as long as the driver is biased in the saturation region and the load is biased in the nonsaturation region.

There are two transition points for the NMOS inverter with a depletion load: one for the load and one for the driver. These are points B and C, respectively, in Figure 16.10(c). The transition point for the load is given by

$$v_{DSL} = V_{DD} - V_{Ot} = v_{GSL} - V_{TNL} = -V_{TNL}$$

(16.26(a))

Of .

$$V_{OI} = V_{DD} + V_{TNL} ag{16.26(b)}$$

Since  $V_{TNL}$  is negative, the output voltage at the transition point is less than  $V_{DD}$ . The transition point for the driver is given by

$$v_{DSD} = v_{GSD} - V_{TND}$$

or

$$V_{Ot} = V_{ft} - V_{TND} ag{16.27}$$

When the Q-point lies between points B and C on the load curve, both devices are biased in the saturation region, and

$$K_D(v_{GSD} - V_{TND})^2 = K_L(v_{GSL} - V_{TNL})^2$$

(16.28(a))

OF

$$\sqrt{\frac{K_D}{K_L}}(v_l - V_{TND}) = -V_{TNL}$$

(16.28(b))

Equation (16.28(b)) demonstrates that the input voltage is a constant as the Q-point passes through this region. This effect is also shown in Figure 16.10(c); the load curve between points B and C lies on a constant  $v_{GSD}$  curve. (This characteristic will change when the body effect is taken into account.)

For an input voltage greater than the value given by Equation (16.28(b)), the driver is biased in the nonsaturation region while the load is biased in the saturation region. The Q-point is now between points C and D on the load curve in Figure 16.10(c). Equating the two drain currents, we obtain

$$K_D[2(v_{GSD} - V_{TND})v_{DSD} - v_{DSD}^2] = K_L(v_{GSL} - V_{TNL})^2$$

(16.29(a))

which becomes

$$\frac{K_D}{K_L} \left[ 2(v_i - V_{TND})v_O - v_O^2 \right] = (-V_{TNL})^2$$

(16.29(b))

This equation implies that the relationship between the input and output voltages are not linear in this region.

Figure 16.11 shows the voltage transfer characteristics of this inverter for three values of  $K_D/K_L$ . Also shown are the locus of transition points for the load and driver transistors as given by Equations (16.26(b)) and (16.27), respectively.

Figure 16.11 Voltage transfer characteristics, NMOS inverter with depletion load, for three aspect ratios

**Design Example 16.4 Objective:** Design the aspect ratio  $K_D/K_L$  to produce a specified low output voltage, and determine the power dissipation in the inverter with depletion load for a minimum W/L ratio for the load transistor.

Consider the inverter in Figure 16.10(a) biased at  $V_{DD}=5\,\mathrm{V}$ . The transistor parameters are:  $V_{TND}=0.8\,\mathrm{V}$ ,  $V_{TNL}=-2\,\mathrm{V}$ , and  $k_n'=35\,\mu\mathrm{A/V}^2$ . Determine  $K_D/K_L$  such that  $v_O=0.10\,\mathrm{V}$  when  $v_I=5\,\mathrm{V}$ . Determine  $(W/L)_D$  and the power dissipation in the inverter for  $(W/L)_L=0.5$ .

**Solution:** For  $v_I = 5$  V, we assume the driver transistor is biased in the nonsaturation region and the load is in the saturation region. Using Equation (16.29(b)), we have

$$\frac{K_D}{K_L} \left[ 2(5 - 0.8)(0.1) - (0.1)^2 \right] = [-(-2)]^2$$

which yields

$$\frac{K_D}{K_I} = 4.82$$

Since

$$\frac{K_D}{K_L} = \frac{(W/L)_D}{(W/L)_L}$$

then

$$(W/L)_D = 2.41$$

when

$$(W/L)_L = 0.5$$

The power dissipated in the inverter is  $P = i_D V_{DD}$ , and the drain current can be found from the load transistor, as follows:

$$i_D = K_L (-V_{TNL})^2 = \frac{k_N'}{2} \left(\frac{W}{L}\right)_L (-V_{TNL})^2 = \left(\frac{35}{2}\right) (0.5)[-(-2)]^2 = 35 \,\mu\text{A}$$

The power dissipation is therefore

$$P = i_D V_{DD} = (35)(5) = 175 \,\mu\text{W}$$

**Comment:** A relatively low output voltage  $V_{OL}$  can be produced in the NMOS inverter with depletion load, even when the load and driver transistors are not vastly different in size. The power dissipation in this inverter is also substantially less than in the enhancement-load inverter since the aspect ratio is smaller.

**Design Consideration:** The static analysis of the three types of NMOS inverters clearly demonstrates the advantage of the depletion load inverter. The size of the driver transistor is smaller for a given load device size to produce a given low output state. This allows a greater number of inverters to be fabricated in a given chip area. In addition, since the power dissipation is less, more inverters can be fabricated on a chip for a given total power dissipation.

#### **Test Your Understanding**

[Assume  $k_n' = 35 \mu A/V^2$ .]

**\*16.4** The depletion load NMOS inverter shown in Figure 16.10(a) is biased at  $V_{DD} = 5 \text{ V}$ , the transistor parameters are:  $V_{TND} = 0.7 \text{ V}$ ,  $V_{TNL} = -1.5 \text{ V}$ ,  $(W/L)_D = 6$ , and  $(W/L)_L = 2$ . (a) Determine  $v_O$  for  $v_I = 5 \text{ V}$ . (b) Find the transition points for the driver and the load. (c) Calculate the power dissipation in the inverter when  $v_I = 5 \text{ V}$ . (Ans. (a)  $v_O = 0.0881 \text{ V}$  (b) Load:  $v_H = 1.57 \text{ V}$ ,  $v_{OI} = 3.5 \text{ V}$ . Driver:  $v_H = 1.57 \text{ V}$ ,  $v_{OI} = 0.87 \text{ V}$  (c)  $P = 394 \mu\text{W}$ )

**D16.5** Consider the depletion load inverter in Figure 16.10(a) biased at  $V_{DD} = 5 \text{ V}$ . The threshold voltages are  $V_{TND} = 0.8 \text{ V}$  and  $V_{TNL} = -2 \text{ V}$ . Design the inverter such that the maximum power dissipation is 350 µW and the output voltage is 0.05 V when  $v_l = 5 \text{ V}$ . (Ans.  $(W/L)_L = 1$ ,  $(W/L)_D = 9.58$ )

#### 16.1.3 Noise Margin

The word "noise" means transient, unwanted variations in voltages or currents. In digital circuits, if the magnitude of the noise at a logic node is too large, logic errors can be introduced into the system. However, if the noise amplitude is less than a specified value, called the noise margin, the noise signal will be attenuated as it passes through a logic gate or circuit, while the logic signals will be transmitted without error.

Noise signals are usually generated outside the digital circuit and transferred to logic nodes or interconnect lines through parasitic capacitances or inductances. The coupling process is usually time dependent, leading to dynamic conditions in the circuit. In digital systems, however, the noise margins are usually defined in terms of static voltages.

### Noise Margin Definition

For static noise margins, the type of noise usually considered is called series-voltage noise. Figure 16.12 shows two inverters in series in which the output of the second is connected back to the input of the first. Also included are series-voltage noise sources  $\delta V_L$  and  $\delta V_H$ . This type of noise can be developed by inductive coupling. The input voltage levels are indicated by H (high) and L (low). The noise amplitudes  $\delta V_L$  and  $\delta V_H$  can be different, and the polarities may be such as to increase the low output and reduce the high output. The noise margins are defined as the maximum values of  $\delta V_L$  and  $\delta V_H$  at which the inverters will remain in the correct state.

Figure 16.12 Two-inverter flip-flop, including series-voltage noise sources

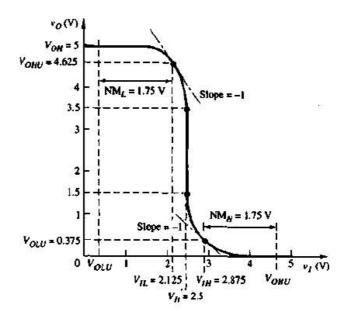

The actual definitions of the noise margins  $NM_L$  and  $NM_H$  are not unique. In addition other types of noise, other than series-voltage source noise, may be present in the system. Dynamic noise sources also complicate the issue. However, in this text, in order to provide some measure of noise margin in a logic circuit, we will use the unity-gain approach to determine the logic threshold levels  $V_{IL}$  and  $V_{IH}$  and the corresponding noise margins.

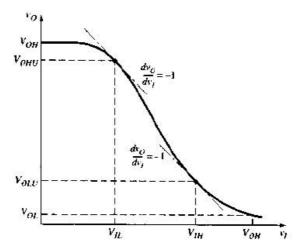

Figure 16.13 shows a general voltage transfer function for an inverter. The expected logic 1 and logic 0 output voltages of the inverter are  $V_{OH}$  and  $V_{OL}$ , respectively. The parameters  $V_{IH}$  and  $V_{IL}$ , which determine the noise margins, are defined as the points at which

$$\frac{d\mathbf{v}_O}{d\mathbf{v}_I} = -1 \tag{16.30}$$

For  $v_I \leq V_{IL}$ , the inverter gain magnitude is less than unity, and the output changes slowly with a change in the input voltage. Similarly, for  $v_I \geq V_{IH}$ , the output again changes slowly with input voltage since the gain magnitude is less than unity. However, when the input voltage is in the range  $V_{IL} < v_I < V_{IH}$ , the gain magnitude is greater than one, and the output signal changes rapidly.

Figure 16.13 Generalized inverter voltage curve and defined voltage limits  $V_{IL}$  and  $V_{IH}$

This region is called the undefined range. If the input voltage is inadvertently pushed into this range by a noise signal, the output may change logic states, and a logic error could be introduced into the system. The corresponding output voltages at the unity-gain points are denoted  $V_{OHU}$  and  $V_{OLU}$ , where the last subscript U signifies the unity-gain values.

The noise margins are defined as

$$NM_L = V_{IL} - V_{OLU}$$

(16.31(a))

and

$$NM_{H} = V_{OHU} - V_{IH} {16.31(b)}$$

We will see how these noise margin definitions correspond to the flip-flop conditions just discussed.

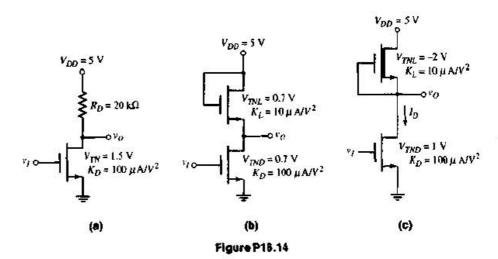

Since an inverter with a resistor load is rarely used in practice, we will determine the noise margins for NMOS inverters with enhancement and depletion loads.

#### Enhancement-Load Inverter

The general voltage transfer characteristic for the NMOS inverter with enhancement load is shown in Figure 16.14. Normally,  $K_D > K_L$  and the gain magnitude for  $v_I > V_{TND}$  is greater than one. Since the slope for this ideal curve is discontinuous at  $v_I = V_{TND}$ , we define the parameter  $V_{IL} \equiv V_{TND}$ . This is the threshold voltage of the driver. In this case, the output voltage  $V_{OHU}$  corresponds to  $V_{OH}$ .

At voltage  $V_{IH}$ , the driver is biased in the nonsaturation region. The relationship between the input and output voltages is given by Equation (16.23). Taking the derivative with respect to  $v_I$ , we obtain

$$2K_{D}v_{O} + 2K_{D}v_{I}\frac{dv_{O}}{dv_{I}} - 2K_{D}V_{TND}\frac{dv_{O}}{dv_{I}} - 2K_{D}v_{O}\frac{dv_{O}}{dv_{I}}$$

$$= -2K_{L}(V_{DD} - v_{O} - V_{TNL})\frac{dv_{O}}{dv_{I}}$$

(16.32)

**Figure 16.14** Voltage transfer characteristic, NMOS inverter with saturated load, and defined voltage limits  $V_{ii}$  and  $V_{iH}$

Setting the derivative equal to -1 yields

$$K_D v_O - K_D v_I + K_D V_{TND} + K_D v_O = + K_L (V_{DD} - v_O - V_{TNL})$$

(16.33)

Solving for  $v_O$ , we obtain

$$v_{O} = V_{OLU} = \frac{(V_{DD} - V_{TNL}) + \frac{K_{D}}{K_{L}}(v_{I} - V_{TND})}{1 + 2\frac{K_{D}}{K_{L}}}$$

(16.34)

Finally, combining Equations (16.34) and (16.23) and solving for  $v_I$ , we have

$$v_{I} = V_{IH} = V_{TND} + \left(\frac{V_{DD} - V_{TNL}}{\frac{K_{D}}{K_{L}}}\right) \left(\frac{1 + 2\frac{K_{D}}{K_{L}}}{\sqrt{1 + 3\frac{K_{D}}{K_{L}}}} - 1\right)$$

(16.35)

**Example 16.5 Objective:** Determine the noise margins of an inverter with enhancement load.

Consider the inverter shown in Figure 16.8(a) with the parameters given in Example 16.3. We have that  $V_{OH} = 4.2 \text{ V}$ ,  $V_{OL} = 0.10 \text{ V}$ , and  $K_D/K_L = 25.1$ .

**Solution:** We know that  $V_{IL} = V_{TND} = 0.8 \text{ V}$  and  $V_{OHU} = V_{OH} = 4.2 \text{ V}$ . The value of  $V_{IH}$  is, from Equation (16.35),

$$V_{IH} = 0.8 + \left(\frac{5 - 0.8}{25.1}\right) \left[\frac{1 + 2(25.1)}{\sqrt{1 + 3(25.1)}} - 1\right] = 1.61 \text{ V}$$

The output voltage corresponding to  $V_{IH}$  is, from Equation (16.34),

$$v_O = V_{OLU} = \frac{(5 - 0.8) + (25.1)(1.61 - 0.8)}{1 + 2(25.1)} = 0.479 \text{ V}$$

The noise margins are

$$NM_L = V_{IL} - V_{OLU} = 0.8 - 0.479 = 0.321 \text{ V}$$

and

$$NM_H = V_{OHU} - V_{IH} = 4.2 - 1.61 = 2.59 V$$

**Comment:** This example shows that the two noise margins are not necessarily equal. In addition, the output voltage corresponding to  $V_{IH}$  is less than the threshold voltage of a driver transistor driven by the inverter. This means that as long as  $v_I$  remains in the range  $V_{IH} \le v_I \le V_{OH}$ , no logic error will be transmitted through a digital system.

The results of this example can be compared to the flip-flop conditions in Figure 16.12. Figure 16.15 shows two inverters in series, including series-voltage noise sources. If the input is high at  $V_{OHU} = 4.2 \,\mathrm{V}$  and if a noise source of  $\delta V_H = \mathrm{NM}_H = 2.59 \,\mathrm{V}$  is included, the input to inverter  $G_1$  is 1.61 V corresponding to  $V_{IH}$ , which is the minimum value corresponding to a logic 1 level. With an input of  $V_{IH} = 1.61 \,\mathrm{V}$  to  $G_1$ , the output is 0.479 V. If a noise source of  $\delta V_L = \mathrm{NM}_L = 0.321 \,\mathrm{V}$  is present, then input to  $G_2$  is 0.8 V corresponding to  $V_{IL}$ , which is the minimum value corresponding to a logic 0 level. With an input of  $V_{IL} = 0.8 \,\mathrm{V}$  to  $G_2$ , the output is 4.2 V. If the output is connected back to the input, the resulting flip-flop configuration is in a stable state, although at the edge of switching. If the noise sources  $\delta V_H$  and  $\delta V_L$  increase slightly above the noise margins, the flip-flop will switch states.

$$V_{OH} = V_{IH} = G_1 L V_{IL} = G_2 V_{OH} = 4.2 \text{ V}$$

$$\delta V_H = NM_H = 2.59 \text{ V}$$

$$0.321 \text{ V}$$

$$0.321 \text{ V}$$

Figure 16.15 Two inverters and two series-voltage noise sources with the noise margins from Example 16.5

#### **Test Your Understanding**

**16.6** For the transistors in the NMOS inverter with enhancement load, the parameters are  $V_{TN}=0.85\,\mathrm{V}$  and  $K_D/K_L=16$ . Let  $V_{DD}=5\,\mathrm{V}$ . Determine  $V_{IL},\,V_{IH},\,\mathrm{NM}_L$ , and  $\mathrm{NM}_H$ . (Ans.  $V_{IH}=1.81\,\mathrm{V},\,V_{IL}=0.85\,\mathrm{V},\,\mathrm{NM}_L=0.259\,\mathrm{V},\,\mathrm{NM}_H=2.34\,\mathrm{V}$ )

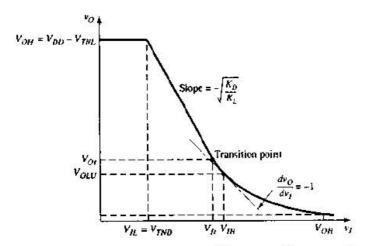

#### Depletion-Load Inverter

The general transfer characteristic of the NMOS inverter with depletion load is shown in Figure 16.16. The point  $V_{IL}$  occurs when the load is biased in the nonsaturation region and the driver is biased in the saturation region. The relationship between the input and output voltages is given by Equation (16.25). Taking the derivative with respect to  $v_I$ , we obtain

$$2K_{D}[v_{I} - V_{TND}] = K_{L} \left[ 2(-V_{TNL}) \left( -\frac{dv_{O}}{dv_{I}} \right) - 2(V_{DD} - v_{O}) \left( -\frac{dv_{O}}{dv_{I}} \right) \right]$$

(16.36)

Figure 16.16 Voltage transfer characteristic, inverter with depletion load, and the defined voltage limits  $V_R$  and  $V_M$

Setting the derivative equal to -1 and solving for  $v_0$  yields

$$v_O = V_{OHU} = (V_{DD} + V_{TNL}) + \left(\frac{K_D}{K_L}\right)(v_I - V_{TND})$$

(16.37)

Combining Equations (16.37) and (16.25), we then have

$$v_I = V_{IL} = V_{TND} + \frac{(-V_{TNL})}{\sqrt{\left(\frac{K_D}{K_L}\right)\left(1 + \frac{K_D}{K_L}\right)}}$$

(16.38)

The point  $V_{IH}$  occurs when the load is biased in the saturation region and the driver is biased in the nonsaturation region. The relationship between the input and output voltages is given by Equation (16.29(b)). Taking the derivative with respect to  $v_I$ , we find

$$\frac{K_D}{K_L} \left[ 2(v_I - V_{TND}) \frac{dv_O}{dv_I} + 2v_O - 2v_O \frac{dv_O}{dv_I} \right] = 0$$

(16.39)

Setting the derivative equal to -1 and solving for  $v_0$  yields

$$v_O = V_{OLU} = \frac{(v_I - V_{TND})}{2} \tag{16.40}$$

Combining Equations (16.40) and (16.29(b)), we then have

$$v_I = V_{IH} = V_{TND} + \frac{2(-V_{TNL})}{\sqrt{3\left(\frac{K_D}{K_L}\right)}}$$

(16.41)

The noise margins are then determined from Equations (16.31(a)) and (16.31(b)). The calculation of noise margins in an inverter with depletion load is considered in Exercise 16.7.

#### **Test Your Understanding**

**16.7** For the transistors in the NMOS inverter with depletion load, the parameters are:  $V_{TND} = 1 \text{ V}$ ,  $V_{TNL} = -1.7 \text{ V}$ , and  $K_B/K_L = 5$ . Let  $V_{DD} = 5 \text{ V}$ . Determine  $V_{IL}$ ,  $V_{IH}$ , NM<sub>L</sub> and NM<sub>B</sub>. (Ans.  $V_{IL} = 1.31 \text{ V}$ ,  $V_{IH} = 1.88 \text{ V}$ , NM<sub>L</sub> = 0.87 V, NM<sub>H</sub> = 2.97 V)

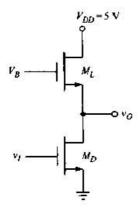

# 16.1.4 Body Effect

Up to this point, we have neglected the body effect and assumed that all threshold voltages are constant. Figure 16.17 shows enhancement-load and depletion-load NMOS inverters with the substrates of all transistors tied to ground. A nonzero source-to-body voltage will then exist in the load devices. In fact, the source terminal of the depletion load can increase to  $V_{DD}$ . The threshold voltage given by Equation (16.1) must be used in the circuit calculations for the load transistor. This significantly complicates the equations for the voltage transfer calculations, making them very cumbersome for hand analyses.

Figure 16.17 NMOS inverters, showing substrate connections to ground potential: (a) enhancement-load inverter and (b) depletion-load inverter

**Example 16.6 Objective:** Determine the change in the high output voltage of an NMOS inverter with enhancement load, taking the body effect into account.

Consider the NMOS inverter with enhancement load in Figure 16.17(a). The transistor parameters are  $V_{TNDO} = V_{TNLO} = 0.8 \text{ V}$  and  $K_D/K_L = 16$ . Assume the inverter is biased at  $V_{DD} = 5 \text{ V}$ , assume the body effect coefficient is  $\gamma = 0.90 \text{ V}^{1/2}$ , and let  $\phi_{fp} = 0.365 \text{ V}$ .

**Solution:** When  $v_I < V_{TNDO}$ , the driver is cut off and the output goes high. From Equation (16.16(b)), the maximum output voltage is

$$v_{O,\text{max}} = V_{OH} = V_{DD} - V_{TNL}$$

where  $V_{TNL}$  is, from Equation (16.1),

$$V_{TNL} = V_{TNLO} + \gamma \left[ \sqrt{2\phi_{fp} + V_{SB}} - \sqrt{2\phi_{fp}} \right]$$

From Figure 16.17(a), we see that  $V_{SB} = v_O$ ; therefore, Equation (16.16(b)) can be written

$$v_{O,\max} = V_{DD} - \left\{ V_{TNLO} + \gamma \left[ \sqrt{2\phi_{fp} + v_{O,\max}} - \sqrt{2\phi_{fp}} \right] \right\}$$

Defining  $v_{O,max} \equiv V_{OH}$ , we have

$$V_{OB} - 4.97 = -0.90\sqrt{0.73 + V_{OH}}$$

Squaring both sides and rearranging terms yields

$$V_{OH}^2 - 9.29V_{OH} + 24.9 = 0$$

Consequently, the maximum output voltage, or the logic 1 level, is

$$V_{OH} = 3.19 \, \text{V}$$

Comment: Neglecting the body effect, the logic I output level is

$$V_{OH} = V_{DD} - V_{TNL} = 5 - 0.8 = 4.2 \text{ V}$$

The body effect, then, can significantly influence the logic high state of the NMOS inverter with enhancement load. These results also impact the inverter noise margins.

The source and body terminals of the depletion load device in the NMOS inverter shown in Figure 16.17(b) are not at the same potential when the output goes high. However, when the driver is cut off, the drain-to-source voltage of the depletion device must be zero in order that  $v_{O,\max} = V_{OB} = V_{DD}$ .

**Computer Simulation:** A computer analysis of the inverters in Figure 16.17 was performed, neglecting the body effect and taking the body effect into account. The threshold voltage of the depletion load device is  $V_{TNLO} = -2 \text{ V}$  and the ratio  $K_D/K_L$  of the depletion load inverter is 4.82.

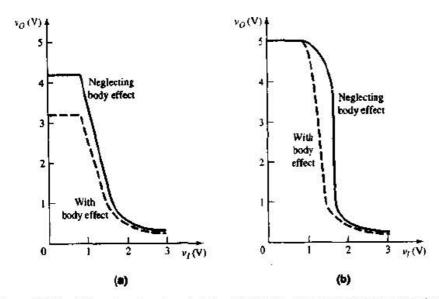

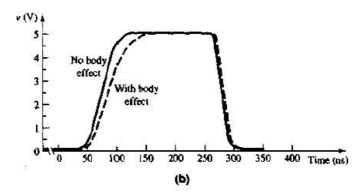

The body effect changes the voltage transfer characteristics of both the enhancement load and depletion load inverters. Figure 16.18(a) shows the voltage transfer characteristics for the enhancement-load inverter. The circuit and transistor parameters are the same as given in this example. For  $v_I = 0$ , the output voltage is 3.15V when the

Figure 18.18 Voltage transfer characteristics of NMOS inverters with and without the body effect (a) enhancement load and (b) depletion load

body effect is taken into account. This compares favorably with the 3.19 V from the hand analysis.

Figure 16.18(b) shows the voltage transfer characteristics for the depletion-load inverter. As discussed, the output voltage is 5V in the high state, which is independent of the body effect. However, the characteristics during the transition region are a function of the body effect.

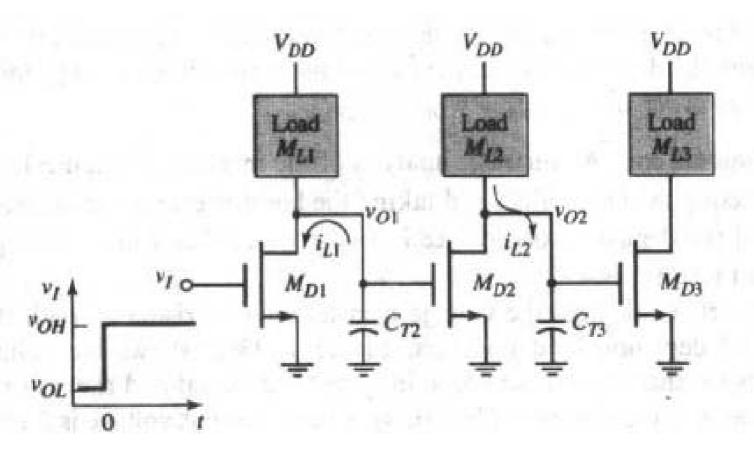

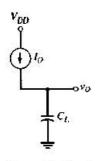

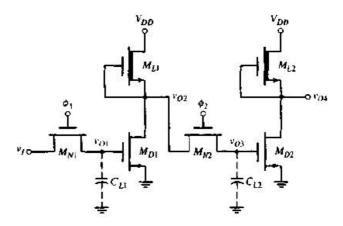

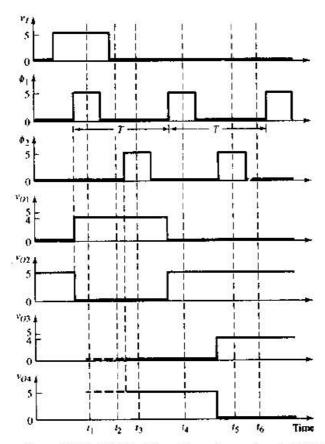

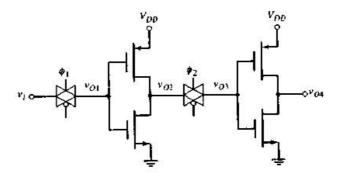

# 16.1.5 Transient Analysis of NMOS Inverters

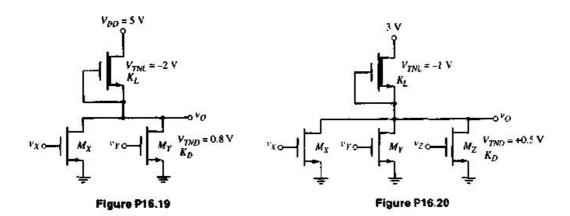

Figure 16.19 shows three NMOS inverters in cascade with generalized load devices. The output of the first inverter sees an effective capacitance looking into the gate of  $M_{D2}$ , and the output of the second inverter sees an effective capacitance looking into the gate of  $M_{D3}$ . The capacitances are  $C_{T2}$  and  $C_{T3}$ , respectively, and they include the transistor input capacitances, as well as any parasitic capacitances due to the interconnect lines between the inverter stages.

Figure 16.19 Three generalized NMOS inverters in cascade, for calculating transient effects

If input  $v_I$  is switched from high to low at time t=0, driver  $M_{D1}$  cuts off, and output  $v_{O1}$  begins to go high. The effective load capacitance  $C_{T2}$  must then be charged by a current through load device  $M_{L1}$ . As  $v_{O1}$  increases,  $M_{D2}$  turns on and  $v_{O2}$  begins to go low. For  $v_{O2}$  to go low, the effective load capacitance  $C_{T3}$  must discharge. The discharge current  $i_{L2}$  is the difference between the driver current in  $M_{D2}$  and the load current in  $M_{L2}$ .

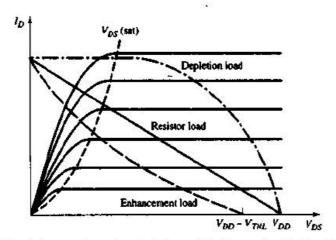

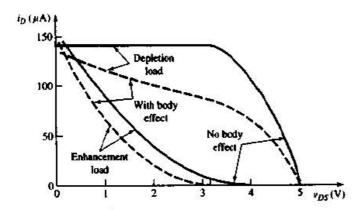

The rate at which capacitance  $C_{T2}$  charges is a function of the current-voltage characteristics of the load device. Figure 16.20 shows the characteristics of the driver transistor  $M_{D1}$ , with superimposed load curves for the three basic load components. These load curves neglect the body effect.

The load devices are assumed to be scaled such that  $I_{D,\max}$  is the same for each device. The constant current over a wide range of  $v_{DS}$  provided by the depletion load implies that this type of inverter will switch a capacitive load more rapidly than the other two types of inverter configurations. The rate at which the voltage across a load capacitance changes is a direct function of the current through the capacitance.

Figure 16.20 Driver transistor characteristics and load curves for the three types of NMOS inverters

Figure 16.21 shows the enhancement- and depletion-load inverter load curves that take the body effect into account. For the enhancement-load inverter, the resulting high output voltage is less than that when the body effect is neglected, as previously determined. Also, the current in the inverter is less over the entire voltage range, which implies that the switching times will be longer. For the depletion-load inverter, the resulting current is not a constant over a wide voltage range, and it is less than that when the body effect is neglected. Therefore, the time required to charge the load capacitance is longer.

Figure 16.21 Load curves, enhancement-load and depletion-load NMOS inverters, with and without body effect

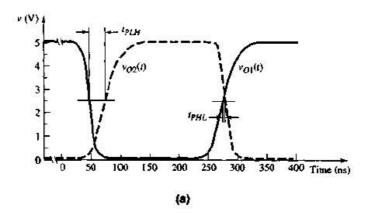

Figure 16.22 shows the switching characteristics of NMOS inverters with depletion-loads as determined from a PSpice analysis. A series of inverters, such as shown in Figure 16.19, was used. The width-to-length ratio of the load devices was  $(W/L)_L = 1$  and that of the driver transistors was  $(W/L)_D = 4$ . The effective load capacitances were assumed to be 0.5 pF, which is larger than would normally be encountered in an IC.

Figure 16.22(a) shows the input  $(v_{O1})$  and output  $(v_{O2})$  voltage characteristics when the body effect is neglected. The fall time is relatively short, since the load capacitance discharges through the larger driver transistor. The rise

Figure 16.22 (a) Switching characteristics of an NMOS inverter with depletion load and (b) switching characteristics with and without body effect

time is longer, since the load capacitance is charged by the current through the smaller load transistor. The propagation delay times are shown in the figure.

The rise and fall times of the inverter with and without the body effect are shown in Figure 16.22(b). The rise time is longer when the body effect is taken into account, since the current in the load device is smaller. This was shown by the load curve in Figure 16.21. The fall time is not affected by the body effect, since the substrate of the driver is connected to the source terminal, which is at ground potential.

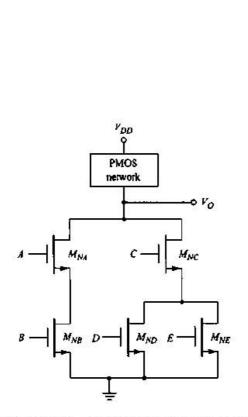

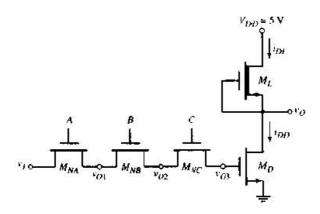

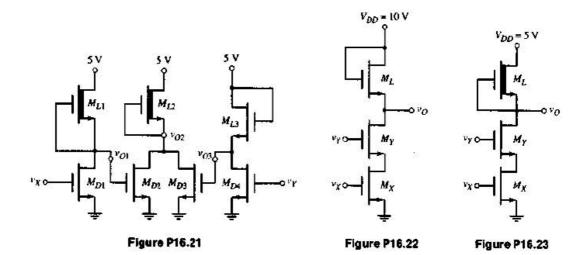

# 16.2 NMOS LOGIC CIRCUITS

NMOS logic circuits are formed by combining driver transistors in parallel, series, or series-parallel combinations to produce a desired output logic function.

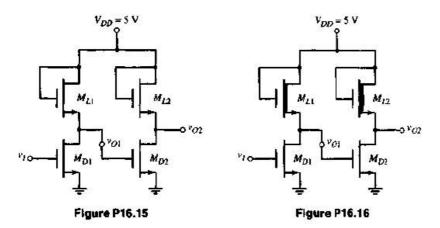

# 16.2.1 NMOS NOR and NAND Gates

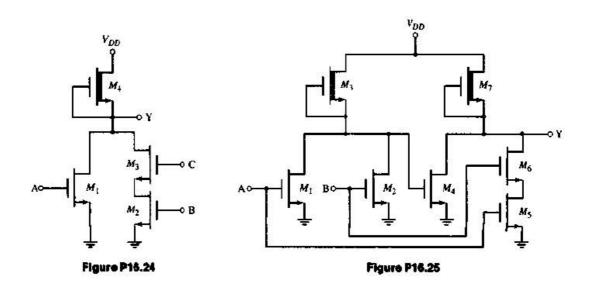

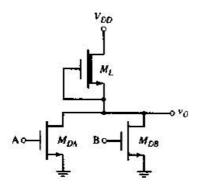

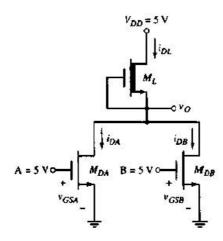

The NMOS NOR logic gate contains additional driver transistors connected in parallel. Figure 16.23 shows a two-input NMOS NOR logic gate with a depletion load. If A = B = logic 0, then both  $M_{DA}$  and  $M_{DB}$  are cut off and  $v_O = V_{DD}$ . If A = logic 1 and B = logic 0, then  $M_{DB}$  is cut off and the NMOS inverter configuration with  $M_L$  and  $M_{DA}$  is the same as previously considered,

Figure 16.23 Two-input NMOS NOR logic gate with depletion load

and the output voltage goes low. Similarly, if  $A = \log 0$  and  $B = \log 1$ , we again have the same inverter configuration.

If A = B = logic 1, then both  $M_{DA}$  and  $M_{DB}$  turn on and the two driver transistors are effectively in parallel. The value of the output voltage now changes slightly. Figure 16.24 shows the NOR gate when both input voltages are a logic 1. From our previous analysis, we can assume that the two driver transistors are biased in the nonsaturation region and the load device is biased in the saturation region. We then have

$$i_{DL} = i_{DA} + i_{DB}$$

Figure 16.24 Two-input NMOS NOR logic gate for Example 16.7

which in general terms can be written

$$K_{L}[v_{GSL} - V_{TNL}]^{2} = K_{DA}[2(v_{GSA} - V_{TNA})v_{DSA} - v_{DSA}^{2}] + K_{DB}[2(v_{GSB} - V_{TNB})v_{DSB} - v_{DSB}^{2}]$$

(16.42)

If we assume the two driver transistors are identical, then the driver conduction parameters and threshold voltages are also identical, or  $K_{DA} = K_{DB} = K_D$  and  $V_{TNA} = V_{TNB} \equiv V_{TND}$ . Noting that  $v_{GSL} = 0$ ,  $v_{GSA} = v_{GSB} = V_{DB}$ , and  $v_{DSA} = v_{DSB} = v_0$ , we can write Equation (16.42) as

$$[-V_{TNL}]^2 = 2\left(\frac{K_D}{K_L}\right)[2(V_{DD} - V_{TND})v_O - v_O^2]$$

(16.43)

Equation (16.43) shows that when both drivers are conducting, the effective width-to-length ratio of the composite driver transistor doubles. This means that the output voltage becomes slightly smaller when both inputs are high.

**Example 16.7** Objective: Determine the low output voltage of an NMOS NOR circuit.

Consider the NOR circuit in Figure 16.24 biased at  $V_{DD}=5\,\mathrm{V}$ . Assume that  $k_A'=35\,\mu\mathrm{A/V}^2$ . Also assume the width-to-length ratios of the load and driver transistors are  $(W/L)_L=1$  and  $(W/L)_D=4$ , respectively. Let  $V_{TND}=0.8\,\mathrm{V}$  and  $V_{TNL}=-2\,\mathrm{V}$ . Neglect the body effect.

**Solution:** If, for example, A = logic 1 = 5 V and B = logic 0, then  $M_{DB}$  is cut off. The output voltage is determined from Equation (16.29(b)), which is

$$\frac{K_D}{K_L} [2(v_I - V_{TND})v_O - v_O^2] = (-V_{TNL})^2$$

or

$$\binom{4}{1} [2(5-0.8)\nu_O - \nu_O^2] = (2)^2$$

The output voltage is found to be

$$v_0 = 0.121 \text{ V}$$

If both inputs go high, then

$$A = B = V_{DD} = 5 \,\mathrm{V}$$

and the output voltage can be found using Equation (16.43), which is

$$[-V_{TNL}]^{2} = 2\left(\frac{K_{D}}{K_{L}}\right)\left[2(V_{DD} - V_{TND})v_{O} - v_{O}^{2}\right]$$

or

$$(2)^2 = 2\left(\frac{4}{1}\right) \left[2(5-0.8)v_O - v_O^2\right]$$

The output voltage is found to be

$$\nu_{\mathcal{O}} = 0.060\,\mathrm{V}$$

**Comment:** An NMOS NOR gate must be designed to achieve a specified  $V_{OL}$  output voltage when only one input is high. This will give the largest logic 0 value. When more than one input is high, the output voltage is smaller than the specified  $V_{OL}$  value, since the effective width-to-length ratio of the composite driver transistor increases.

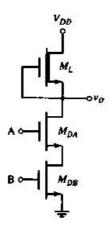

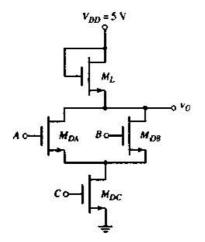

The NMOS NAND logic gate contains additional driver transistors connected in series. Figure 16.25 shows a two-input NMOS NAND logic gate with a depletion load. If both  $A = B = \log c \, 0$ , or if either A or B is a logic 0, at least

Figure 16.25 Two-input NMOS NAND logic gate with depletion load

one driver is cut off, and the output is high. If both A = B = logic 1, then the composite driver of the NMOS inverter conducts and the output goes low.

Since the gate-to-source voltages of  $M_{DA}$  and  $M_{DB}$  are not equal, determining the actual voltage  $V_{OL}$  of a NAND gate is difficult. The drain-to-source voltages of  $M_{DA}$  and  $M_{DB}$  must adjust themselves to produce the same current. In addition, if the body effect is also included, the analysis becomes even more difficult. Since the two driver transistors are in series, a good approximation assumes that the width-to-length ratio of the drivers must be twice that of a single driver in an NMOS inverter to achieve a given  $V_{OL}$  value.

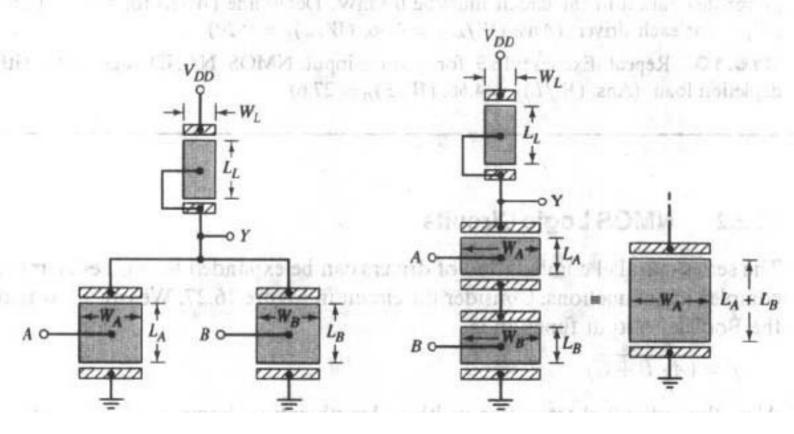

The composite width-to-length ratios of the driver transistors in the two-input NMOS NOR and NAND gates are shown schematically in Figure 16.26. For the NOR gate, the effective width doubles; for the NAND gates, the effective length doubles.

Example 16.8 Objective: Determine the low output voltage of an NMOS NAND circuit.

Consider the NAND circuit in Figure 16.25 biased at  $V_{DD} = 5 \text{ V}$ . Assume  $k_n' = 35 \mu\text{A/V}^2$ . Also assume the width-to-length ratio of the load transistor is  $(W/L)_L = 1$ . Let  $V_{TND} = 0.8 \text{ V}$  and  $V_{TNL} = -2 \text{ V}$ . Neglect the body effect.

**Solution:** From a PSpice analysis for A = B = logic 1 = 5 V, the output voltage is 0.060 V when the width-to-length ratio of each driver transistor is  $(W/L)_D = 16$ .

This result correlates very well with the results of Example 16.7. For the two-input NOR gate, the effective width of the composite driver doubles, or  $(W/L)_C = 2 \times 4 = 8$ , which results in an output voltage of 0.060 V. For the two input NAND gate, the effective length of the composite driver doubles, or  $(W/L)_C = (1/2) \times 16 = 8$ , which also results in an output voltage of 0.060 V.

Comment: If an N-input NMOS NAND logic gate were to be fabricated, then the width-to-length ratio of the drivers would need to be N times that of a single driver in an NMOS inverter to achieve a given value of  $V_{OL}$ . The increase in the required area of the driver transistors in a NAND logic gate means that logic gates with more than three or four inputs are not attractive.

# **Test Your Understanding**

[Note: In the following exercises, assume  $k'_n = 35 \,\mu\text{A/V}^2$  for all NMOS transistors.]

\*16.8 Consider the two-input NMOS NOR logic gate shown in Figure 16.23 biased at  $V_{DD}=10\,\mathrm{V}$ . Let  $(W/L)_L=2$ ,  $(W/L)_B=10$ ,  $V_{TND}\simeq 1.5\,\mathrm{V}$ , and  $V_{TNL}=-3\,\mathrm{V}$ . Neglect the body effect. (a) Determine  $V_{OL}$  when: (i)  $A=\log ic$  1,  $B=\log ic$  0, and (ii)  $A=B=\log ic$  1. (b) Calculate the power dissipation in the circuit when: (i)  $A=\log ic$  1,  $B=\log ic$  0, and (ii)  $A=B=\log ic$  1. (Ans. (a)  $V_{OL}=0.107\,\mathrm{V}$ ,  $V_{OL}=0.0531\,\mathrm{V}$  (b)  $P=3.15\,\mathrm{mW}$ )

**D16.9** Design a three-input NMOS NOR logic gate with depletion load such that  $V_{OL}(\max) = 0.12 \text{ V}$ . Let  $V_{DD} = 5 \text{ V}$ ,  $V_{TND} = 0.8 \text{ V}$ , and  $V_{TNL} = -1.4 \text{ V}$ . The maximum power dissipation in the circuit must be 0.8 mW. Determine (W/L) for the load and (W/L) for each driver. (Ans.  $(W/L)_L = 4.66$ ,  $(W/L)_D = 9.20$ )

**D16.10** Repeat Exercise 16.9 for a three-input NMOS NAND logic gate with depletion load. (Ans.  $(W/L)_L = 4.66$ ,  $(W/L)_D = 27.6$ )

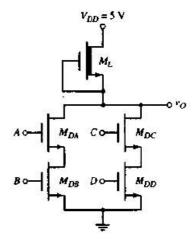

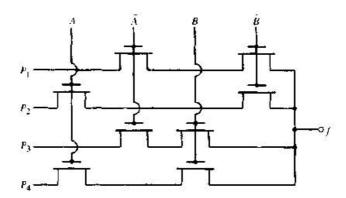

# 16.2.2 NMOS Logic Circuits

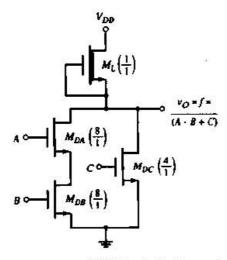

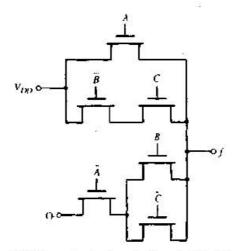

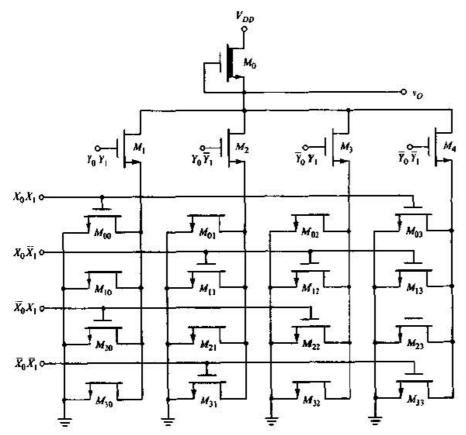

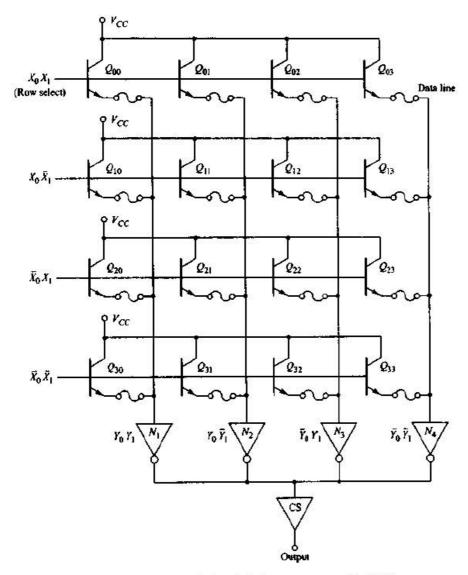

The series—parallel combination of drivers can be expanded to synthesize more complex logic functions. Consider the circuit in Figure 16.27. We can show that the Boolean output function is

$$f = \overline{(A \cdot B + C)}$$

Also, the individual transistor width-to-length ratios shown produce an effective  $K_D/K_L$  ratio of 4 for an effective single inverter when only  $M_{DA}$  and  $M_{DB}$  are conducting, or only  $M_{DC}$  is conducting. The actual complexity of the Boolean function is limited since the required width-to-length ratios of individual transistors may become unreasonably large.

Figure 18.27 NMOS logic circuit example

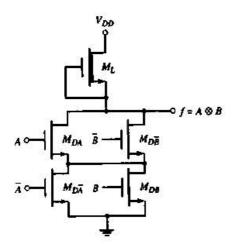

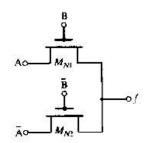

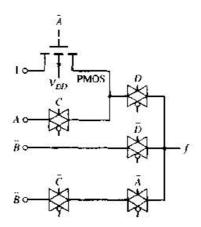

Two additional logic functions are the exclusive-OR and exclusive-NOR. Figure 16.28 shows a circuit configuration that produces the exclusive-OR function. If A = B = logic 1, a path exists from the output to ground through drivers  $M_{DA}$  and  $M_{DB}$ , and the output goes low. Similarly, if A = B = logic 0, which means that  $\tilde{A} = \tilde{B} = \text{logic 1}$ , a path exists from the output to ground through the drivers  $M_{DB}$  and  $M_{DA}$ , and the output gain goes low. For all other input logic signal combinations, the output is isolated from ground so the output goes high.

Figure 16.28 NMOS exclusive-OR logic

Figure 18.29 Logic circuit driving N load circuits

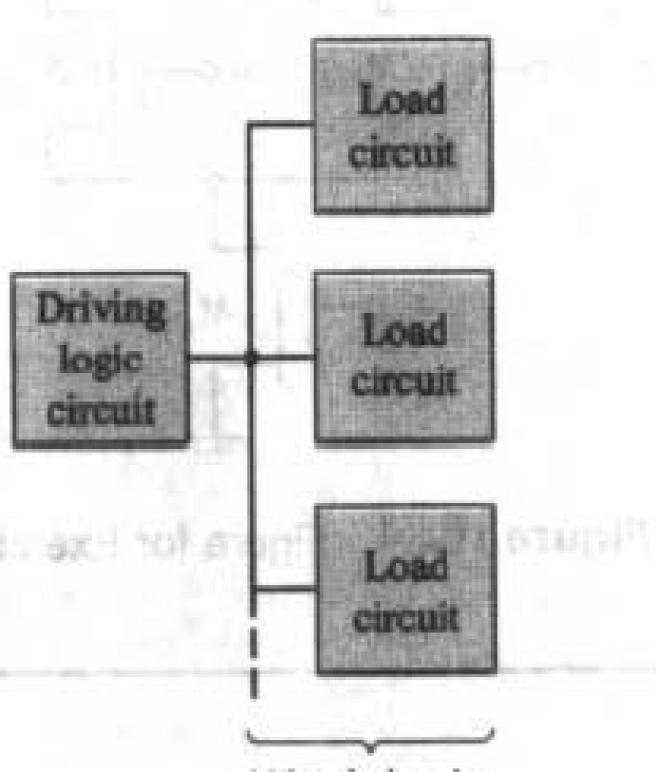

# 16.2.3 Fanout

An NMOS inverter or NMOS logic gate must be capable of driving more than one load, as shown in Figure 16.29. It is assumed that each load is identical to the driver logic circuit. The number of identical-load circuits connected to the output of a driver logic circuit is defined as the famout. For MOS logic circuits,

N load circuits

the inputs to the load circuits are the oxide-insulated gates of the MOS transistors; therefore, the static loading caused by multiple driver loads is so small that the dc transfer curve is essentially identical to a no-load condition. The dc characteristics of MOS logic circuits are unaffected by the fanout to other MOS logic inputs. However, the load capacitance due to a large fanout seriously degrades the switching speed and propagation delay times. Consequently, maintaining the propagation delay time below a specified maximum value determines the fanout of MOS digital circuits.

# **Test Your Understanding**

[Assume  $k'_n = 35 \,\mu\text{A/V}^2$ .]

**\*16.11** Consider the NMOS logic circuit in Figure 16.30. Let  $V_{TN} = 0.7 \, \text{V}$  for each transistor and assume all driver transistors are identical. (a) If  $(W/L)_L = 0.5$ , determine (W/L) for the drivers such that  $V_{OL}(\text{max}) = 0.15 \, \text{V}$ . (b) Determine the maximum power dissipation in the logic circuit. (Ans. (a)  $(W/L)_D = 13.6$  (b)  $P = 753 \, \mu\text{W}$ )

**16.12** Repeat Exercise 16.11 for the NMOS logic circuit in Figure 16.31, except assume that the threshold voltage of the load device is  $V_{TN} = -1.2 \,\text{V}$ . (Ans. (a)  $(W/L)_D = 1.14$  (b)  $P = 63 \,\mu\text{W}$ )

Figure 16.31 Figure for Exercise 16.12

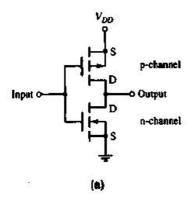

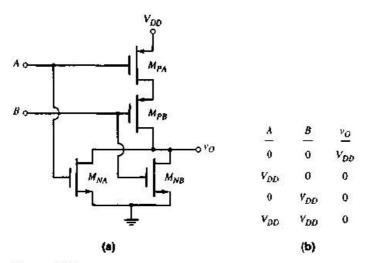

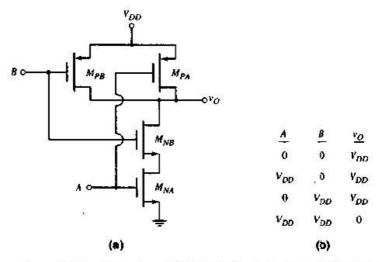

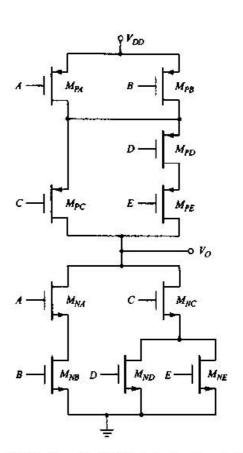

### 16.3 CMOS INVERTER

Complementary MOS, or CMOS, circuits contain both n-channel and p-channel MOSFETs. As we will see, the power dissipation in CMOS logic circuits is much smaller than in NMOS circuits, which makes CMOS very attractive. We briefly review the characteristics of p-channel transistors, and will then analyze the CMOS inverter, which is the basis of most CMOS logic circuits. We will examine the CMOS NOR and NAND gates and other basic CMOS logic circuits, covering power dissipation, noise margin, fanout, and switching characteristics.

# 16.3.1 p-Channel MOSFET Revisited

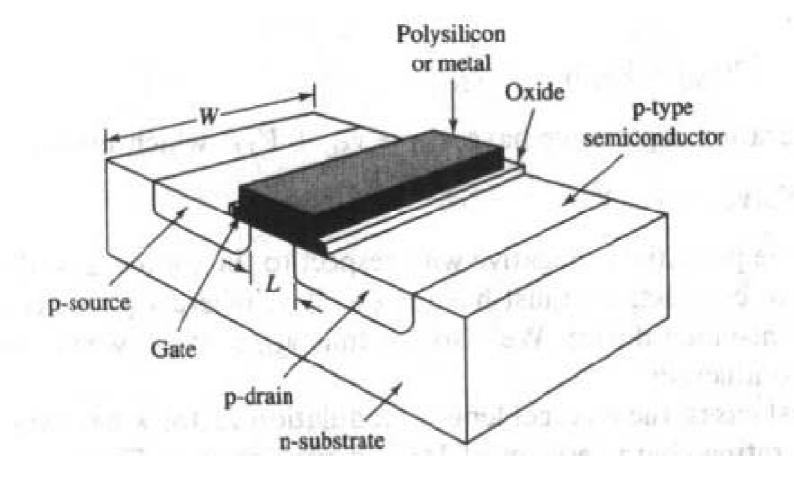

Figure 16.32 shows a simplified view of a p-channel MOSFET. The p- and n-regions are reversed from those in an n-channel device. Again, the channel length is L and the channel width is W. Usually in any given fabrication process, the channel length is the same for all devices, so the channel width W is the variable in logic circuit design.

Figure 16.32 Simplified cross section of p-channel MOSFET

Figure 16.33(a) shows the simplified circuit symbol for the p-channel enhancement-mode device. When the body or substrate connection is needed, we will use the symbol shown in Figure 16.33(b). Usually, the p-channel depletion-mode device is not used in CMOS digital circuits; therefore, it is not addressed here.

Figure 16.33 (a) Simplified circuit symbol, p-channel enhancement-mode MOSFET and (b) circuit symbol showing substrate connection

Normally, in an integrated circuit, more than one p-channel device will be fabricated in the same n-substrate so the p-channel transistors will exhibit a body effect. The n-substrate is connected to the most positive potential. The source terminal may be negative with respect to the substrate; therefore, voltage  $V_{BS}$  may exist between the body and the source. The threshold voltage is

$$V_{TP} = V_{TPO} - \frac{\sqrt{2e\varepsilon_s N_d}}{C_{ox}} \left[ \sqrt{2\phi_{fn} + V_{BS}} - \sqrt{2\phi_{fn}} \right]$$

$$= V_{TPO} - \gamma \left[ \sqrt{2\phi_{fn} + V_{BS}} - \sqrt{2\phi_{fn}} \right]$$

(16.44)

where  $V_{TPO}$  is the threshold voltage for zero body-to-source voltage, or  $V_{BS} = 0$ . The parameter  $N_d$  is the n-substrate doping concentration and  $\phi_{fh}$  is a potential related to the substrate doping. The parameter  $\gamma$  is the body effect coefficient.

The current-voltage characteristic of the p-channel MOSFET are functions of both the electrical and geometric properties of the device. When the transistor is biased in the nonsaturation region, we have  $v_{SD} \leq v_{SG} + V_{TP}$ . Therefore,

$$i_D = K_P [2(v_{SG} + V_{TP})v_{SD} - v_{SD}^2]$$

(16.45(a))

In the saturation region, we have  $v_{SD} \ge v_{SG} + V_{TP}$ , which means that

$$i_D = K_P (v_{SG} + V_{TP})^2 ag{16.45(b)}$$

The gate potential is negative with respect to the source. For the p-channel transistor to conduct, we must have  $v_{GS} < V_{TP}$ , where  $V_{TP}$  is negative for an enhancement-mode device. We also see that  $v_{SG} > |V_{TP}|$  when the p-channel device is conducting.

In most cases, the channel length modulation factor  $\lambda$  has very little effect on the operating characteristics of MOS digital circuits. Therefore, the term  $\lambda$  is assumed to be zero unless otherwise stated.

The transition point, which separates the nonsaturation and saturation bias regions, is given by

$$v_{SD} = v_{SD}(\text{sat}) = v_{SG} + V_{TP}$$

(16.46)

The parameter  $K_P$  is the conduction parameter and is given by

$$K_P = \left(\frac{1}{2}\mu_p C_{ox}\right) \left(\frac{W}{L}\right) = \frac{k_p'}{2} \frac{W}{L}$$

(16.47)

As before, the hole mobility  $\mu_p$  and oxide capacitance  $C_{ox}$  are assumed to be constant for all devices. The hole mobility in p-channel silicon MOSFETs is approximately one-half the electron mobility  $\mu_n$  in n-channel silicon MOSFETs. This means that a p-channel device width must be approximately twice as large as that of an n-channel device in order that the two devices be electrically equivalent (that is, that they have the same conduction parameter values).

## Small Geometry Effects

The same small geometry effects apply to the p-channel devices as we discussed for the n-channel devices in Section 16.1.1. As with the NMOS inverters and logic circuits, we can use Equations (16.45(a)), (16.45(b)), and (16.46) as first-order equations in the design of NMOS logic circuits. The basic operation and behavior of CMOS logic circuits can be predicted using these first-order equations.

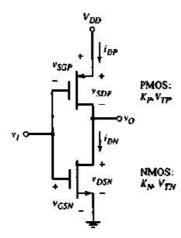

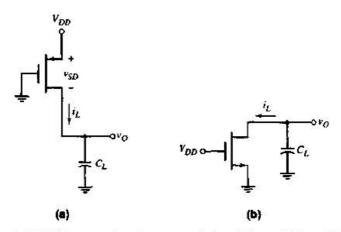

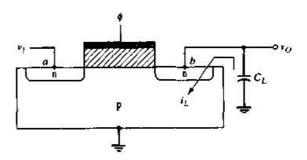

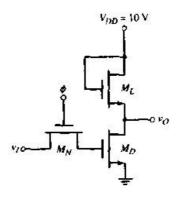

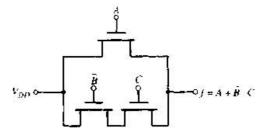

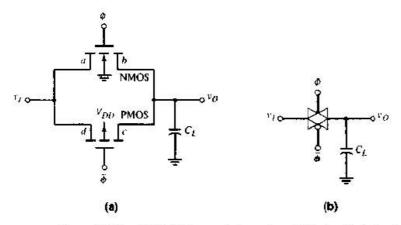

## 16.3.2 DC Analysis of the CMOS Inverter

The CMOS inverter, shown in Figure 16.34, is a series combination of a pchannel and an n-channel MOSFET. The gates of the two MOSFETs are connected together to form the input and the two drains are connected together

Figure 16.34 CMOS inverter

to form the output. Both transistors are enhancement-mode devices. The parameters of the NMOS are denoted by  $K_N$  and  $V_{TN}$ , where  $V_{TN} > 0$ , and the parameters of the PMOS are denoted by  $K_P$  and  $V_{TP}$ , where  $V_{TP} < 0$ .

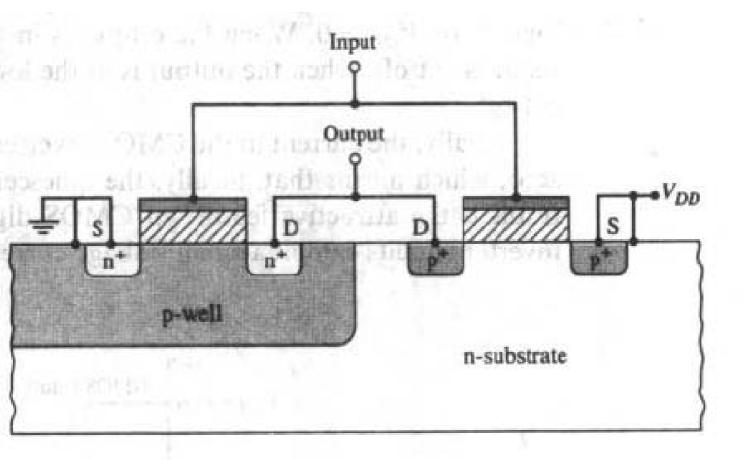

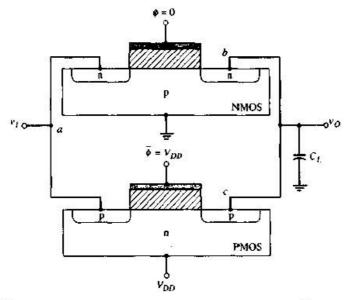

Figure 16.35 shows a simplified cross section of a CMOS inverter. In this process, a separate p-well region is formed within the starting n-substrate. The n-channel device is fabricated in the p-well region and the p-channel device is fabricated in the n-substrate. Although other approaches, such as an n-well in a p-substrate, are also used to fabricate CMOS circuits, the important point is that the processing is more complicated for CMOS circuits than for NMOS circuits. However, the advantages of CMOS digital logic circuits over NMOS circuits justify their use.

Figure 16.35 Simplified cross section, CMOS inverter

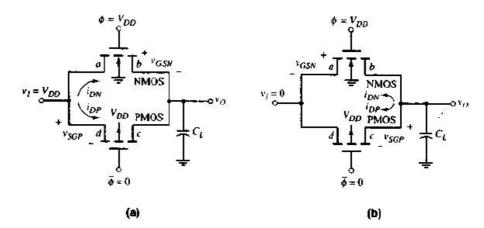

## Voltage Transfer Curve

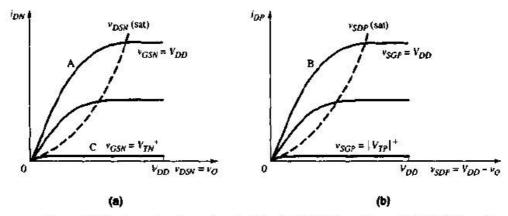

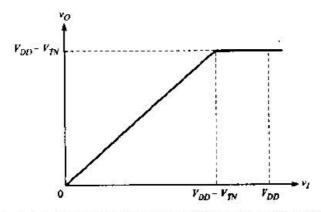

Figure 16.36 shows the transistor characteristics for both the n- and p-channel devices. We can determine the voltage transfer characteristics of the inverter by evaluating the various transistor bias regions. For  $v_i = 0$ , the NMOS device is cut off,  $i_{DN} = 0$ , and  $i_{DP} = 0$ . The PMOS source-to-gate voltage is  $V_{DD}$ , which

Figure 16.36 Current-voltage characteristics, (a) NMOS transistor and (b) PMOS transistor

means that the PMOS is biased on the curve marked B in Figure 16.36(b). Since the only point on the curve corresponding to  $i_{DP} = 0$  occurs at  $v_{SDP} = 0 = V_{DD} - v_O$ , the output voltage is  $v_O = V_{DD}$ . This condition exists as long as the NMOS transistor is cut off, or  $v_I \le V_{TN}$ .

For  $v_I = V_{DD}$ , the PMOS device is cut off,  $i_{DP} = 0$ , and  $i_{DN} = 0$ . The NMOS gate-to-source voltage is  $V_{DD}$  and the NMOS is biased on the curve marked A in Figure 16.36(a). The only point on the curve corresponding to  $i_{DN} = 0$  occurs at  $v_{DSN} = v_O = 0$ . The output voltage is zero as long as the PMOS transistor is cut off, or  $v_{SGP} = V_{DD} - v_I \le |V_{TP}|$ . This means that the input voltage is in the range  $V_{DD} - |V_{TP}| \le v_I \le V_{DD}$ .

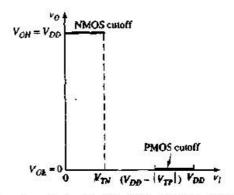

Figure 16.37 shows the voltage transfer characteristics generated thus far for the CMOS inverter. The more positive output voltage corresponds to a logic 1, or  $V_{OH} = V_{DD}$ , and the more negative output voltage corresponds to a logic 0, or  $V_{OL} = 0$ . When the output is in the logic 1 state, the NMOS transistor is cut off; when the output is in the logic 0 state, the PMOS transistor is cut off.

Ideally, the current in the CMOS inverter in either steady-state condition is zero, which means that, ideally, the quiescent power dissipation is zero. This result is the attractive feature of CMOS digital circuits. In actuality, CMOS inverter circuits exhibit a small leakage current in both steady-state conditions,

Figure 16.37 CMOS inverter output voltage for input voltage in either high state or low

due to the reverse-biased pn junctions. However, the power dissipation may be in the nanowatt range rather than in the milliwatt range of NMOS inverters. Without this feature, VLSI would not be possible.

When the input voltage is just greater than  $V_{TN}$ , or

$$v_I = v_{GSN} = V_{TN}^+$$

the NMOS begins to conduct and the Q-point falls on the curve marked C in Figure 16.36(a). The current is small and  $v_{DSN} \cong V_{DD}$ , which means that the NMOS is biased in the saturation region. The PMOS source-to-drain voltage is small, so the PMOS is biased in the nonsaturation region. Setting  $i_{DN} = i_{DP}$ , we can write

$$K_N[v_{GSN}, -V_{TN}]^2 = K_P[2(v_{SGP} + V_{TP})v_{SOP} - v_{SDP}^2]$$

(16.48)

Relating the gate-to-source and drain-to-source voltages in each transistor to the inverter input and output voltages, respectively, we can rewrite Equation (16.48) as follows:

$$K_N[v_I - V_{TN}]^2 = K_P[2(V_{DD} - v_I + V_{TP})(V_{DD} - v_O) - (V_{DD} - v_O)^2]$$

(16.49)

Equation (16.49) relates the input and output voltages as long as the NMOS is biased in the saturation region and the PMOS is biased in the nonsaturation region.

The transition point for the PMOS is defined from

$$v_{SOP}(\text{sat}) = v_{SOP} + V_{TP} \tag{16.50}$$

Using Figure 16.38, Equation (16.50) can be written

$$V_{DD} - V_{OPt} = V_{DD} - V_{IPt} + V_{TP}$$

(16.51(a))

or

$$V_{OP_1} = V_{IP_2} - V_{TP} ag{16.51(b)}$$

where  $V_{OP_I}$  and  $V_{IP_I}$  are the PMOS output and input voltages, respectively, at the transition point.

The transition point for the NMOS is defined from

$$v_{DSN}(\text{sat}) = v_{GSN} - V_{TN}$$

(16.52(a))

or

$$V_{ONt} = V_{INt} - V_{TN} (16.52(b))$$

where  $V_{ON}$  and  $V_{IN}$  are the NMOS output and input voltages, respectively, at the transition point.

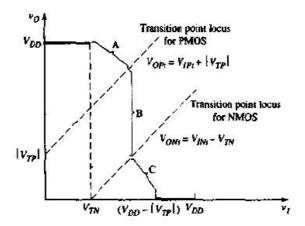

On the basis that  $V_{TP}$  is negative for an enhancement-mode PMOS, Equations (16.51(b)) and (16.52(b)) are plotted in Figure 16.38. We determine the input voltage at the transition points by setting the two drain currents equal to each other when both transistors are biased in the saturation region. The result is

$$K_N(v_{GSN} - \dot{V}_{TN})^2 = K_P(v_{SGP} + V_{TP})^2$$

(16.53)

Figure 16.36 Regions of the CMOS transfer characteristics indicating NMOS and PMOS transistor bias conditions. The NMOS device is biased in the saturation region in areas A and B and in the nonsaturation region in area C. The PMOS device is biased in the saturation region in areas B and C and in the nonsaturation region in area A.

With the gate-to-source voltages related to the input voltage, Equation (16.53) becomes

$$K_N(v_I - V_{TN})^2 = K_P(V_{DD} - v_I + V_{TP})^2$$

(16.54)

For this ideal case, the output voltage does not appear in Equation (16.54), and the input voltage is a constant, as long as the two transistors are biased in the saturation region.

Voltage  $v_I$  from Equation (16.54) is the input voltage at the PMOS and NMOS transition points. Solving for  $v_I$ , we find that

$$v_{I} = v_{It} = \frac{V_{DD} + V_{TP} + \sqrt{\frac{K_{N}}{K_{P}}} V_{TN}}{1 + \sqrt{\frac{K_{N}}{K_{P}}}}$$

(16.55)

For  $v_I > V_{II}$ , the NMOS is biased in the nonsaturation region and the PMOS is biased in the saturation region. Again equating the two drain currents, we have

$$K_N[2(v_{GSN} - V_{TN})v_{DSN} - v_{DSN}^2] = K_P(v_{SGP} + V_{TP})^2$$

(16.56)

Also, relating the gate-to-source and drain-to-source voltages to the input and output voltages, respectively, modifies Equation (16.56) as follows:

$$K_N[2(v_I - V_{TN})v_O - v_O^2] = K_P(V_{DD} - v_I + V_{TP})^2$$

(16.57)

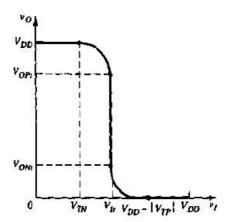

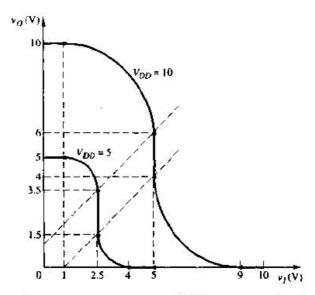

Equation (16.57) relates the input and output voltages as long as the NMOS is biased in the nonsaturation region and the PMOS in the saturation region. Figure 16.39 shows the complete voltage transfer curve.

Figure 16.39 Complete voltage transfer characteristics, CMOS inverter

**Example 16.9** Objective: Determine the critical voltages on the voltage transfer curve of a CMOS inverter.

Consider a CMOS inverter biased at  $V_{DD} = 5 \text{ V}$  with transistor parameters of  $K_N = K_P$  and  $V_{TN} = -V_{TP} = 1 \text{ V}$ . Then consider another CMOS inverter biased at  $V_{DD} = 10 \text{ V}$  with the same transistor parameters.

**Solution:** For  $V_{DD} = 5 \text{ V}$ , the input voltage at the transition points is, from Equation (16.55).

$$V_h = \frac{5 + (-1) + \sqrt{1} \cdot 1}{1 + \sqrt{1}} = 2.5 \text{ V}$$

The output voltage at the transition point for the PMOS is, from Equation (16.51(b)),

$$V_{OP} = V_{IP} - V_{TP} = 2.5 - (-1) = 3.5 \text{ V}$$

and the output voltage at the transition point for the NMOS is, from Equation (16.52(b)),

$$V_{ONt} = V_{INt} - V_{TN} = 2.5 - 1 = 1.5 \text{ V}$$

For  $V_{DD} = 10 \text{ V}$  and the same transistor parameters, the critical voltages are:

$$V_{II} = 5 \text{ V}$$

$V_{OPr} = 6 \text{ V}$   $V_{ONt} = 4 \text{ V}$

Comment: The two voltage transfer curves are shown in Figure 16.40. The figure depicts another advantage of CMOS technology, that is, CMOS circuits can be biased over a wide range of voltages.

## **Test Your Understanding**

**16.13** The CMOS inverter in Figure 16.34 is biased at  $V_{DD}=10\,\text{V}$ , and the transistor threshold voltages are  $V_{TN}=2\,\text{V}$  and  $V_{TP}=-2\,\text{V}$ . Sketch the voltage transfer curve and show the critical points, as in Figure 16.39, for: (a)  $K_N/K_P=1$ , (b)  $K_N/K_P=0.5$ , and (c)  $K_N/K_P=2$ . (Ans. (a)  $V_{II}=5\,\text{V}$ ,  $V_{OPI}=7\,\text{V}$ ,  $V_{OHI}=3\,\text{V}$  (b)  $V_{II}=5.51\,\text{V}$ ,  $V_{OPI}=7.51\,\text{V}$ ,  $V_{ONI}=3.51\,\text{V}$  (c)  $V_{II}=4.49\,\text{V}$ ,  $V_{OPI}=6.49\,\text{V}$ ,  $V_{ONI}=2.49\,\text{V}$ )

Figure 18.40 Voltage transfer characteristics, CMOS inverter biased at either  $V_{DD}=5\,\mathrm{V}$  or  $V_{DD}=10\,\mathrm{V}$

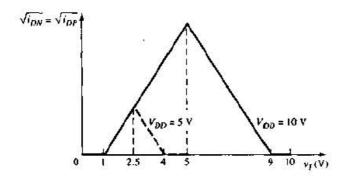

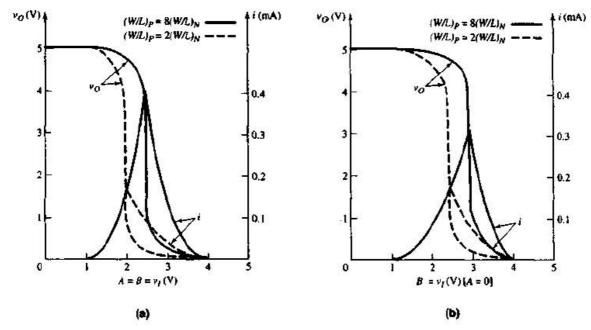

## **CMOS Inverter Currents**

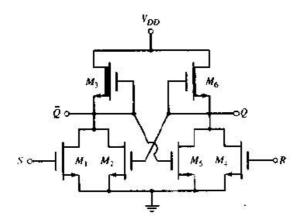

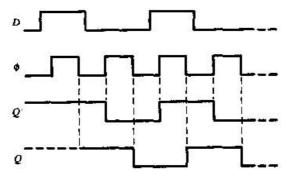

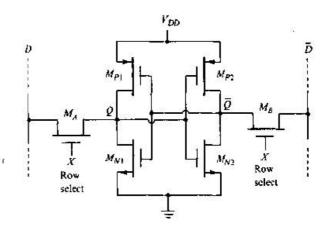

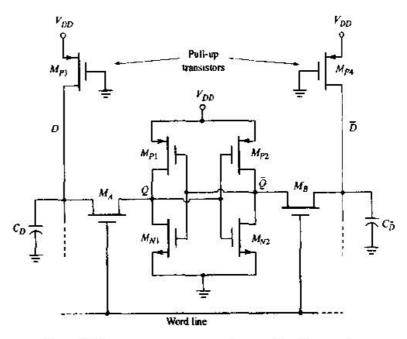

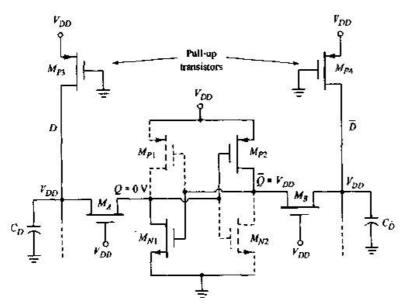

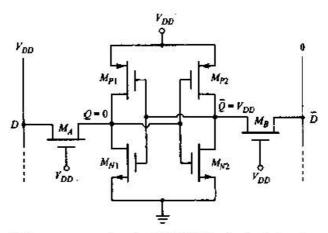

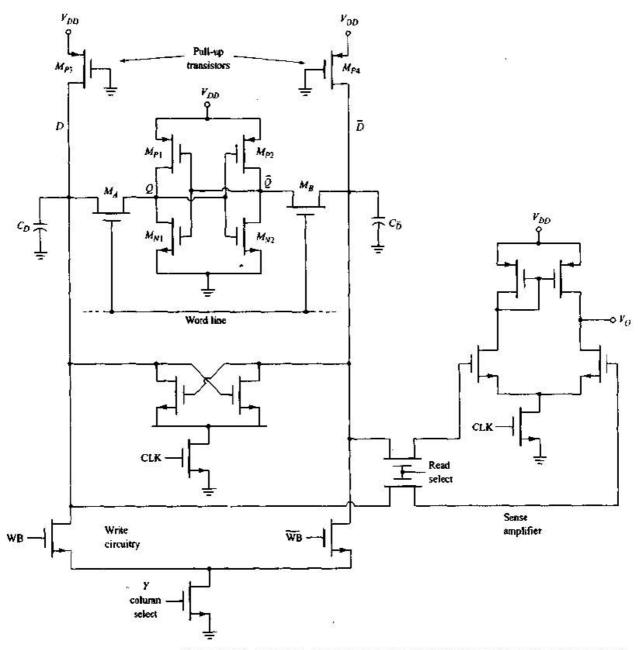

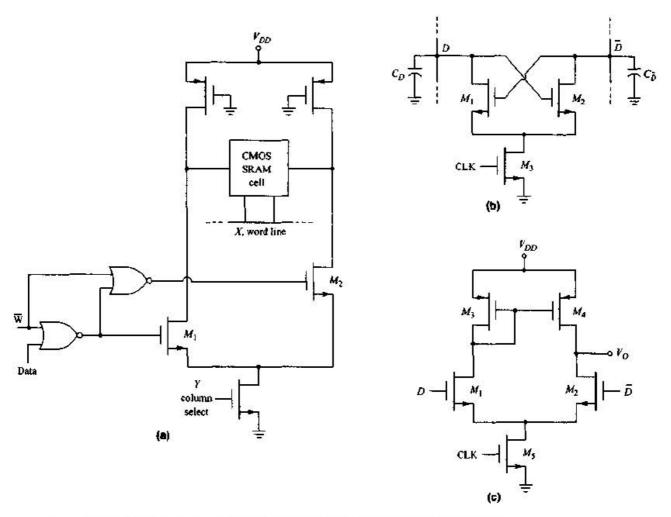

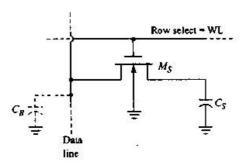

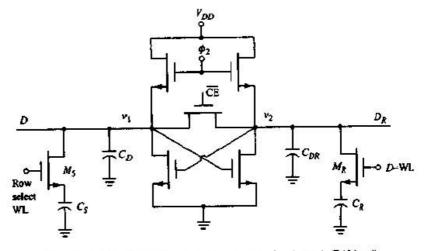

When the CMOS inverter input voltage is either a logic 0 or a logic 1, the current in the circuit is zero, since one of the transistors is cut off. When the input voltage is in the range  $V_{TN} < v_I < V_{DD} - |V_{TP}|$ , both transistors are conducting and a current exists in the inverter.