(a) Design an NMOS logic circuit with depletion load to perform this function. Signals A, B, and C are available. (b) Assume  $(W/L)_L = 1$ ,  $V_{DD} = 5 \, \text{V}$ ,  $V_{TNL} = -1.5 \, \text{V}$ , and  $V_{TND} = 0.8 \, \text{V}$ . Determine the W/L ratio of the other transistors such that the maximum logic 0 value in any part of the circuit is  $0.2 \, \text{V}$ .

D16.27 Design an NMOS logic circuit with a depletion load that will sound an alarm in an automobile if the ignition is turned off while the headlights are still on and/or the parking brake has not been set. Separate indicator lights are also to be included showing whether the headlights are on or the parking brake needs to be set. State any assumptions that are made.

#### Section 16.3 CMOS Inverter

**16.28** Consider the CMOS inverter in Figure 16.34. Let  $K_P = K_n$ ,  $V_{TN} = +0.8 \text{ V}$ ,  $V_{TP} = -0.8 \text{ V}$ , and  $V_{DD} = 5 \text{ V}$ . (a) Find the transition points for the p-channel and n-channel transistors. (b) Sketch the voltage transfer characteristic, including the appropriate voltage values at the transition points. (c) Find  $v_D$  for  $v_I = 2 \text{ V}$  and for  $v_I = 3 \text{ V}$ .

16.29 For the CMOS inverter in Figure 16.34, let  $V_{TN} = +0.4 \text{ V}$ ,  $V_{TP} = -0.4 \text{ V}$ ,  $k'_n = 80 \,\mu\text{a}/\text{V}^2$ ,  $k'_p = 40 \,\mu\text{A}/\text{V}^2$ , and  $V_{DD} = 3.3 \,\text{V}$ . (a) Let  $(W/L)_n = 2$  and  $(W/L)_p = 4$ . (i) Find the transition points for the p-channel and n-channel transistors. (ii) Sketch the voltage transfer characteristics including the appropriate voltage values at the transition points. (iii) Find  $v_I$  when  $v_O = 0.4 \,\text{V}$  and when  $v_O = 2.9 \,\text{V}$ . (b) For  $(W/L)_n = (W/L)_p = 2$ , repeat part (a).

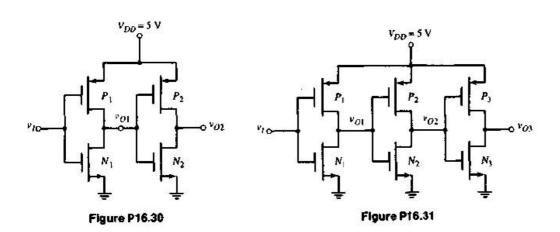

**16.30** Consider the CMOS inverter pair in Figure P16.30. Let  $V_{TN} = 0.8 \,\text{V}$ ,  $V_{TP} = -0.8 \,\text{V}$ , and  $K_n = K_p$ . (a) If  $v_{O1} = 0.6 \,\text{V}$ , determine  $v_I$  and  $v_{O2}$ . (b) Determine the range of  $v_{O2}$  for which both  $N_2$  and  $P_2$  are biased in the saturation region.

16.31 Consider the series of CMOS inverters in Figure P16.31. The threshold voltages of the n-channel transistors are  $V_{TN} = 0.8 \, \text{V}$ , and the threshold voltages of the p-channel transistors are  $V_{TP} = -0.8 \, \text{V}$ . The conduction parameters are all equal. (a) Determine the range of  $v_{O1}$  for which both  $N_1$  and  $P_1$  are biased in the saturation region. (b) If  $v_{O2} = 0.6 \, \text{V}$ , determine the values of  $v_{O3}$ ,  $v_{O1}$ , and  $v_{I}$ .

16.32 For the CMOS inverter in Figure 16.34, (a) calculate and plot the current through the transistors as a function of the input voltage for  $0 \le v_I \le 5 \text{ V}$ . Assume  $K_n = K_p = 0.1 \text{ mA/V}^2$ ,  $V_{TN} = 0.8 \text{ V}$ ,  $V_{TI} = -0.8 \text{ V}$ , and  $V_{DD} = 5 \text{ V}$ . (b) Repeat part (a) for  $V_{DD} = 15 \text{ V}$ .

**16.33** The transistor parameters in the CMOS inverter are:  $k_n' = 50 \,\mu\text{A}/\text{V}^2$ ,  $k_p' = 25 \,\mu\text{A}/\text{V}^2$ ,  $V_{TN} = 0.8 \,\text{V}$ , and  $V_{TP} = -0.8 \,\text{V}$ . (a) For  $(W/L)_n = 2$  and  $(W/L)_p = 4$ , determine the peak current in the inverter during a switching cycle for  $V_{DD} = 5 \,\text{V}$ . (b) Repeat part (a) for  $(W/L)_n = (W/L)_p = 2$ .

16.34 A load capacitor of 0.2 pF is connected to the output of a CMOS inverter. Determine the power dissipated in the CMOS inverter for a switching frequency of 10 MHz, for inverter parameters described in (a) Problem 16.32 and (b) Problem 16.33.

16.35 A CMOS digital logic circuit contains the equivalent of 2 million CMOS inverters and is biased at  $V_{DD} = 5 \text{ V}$ . (a) The equivalent load capacitance of each inverter is 0.4 pF and each inverter is switching at 150 MHz. Determine the total average power dissipated in the circuit. (b) If the switching frequency is doubled, but the total power dissipated is to remain the same and the load capacitance remains constant, determine the required bias voltage.

**16.36** Consider a CMOS inverter. (a) Show that when  $v_I \cong V_{DD}$ , the resistance of the NMOS device is approximately  $1/[k'_n(W/L)_n(V_{DD} - V_{TN})]$ , and when  $v_I \cong 0$ , the resistance of the PMOS device is approximately  $1/[k'_p(W/L)_p(V_{DD} + V_{TP})]$ . (b) Using the results of part (a), determine the maximum current that the NMOS device can sink such that the output voltage stays below 0.5 V, and determine the maximum current that the PMOS device can source such that the output voltage does not drop more than 0.5 V below  $V_{DD}$ .

16.37 Consider the CMOS inverter in Figure 16.34. Let  $K_p = K_n$ ,  $V_{TN} = +1.5 \,\text{V}$ ,  $V_{TP} = -1.5 \,\text{V}$ , and  $V_{DD} = 10 \,\text{V}$ . Determine the two values of  $v_I$  and the corresponding values of  $v_O$  for which  $(dv_O/dv_I) = -1$  on the voltage transfer characteristics. What are the noise margins?

**16.38** Repeat Problem 16.37 if the CMOS inverter transistor parameters are:  $V_{TN} = +1.5 \text{ V}$ ,  $V_{TP} = -1.5 \text{ V}$ ,  $K_n = 100 \,\mu\text{A/V}^2$ , and  $K_p = 50 \,\mu\text{A/V}^2$ . Let  $V_{DD} = 10 \,\text{V}$ .

## Section 16.4 CMOS Logic Circuits

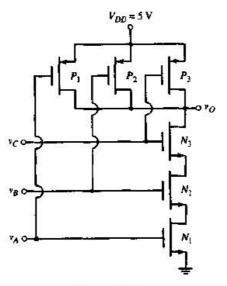

**16.39** Consider the three-input CMOS NAND circuit in Figure P16.39. Assume  $k'_n = 2k'_p$  and  $V_{TN} = |V_{TP}| = 0.8 \text{ V}$ . (a) If  $v_A = v_B = 5 \text{ V}$ , determine  $v_C$  such that both  $N_3$  and

Figure P16.38

$P_3$  are biased in the saturation region when  $(W/L)_p = 2(W/L)_n$ . (State any assumptions you make.) (b) If  $v_A = v_B = v_C = v_I$ , determine the relationship between  $(W/L)_p$  and  $(W/L)_q$  such that  $v_I = 2.5 \,\mathrm{V}$  when all transistors are biased in the saturation region. (c) Using the results of part (b) and assuming  $v_A = v_B = 5 \,\mathrm{V}$ , determine  $v_C$  such that both  $N_3$  and  $P_3$  are biased in the saturation region. (State any assumptions you make.)

**16.40** Consider the circuit in Figure P16.40. (a) The inputs  $v_{\chi}$ ,  $v_{Y}$ , and  $v_{Z}$  listed in the following table are either a logic 0 or a logic 1. These inputs are the outputs from similar-type CMOS logic circuits. The input logic conditions listed are sequential in time. State whether the transistors listed are "on" or "off," and determine the output voltage. (b) What logic function does this circuit implement?

| VX. | Fy | $\nu_Z$ | $N_1$ | N <sub>2</sub> | $N_3$    | $N_4$ | $N_5$ | Po |

|-----|----|---------|-------|----------------|----------|-------|-------|----|

| ī   | 0  | 1       |       | KAZIL-W        | desdavid |       |       |    |

| 0   | 0  | ı       |       |                |          |       |       |    |

| 1   | 1  | 0       |       |                |          |       |       |    |

| 1   | 1  | 1       |       |                |          |       |       |    |

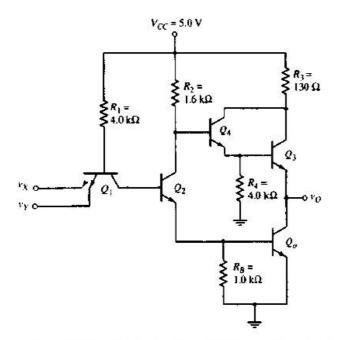

Figure P16.40

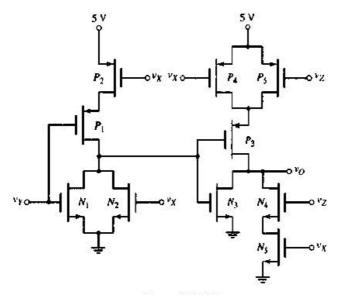

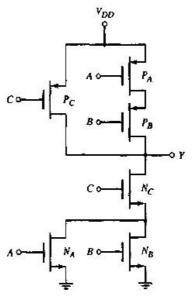

**D16.41** (a) Given inputs A, B, and C, design a CMOS circuit to implement the logic function  $Y = ABC + \overline{ABC}$ . (b) For  $k'_n = 2k'_p$  and assuming a minimum width-to-length ratio of unity, size the transistors in the design to provide equal composite conduction parameters.

**D16.42** (a) Given inputs A, B, C, and D, design a CMOS circuit to implement the logic function  $Y = \overline{(A+B)C+D}$ . (b) Repeat part (b) of Problem 16.41 for this circuit.

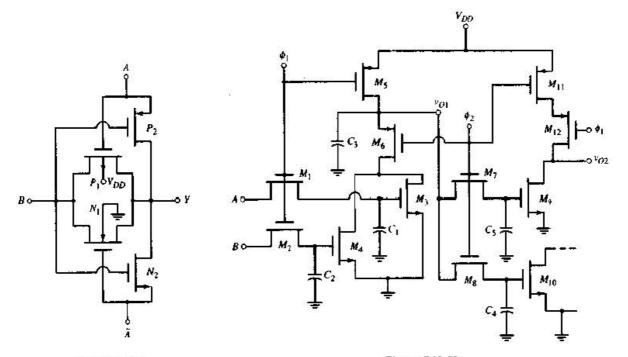

16.43 Determine the logic function implemented by the circuit in Figure P16.43.

**D16.44** Consider a five-input CMOS NAND logic gate. Assume that  $k'_a = 2k'_p$  and assume that the minimum width-to-length ratio of any single transistor is unity. Design the width-to-length ratio of each transistor such that the composite conduction parameters of the NMOS and PMOS portions of the circuit are equal and such that the composite conduction parameters are equal to those of a CMOS inverter in which  $(W/L)_p = 1$  and  $(W/L)_p = 2$ .

Figure P16.43

\*D16.45 (a) Consider a six-input CMOS NOR logic gate whose output is connected to a CMOS inverter, so the output is an OR logic function. Repeat Problem 16.44 for this circuit. (b) Redesign the circuit such that three inputs are connected to one three-input CMOS NOR gate, the other three inputs are connected to another three-input CMOS NOR gate, and the outputs of the NOR gates are connected to a two-input CMOS NAND gate. The output of the NAND gate is still the OR function of the six inputs. Design these logic circuits using the specifications of Problem 16.44. Compare the size of transistors in this design compared to that of part (a). What can be said about the expected propagation delay times of the two circuits?

### Section 16.5 Clocked CMOS Logic Circuits

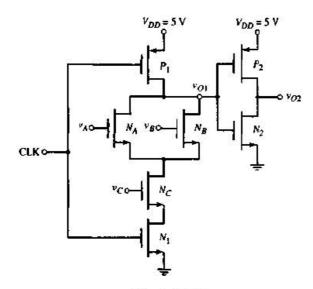

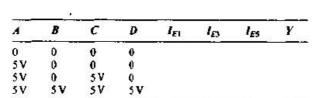

16.46 (a) Figure P16.46 shows a clocked CMOS logic circuit. Make a table showing the state of each transistor ("on" or "off"), and determine the output voltages  $v_{01}$  and  $v_{02}$  for the input logic states listed in the following table. Assume the input conditions are sequential in time from state 1 to state 6. (b) What logic function does the circuit implement?

| State | CLK | PA | ₽B | 70 |

|-------|-----|----|----|----|

| [     | 0   | 0  | 0  | 0  |

| 2     | 1   | 1  | 0  | 0  |

| 3     | 0   | 0  | 0  | 0  |

| 4     | 1   | 0  | 0  | 1  |

| 5     | 0   | 0  | 0  | 0  |

| 6     | 1   | 0  | 1  | 1  |

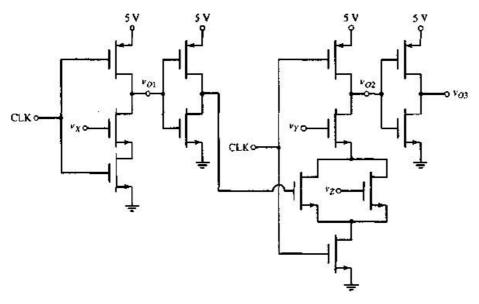

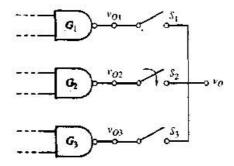

16.47 (a) For the circuit in Figure P16.47, make a table showing the state of each transistor ("on" or "off"), and determine the output voltages  $v_{O1}$ ,  $v_{O2}$ , and  $v_{O3}$  for the input logic states listed in the following table. Assume the input conditions are sequential in time from state 1 to state 6. (b) What logic function does the circuit implement?

Figure P16.46

Figure P16.47

| State | CLK | PX | ΨY | ۴Z |

|-------|-----|----|----|----|

| ī     | 0   | 0  | 0  | 0  |

| 2     | 1   | î  | 1  | 1  |

| 3     | 0   | 0  | 0  | 0  |

| 4     | Ĩ   | 0  | 1  | 1  |

| 5     | 0   | 0  | 0  | 0  |

| 6     | 1   | 1  | 0  | t  |

**D16.48** Sketch a clocked CMOS domino logic circuit that realizes the function  $Y = ABC + \overline{A} \overline{B} \overline{C}$ .

**D16.49** Sketch a clocked CMOS domino logic circuit that realizes the function Y = (A + B)C + D.

**16.50** Consider the CMOS clocked circuit in Figure 16.52(b). Assume the effective capacitance at the  $v_{O1}$  terminal is 25 fF. If the leakage current through the  $M_{NA}$  and  $M_{NB}$  transistors is  $I_{\text{Leakage}} = 2 \text{ pA}$  when these transistors and  $M_{P1}$  are cutoff, determine the time for which  $v_{O1}$  will decay by 0.5 V.

#### Section 16.6 Transmission Gates

**18.51** The parameters of an NMOS transmission gate are  $V_{IN} = 0.8 \, \text{V}$ ,  $K_n = 0.5 \, \text{mA/V}^2$ , and  $C_L = 1 \, \text{pF}$ . (a) For a gate voltage of  $\phi = 5 \, \text{V}$ , determine the quasisteady-state output voltage for (i)  $v_I = 0$ , (ii)  $v_I = 5 \, \text{V}$ , and (iii)  $v_I = 2.5 \, \text{V}$ . (b) Repeat part (a) for a gate voltage of  $\phi = 4 \, \text{V}$ .

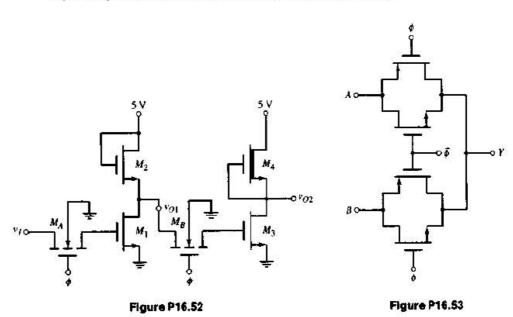

**D16.52** For the circuit in Figure P16.52, the input voltage  $v_I$  is either 0.1 V or 5 V. Let  $\phi = 5$  V. The threshold voltages are  $V_{TN} = -1.5$  V for  $M_4$  and  $V_{TN} = 0.8$  V for all other transistors. The width-to-length ratios are 1 for  $M_2$  and  $M_4$  and 10 for  $M_A$  and  $M_B$ .

(a) What are the logic 1 values of  $v_{O1}$  and  $v_{O2}$ ? (b) Design the width-to-length ratios of  $M_1$  and  $M_3$  such that the logic 0 values of  $v_{O1}$  and  $v_{O2}$  are 0.1 V.

- 16.53 What is the logic function implemented by the circuit shown in Figure P16.53? Assume that all inputs are either 0 or 5 V.

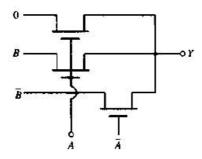

- 18.54 Consider the circuit in Figure P16.54. What logic function is implemented by this circuit? Are there any potential problems with this circuit?

- 16.55 What is the logic function implemented by the circuit in Figure P16.55?

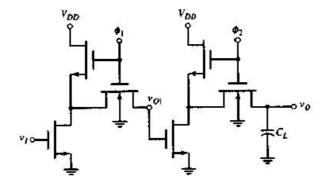

- 16.56 Consider the circuit in Figure P16.56. Signals  $\phi_1$  and  $\phi_2$  are nonoverlapping clock signals. Describe the operation of the circuit and the logic function implemented. Discuss any possible relationship between the width-to-length ratios of the load and driver transistors for "proper" circuit operation.

- 16.57 The circuit in Figure P16.57 is a form of clocked shift register. Signals  $\phi_1$  and  $\phi_2$  are nonoverlapping clock signals. Describe the operation of the circuit. Discuss any possible relationship between the width-to-length ratios of the load and driver transistors for "proper" circuit operation.

Figure P16.54

Figure P16.55

Figure P16.56

Figure P16.57

# Section 16.7 Sequential Logic Circuits

**16.58** Consider the NMOS R-S flip-flop in Figure 16.71 biased at  $V_{DD} = 5 \, \text{V}$ . The threshold voltages are 1 V (enhancement-mode devices) and  $-2 \, \text{V}$  (depletion-mode devices). The conduction parameters are  $K_3 = K_6 = 30 \, \mu \text{A/V}^2$ ,  $K_2 = K_5 = 100 \, \mu \text{A/V}^2$ , and  $K_1 = K_4 = 200 \, \mu \text{A/V}^2$ . If Q = logic 0 and  $\overline{Q} = \text{logic 1}$  initially, determine the voltage at S that will cause the flip-flop to change states.

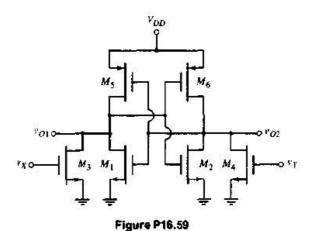

**16.59** A CMOS R-S flip-flop is shown in Figure P16.59. Assume  $V_{DD} = 5 \text{ V}$ ,  $|V_{TN}| = |V_{TP}| = 1 \text{ V}$ ,  $K_1 = K_2 = K_3 = K_4 \equiv K$ , and  $K_5 = K_6$ . If Q = logic 1 and  $\overline{Q} = \text{logic 0}$  initially, determine the relationship between  $K_5$  and K such that the flip-flop changes state when R = 2.5 V.

**D18.60** The CMOS R-S flip-flop in Figure P15.59 is not a fully complementary CMOS design. Design a fully complementary CMOS clocked R-S flip-flop. [Note: the design contains 12 transistors.]

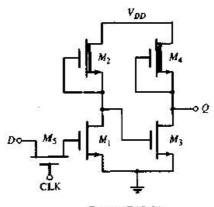

**D16.61** The circuit in Figure P16.61 is an example of a D flip-flop. (a) Explain the operation of the circuit. Is this a positive- or negative-edge-triggered flip-flop? (b) Redesign the circuit to make this a static flip-flop.

Figure P16.61

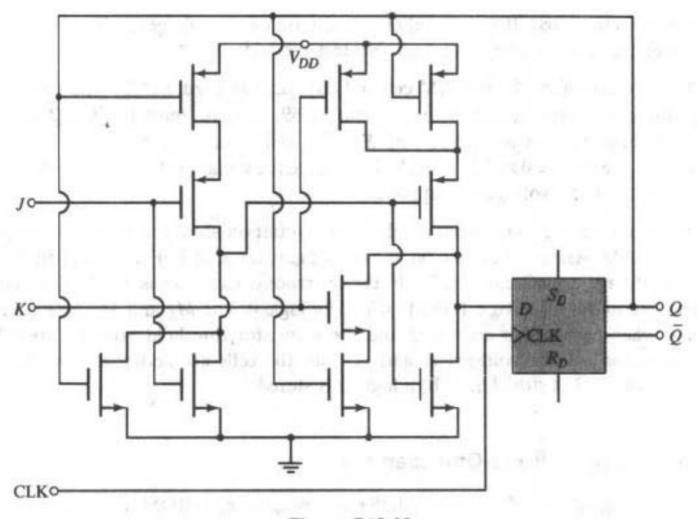

18.62 Show that the circuit in Figure P16.62 is a J-K flip-flop.

**16.63** Reconsider the circuit shown in Figure P16.40. Show that this circuit is a J-K flip-flop with  $J = v_X$ ,  $K = v_Y$ , and CLK =  $v_Z$ .

## Section 16.8 Memories: Classifications and Architectures

16.64 A 64-K memory is organized in a square array and uses the NMOS NOR decoder in Figure 16.81(b) for the row- and column decoders. (a) How many inputs does each decoder require? (b) What input to the row decoder is required to address rows (i) 94 and (ii) 239? (c) What input to the column decoder is required to address columns (i) 39 and (ii) 123?

**D16.65** A 1024-bit RAM consists of 128 words of 8 bits each. Design the memory array to minimize the number of row and column address decoder transistors required. How many row and column address lines are necessary?

18.66 Assume that an NMOS address decoder can source 250  $\mu$ A when the output goes high. If the effective capacitance of each memory cell is  $C_L=0.8\,\mathrm{pF}$  and the effective capacitance of the address line is  $C_{LA}=5\,\mathrm{pF}$ , determine the rise time of the address line voltage if  $V_{IH}=2.7\,\mathrm{V}$ .

#### Section 16.9 RAM Memory Cells

**D16.67** Consider the NMOS RAM cell with resistor load in Figure 16.82(b). Assume parameter values of  $k_R' = 35 \,\mu\text{A/V}^2$ ,  $V_{IN} = 0.7 \,\text{V}$ ,  $V_{DD} = 5 \,\text{V}$ , and  $R = 1 \,\text{M}\Omega$ . (a) Design the width-to-length ratios such that  $v_{DS} = 0.1 \,\text{V}$  for the on transistor. (b) Consider a 16-K memory with the cell described in part (a). Determine the standby current and power of the memory for a standby voltage of  $V_{DD} = 2 \,\text{V}$ .

**D16.88** A 16-K NMOS RAM, with the cell design shown in Figure 16.82(b), is to dissipate no more than 200 mW in standby when biased at  $V_{DD} = 2.5$  V. Design the width-to-length ratios of the transistors and the resistance value. Assume  $V_{TN} = 0.7$  V and  $k'_n = 35 \,\mu\text{A}/\text{V}^2$ .

\*16.89 Consider the CMOS RAM cell and data lines in Figure 16.84 biased at  $V_{DD} = 5 \text{ V}$ . Assume transistor parameters  $k_n' = 40 \,\mu\text{A/V}^2$ ,  $k_p' = 20 \,\mu\text{A/V}^2$ ,  $V_{TN} = 0.8 \,\text{V}$ ,  $V_{TP} = -0.8 \,\text{V}$ ,  $W/L = 2 \,(M_{N1} \,\text{and}\, M_{N2})$ ,  $W/L = 4 \,(M_{P1} \,\text{and}\, M_{P2})$ , and  $W/L = 4 \,(M_{P1} \,\text{and}\, M_{P2})$ .

Figure P16.62

1 (all other transistors). If Q=0 and  $\overline{Q}=1$ , determine the voltages at D and  $\overline{D}$  a short time after the row has been addressed. Neglect the body effect.

\*16.70 Consider the CMOS RAM cell and data lines in Figure 16.84 with circuit and transistor parameters described in Problem 16.69. Assume initially that Q=0 and  $\overline{Q}=1$ . Assume the row is selected with X=5 V and assume the data lines, through a write cycle, are at  $\overline{D}=0$  and D=4.2 V. Determine the voltages at Q and  $\overline{Q}$  a short time after the write cycle voltages are applied.

\*16.71 Consider a general sense amplifier configuration shown in Figure 16.90 for a dynamic RAM. Assume that each bit line has a capacitance of 1 pF and is precharged to 4 V. The storage capacitance is 0.05 pF, the reference capacitance is 0.025 pF, and each are charged to 5 V for a logic 1 and to 0 V for a logic 0. The  $M_S$  and  $M_R$  gate voltages are 5 V when each cell is addressed and the transistor threshold voltages are 0.5 V. Determine the bit line voltages  $v_1$  and  $v_2$  after the cells are addressed for the case when (a) a logic 1 is stored and (b) a logic 0 is stored.

## Section 16.10 Read-Only Memory

D16.72 Design a 4-word × 4-bit NMOS mask-programmed ROM to produce outputs of 1011, 1111, 0110, and 1001 when rows 1, 2, 3, and 4, respectively, are addressed.

D16.73 Design an NMOS  $16 \times 4$  mask-programmed ROM that provides the 4-bit product of two 2-bit variables.

D16.74 Design an NMOS mask-programmed ROM that decodes a binary input and produces the output for a seven-segment array. (See Figure 2.40, Chapter 2.) The output is to be high when a particular LED is to be turned on.

# **COMPUTER SIMULATION PROBLEMS**

16.75 The three types of NMOS inverters are shown in Figures 16.5(a), 16.8(a), and 16.10(a). Using PSpice, investigate the voltage transfer characteristics and the current versus input voltage characteristics for the three types of inverters as a function of various width-to-length ratios and as a function of the body effect.

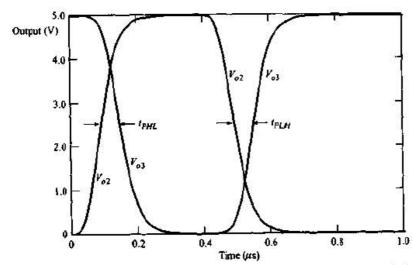

18.78 Again consider the three-types of NMOS inverters. Investigate the propagation delay times and switching characteristics of the three types of inverters using PSpice. Consider a series of inverters as shown in Figure 16.19. Include appropriate transistor capacitance values and assume effective  $C_T$  load capacitor values of 0.2 pF. Determine the propagation delay times with and without the body effect. Consider various transistor width-to-length ratios.

16.77 Consider a three-input CMOS NAND logic circuit similar to the two-input circuit shown in Figure 16.45(a). Using PSpice, investigate the voltage transfer characteristics and the current versus input voltage characteristics for various transistor width-to-length ratios and various input conditions similar to the results in Figure 16.46 for the CMOS NOR circuit.

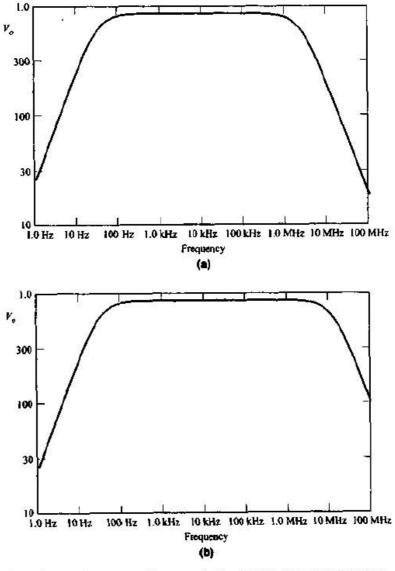

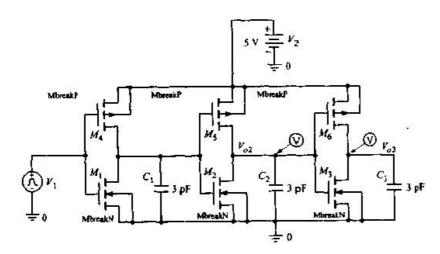

16.78 Investigate the propagation delay times and switching characteristics of the CMOS inverter using PSpice. Set up a series of CMOS inverters similar to the series of inverters shown in Figure 16.19. Include appropriate transistor capacitance values and assume effective  $C_T$  load capacitor values of 0.2 pF. Determine the propagation delay times as a function of various transistor width-to-length ratios.

16.79 Consider the dynamic shift register shown in Figure 16.68. Assume appropriate transistor and load capacitance values. Using PSpice, investigate the transient effects in voltages  $v_{01}$ ,  $v_{02}$ ,  $v_{03}$ , and  $v_{04}$  after the clock signals go to zero.

## **DESIGN PROBLEMS**

\*D18.80 Design an NMOS logic circuit that will implement the logic function  $Y = (A + (B \cdot C)) \cdot D$ .

**\*D16.81** Design clocked CMOS logic circuits that will implement the logic functions: (a)  $Y = [\overline{A + (B \cdot C)}]$ , and (b)  $Y = [(A + B) \cdot (C + D)]$ . If the smallest width-to-length ratio is 2, determine the appropriate width-to-length ratios of each transistor in your design.

\*D16.82 Design an NMOS pass logic network that implements the logic functions described in Problem 16.81.

\*D16.83 Design a clocked CMOS R-S flip-flop such that the output becomes valid on the negative-going edge of a clock signal.

\*D16.84 Design a clocked CMOS dynamic shift register in which the output becomes valid on the positive-going edge of a clock signal.

CHAPTER

17

# Bipolar Digital Circuits

#### 17.0 PREVIEW

In the previous chapter, we presented the basic concepts of MOSFET logic circuits. In this chapter, we discuss the basic principles of bipolar logic circuits. Prior to the emergence of the MOS digital technology, the bipolar digital family of transistor-transistor logic circuits was used extensively. Bipolar digital circuits are now used less frequently because of their relatively large power requirements.

Our study of bipolar digital circuits begins with emitter-coupled logic (ECL). This is the fastest bipolar technology and is used in specialized applications where high speed is required. One price to pay for high speed is a relatively low noise margin. The basis of ECL is a differential amplifier that is operated in the nonlinear region.

A bipolar technology that has a higher noise margin is transistor-transistor logic (TTL). Transistors in this technology are driven between cutoff and saturation. The storage time related to transistors driven into saturation slows the switching speed of TTL compared to that of ECL. Higher speed in TTL is achieved in Schottky TTL circuits. The basic principle of the Schottky transistor is discussed and the transistor is then applied to digital circuits. Low-power Schottky TTL makes a trade-off between speed and power.

The BiCMOS inverter and BiCMOS digital logic circuit are considered. These circuits take advantage of the low-power properties of CMOS and the high-current drive capability of bipolar transistors.

# 17.1 EMITTER-COUPLED LOGIC (ECL)

The emitter-coupled logic (ECL) circuit is based on the differential amplifier circuit, which we studied in Chapter 11 in the context of linear amplifiers. In digital applications, the diff-amp is driven into its nonlinear region. The transistors are either cut off or in the active region. Saturation is avoided in order to minimize switching times and propagation delay times. ECL circuits have the shortest propagation delay times of any bipolar digital technology.

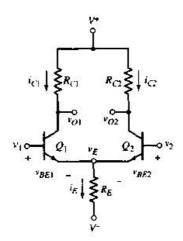

# 17.1.1 Differential Amplifier Circuit Revisited

Consider the basic diff-amp circuit in Figure 17.1. For a linear diff-amp, the input voltages are small and both transistors remain biased in the active region at all times. The relationship between collector currents and base-emitter voltages for  $Q_1$  and  $Q_2$  can be written<sup>1</sup>

$$i_{\rm Cl} = I_{\rm S} e^{v_{\rm BE}/P_T} \tag{17.1(a)}$$

and

$$i_{C2} = I_S e^{v_{B2}/V_T}$$

(17.1(b))

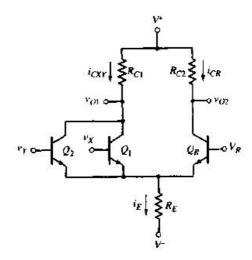

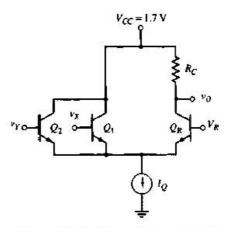

Figure 17.1 Basic differential amplifier circuit

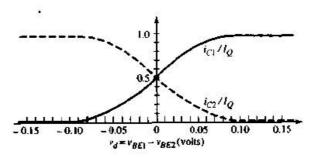

where  $Q_1$  and  $Q_2$  are assumed to be matched and parameter  $I_S$  is the same for both devices. The current-voltage transfer curves are shown in Figure 17.2.

In digital applications, the input voltages are large, which means that one transistor remains biased in its active region while the opposite transistor is cut off. For example, if  $v_{BE1} = v_{BE2} + 0.12$ , then the ratio of  $i_{C1}$  and  $i_{C2}$  is

$$\frac{i_{C1}}{i_{C2}} = \frac{e^{v_{BE1}/V_T}}{e^{v_{BE1}/V_T}} = e^{(v_{BE1} - v_{BE2})/V_T} = e^{0.12/0.026} = 101$$

(17.2)

Figure 17.2 Normalized dc transfer characteristics, BJT differential amplifier

<sup>&</sup>lt;sup>1</sup>In most cases in this chapter, total instantaneous current and voltage parameters are used, even though most analyses of logic circuits involve de calculations.

When the base-emitter voltage of  $Q_1$  is 120 mV greater than the base-emitter voltage of  $Q_2$ , the collector current of  $Q_1$  is 100 times that of  $Q_2$ ; for all practical purposes,  $Q_1$  is on and  $Q_2$  is cut off.

Conversely, if  $v_1$  is less than  $v_2$  by at least 120 mV, then  $Q_1$  is effectively cut off and  $Q_2$  is on. The difference amplifier, when operating as a digital circuit, operates as a current switch. When  $v_1 > v_2$  by at least 120 mV, it switches an approximately constant current through  $R_E$  to  $Q_1$ ; when  $v_2 > v_1$  by at least 120 mV, the current goes to  $Q_2$ .

**Example 17.1 Objective:** Calculate the currents and voltages in the basic differential amplifier circuit used as a digital circuit.

Consider the circuit in Figure 17.1. Assume that  $V^+ = -V^- = 5 \text{ V}$ ,  $R_{C1} = R_{C2} \equiv R_C = 1 \text{ k}\Omega$ ,  $R_E = 2.15 \text{ k}\Omega$ , and  $v_2 = 0$ . In the dc analysis, assume that dc base currents are negligible.

**Solution:** For  $v_1 = 0$ , both transistors are on. Assuming a base-emitter turn-on voltage of 0.7 V, then  $v_E = -0.7$  V and

$$i_E = \frac{v_E - V^-}{R_E} = \frac{-0.7 - (-5)}{2.15} = 2.0 \,\text{mA}$$

Assuming  $Q_1$  and  $Q_2$  are matched, we have  $i_{C1} = i_{C2} = i_{E/2}$  since  $v_{BE1} = v_{BE2}$  and  $i_{C1} = i_{C2} \equiv i_{C} = 1$  mA. In this case,

$$v_{O1} = v_{O2} = V_{CC} - i_C R_C = 5 - (1)(1) = 4V$$

Both  $Q_1$  and  $Q_2$  are now biased in the active region.

Now let  $v_1 = -1$  V. Since the base voltage of  $Q_1$  is less than the base voltage of  $Q_2$  by more than  $120 \,\mathrm{mV}$ ,  $Q_1$  is cut off and  $Q_2$  is on. In this case,  $v_E = v_2 - V_{BE}(\mathrm{on}) = -0.7 \,\mathrm{V}$  and  $i_E = 2 \,\mathrm{mA}$ , as before. However,  $i_{C1} = 0$  and  $i_{C2} = i_E = 2 \,\mathrm{mA}$ , so that

$$v_{O1} = V_{CC} = 5 \text{ V}$$

and

$$v_{O2} = V_{CC} - i_{C2}R_C = 5 - (2)(1) = 3 \text{ V}$$

For  $v_1 = +1$  V,  $Q_1$  is on and  $Q_2$  is cut off. For this case,  $v_E = v_1 - V_{BE}(\text{on}) = 1 - 0.7 = +0.3$  V, the current  $i_E$  is

$$i_E = i_{C1} = \frac{v_E - V^-}{R_E} = \frac{0.3 - (-5)}{2.15} = 2.47 \text{ mA}$$

and

$$v_{O1} = V_{CC} - i_{C1}R_C = 5 - (2.47)(1) = 2.53 \text{ V}$$

and

$$v_{O2} = V_{CC} = 5 \text{ V}$$

**Comment:** For the three conditions given, transistors  $Q_1$  and  $Q_2$  are biased either in cutoff or in the active region. In terms of digital applications, output  $v_{02}$  is in phase with input  $v_1$  and output  $v_{01}$  is 180 degrees out of phase.

When biased on, transistor  $Q_1$  conducts slightly more heavily than  $Q_2$  when it is conducting. To obtain symmetrical complementary outputs,  $R_{C1}$  should therefore be slightly smaller than  $R_{C2}$ .

## **Test Your Understanding**

**D17.1** Consider the differential amplifier circuit in Figure 17.1 biased at  $V^+ = 5 \text{ V}$ ,  $V^- = -5 \text{ V}$ , and  $v_2 = 0$ . Assume  $V_{BE}(\text{on}) = 0.7 \text{ V}$  and neglect base currents. (a) Design the circuit such that  $i_E = 1 \text{ mA}$  and  $v_{O1} = v_{O2} = 3.5 \text{ V}$  when  $v_1 = 0$ . (b) Using the results of part (a), calculate  $i_E$ ,  $v_{O1}$ , and  $v_{O2}$  for: (i)  $v_1 = +1 \text{ V}$ , and (ii)  $v_4 = -1 \text{ V}$ . (Ans. (a)  $R_E = 4.3 \text{ k}\Omega$ ,  $R_{C1} = R_{C2} = 3 \text{ k}\Omega$  (b) (i)  $i_E = 1.23 \text{ mA}$ .  $v_{O1} = 1.31 \text{ V}$ ,  $v_{O2} = 5 \text{ V}$  (ii)  $v_{O2} = 2 \text{ V}$ ,  $v_{O1} = 5 \text{ V}$ )

## 17.1.2 Basic ECL Logic Gate

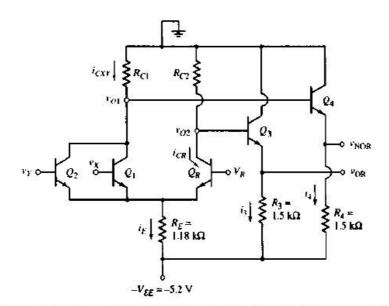

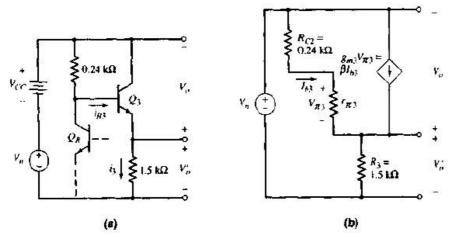

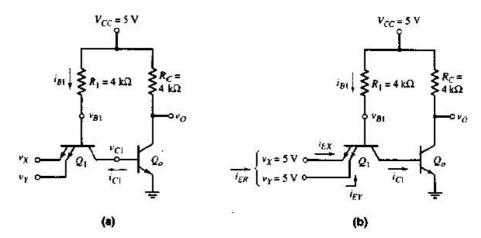

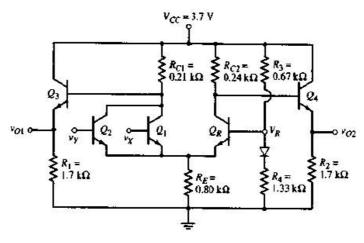

A basic two-input ECL OR/NOR logic circuit is shown in Figure 17.3. The two input transistors,  $Q_1$  and  $Q_2$ , are connected in parallel. On the basis of the differential amplifier, if both  $v_X$  and  $v_Y$  are less than the reference voltage  $V_R$  (by at least 120 mV), then both  $Q_1$  and  $Q_2$  are cut off, while the reference transistor  $Q_R$  is biased on its active region. In this situation, the output voltage  $v_{O1}$  is greater than  $v_{O2}$ . If either  $v_X$  or  $v_Y$  becomes greater than  $V_R$ , then  $Q_R$  turns off and  $v_{O2}$  becomes larger than  $v_{O1}$ . The OR logic is at the  $v_{O2}$  output and the NOR logic is at the  $v_{O1}$  output. An advantage of ECL gates is the availability of complementary outputs, precluding the need for separate inverters to provide the complementary outputs.

One problem with the OR/NOR circuit in Figure 17.3 is that the output voltage levels differ from the required input voltage levels; the output voltages are not compatible with the input voltages. The mismatch arises because ECL

Figure 17.3 Basic two-input ECL OR/NOR logic circuit

circuit transistors operate between their cutoff and active regions, requiring that the base-collector junctions be reverse biased at all times. We see that a logic I voltage of the output is  $V_{OH} = V^+$ . If this voltage were to be applied to either the  $v_X$  or  $v_Y$  input, then either  $Q_1$  or  $Q_2$  would turn on and the collector voltage  $v_{O1}$  would decrease below  $V^+$ ; the base-collector voltage would then become forward biased and the transistor would go into saturation. Emitter-follower circuits are added to provide outputs that are compatible with the inputs of similar gates.

## **Test Your Understanding**

**D17.2** For the ECL logic gate in Figure 17.3, the bias voltages are:  $V^+ = 3.5 \text{ V}$ ,  $V^- = -3.5 \text{ V}$ , and  $V_R = 1.5 \text{ V}$ . Assume  $V_{BE}(\text{on}) = 0.7 \text{ V}$  and neglect base currents. (a) Determine  $R_E$  and  $R_{C2}$  such that  $i_E = 2 \text{ mA}$  and  $v_{O2} = 2 \text{ V}$  when  $v_x = v_y = \text{logic}$  0. (b) Find  $R_{C1}$  such that  $v_{O1} = 2 \text{ V}$  when  $v_x = v_y = 2 \text{ V}$ . What is  $i_E$ ? (Ans. (a)  $R_E = 2.15 \text{ k}\Omega$ ,  $R_{C2} = 0.75 \text{ k}\Omega$  (b)  $i_E = 2.23 \text{ mA}$ ,  $R_{C1} = 0.673 \text{ k}\Omega$ )

## ECL Logic Gate with Emitter Followers

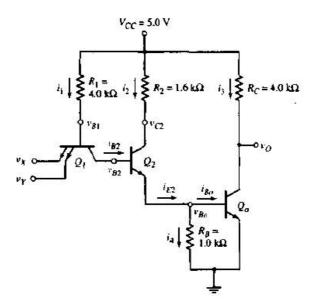

In the ECL circuit in Figure 17.4, emitter followers are added to the OR/NOR outputs, and supply voltage  $V^+$  is set equal to zero. The ground and power supply voltages are reversed because analyses show that using the collector-emitter voltage as the output results in less noise sensitivity. If the forward current gain of the transistors is on the order of 100, then the dc base currents may be neglected with little error in the calculations.

Figure 17.4 Two-input ECL OR/NOR logic gate with emitter-follower output stages

If either  $v_X$  or  $v_Y$  is a logic 1 (defined as greater than  $V_R$  by at least 120 mV), then the reference transistor  $Q_R$  is cut off,  $i_{CR} = 0$ , and  $v_{O2} = 0$ . Output transistor  $Q_3$  is biased in the active region, and  $v_{OR} = v_{O2} - V_{BE}(\text{on}) = -0.7 \text{ V}$ . If both  $v_X$  and  $v_Y$  are a logic 0 (defined as less than  $V_R$  by at least 120 mV), then both  $Q_1$  and  $Q_2$  are cut off,  $v_{O1} = 0$ , and  $v_{NOR} = 0 - V_{BE}(\text{on}) = -0.7 \text{ V}$ . The largest possible voltage that can be achieved at either output is -0.7 V; therefore, -0.7 V is defined as the logic 1 level.

In the following example, we will determine the currents and the logic 0 values in the basic ECL gate.

**Example 17.2 Objective:** Calculate current, resistor, and logic 0 values in the basic ECL logic gate.

Consider the circuit in Figure 17.4. Determine  $R_{C1}$  and  $R_{C2}$  such that when  $Q_1$ ,  $Q_2$ , and then  $Q_R$  are conducting, the B-C voltages are zero.

**Solution:** Let  $v_X = v_Y = -0.7 \text{ V} = \text{logic I} > V_R$  such that  $Q_1$  and  $Q_2$  are on. We find that

$$v_E = v_X - V_{BE}(\text{on}) = -0.7 - 0.7 = -1.4 \text{ V}$$

and the current is

$$i_E = i_{Cxy} = \frac{v_E - V^-}{R_E} = \frac{-1.4 - (-5.2)}{1.18} = 3.22 \text{ mA}$$

In order for the B-C voltages of  $Q_1$  and  $Q_2$  to be zero, voltage  $v_{O1}$  must be  $-0.7\,\mathrm{V}$ . Therefore

$$R_{C1} = \frac{-v_{O1}}{I_{Cxx}} = \frac{0.7}{3.22} = 0.217 \text{k}\Omega$$

The NOR output logic 0 value is then

$$v_{\text{NOR}} = v_{O1} - V_{BE}(\text{on}) = -0.70 - 0.7 = -1.40 \text{ V}$$

Input voltages  $v_X$  and  $v_Y$  are greater than  $V_R$  in a logic 1 state and less than  $V_R$  in a logic 0 state. If  $V_R$  is set at the midpoint between the logic 0 and logic 1 levels, then

$$V_R = \frac{-0.7 - 1.40}{2} = -1.05 \text{ V}$$

When  $Q_R$  is on, we have

$$v_F = V_R - V_{BE}(\text{on}) = -1.05 - 0.7 = -1.75 \text{ V}$$

and

$$i_E = i_{CR} = \frac{v_E - V^-}{R_E} = \frac{-1.75 - (-5.2)}{1.18} = 2.92 \,\text{mA}$$

For  $v_{02} = -0.7 \text{ V}$ , we find that

$$R_{C2} = \frac{-v_{O2}}{i_{C2}} = \frac{0.7}{2.92} = 0.240 \,\mathrm{k}\Omega$$

The OR logic 0 value is therefore

$$v_{OR} = v_{O2} - V_{BE}(on) = -0.7 - 0.7 = -1.40 \text{ V}$$

**Comment:** For symmetrical complementary outputs,  $R_{C1}$  and  $R_{C2}$  are not equal. If  $R_{C1}$  and  $R_{C2}$  become larger than the designed values, transistors  $Q_1$ ,  $Q_2$ , and  $Q_R$  will be driven into saturation when they are conducting.

## **Test Your Understanding**

**D17.3** Redesign the ECL circuit in Figure 17.4 such that the logic 0 values at the  $v_{\rm OR}$  and  $v_{\rm NOR}$  terminals are -1.5 V. The maximum value of  $i_E$  is to be 2.5 mA, and the maximum values of  $i_3$  and  $i_4$  are to be 2.5 mA. The bias voltages are as shown. Determine all resistor values and the value of  $V_R$ . (Ans.  $R_E = 1.52 \, \rm k\Omega$ .  $R_{C1} = 320 \, \Omega$ ,  $V_R = -1.1 \, \rm V$ ,  $R_{C2} = 357 \, \Omega$ ,  $R_3 = R_4 = 1.8 \, \rm k\Omega$ )

**17.4** Using the results of Example 17.2, calculate the power dissipated in the circuit in Figure 17.4; for: (a)  $v_x = v_y = \log i - 1$ , and (b)  $v_y = v_y = \log i - 0$ . (Ans. (a)  $P = 45.5 \,\mathrm{mW}$  (b)  $P = 43.9 \,\mathrm{mW}$ )

#### The Reference Circuit

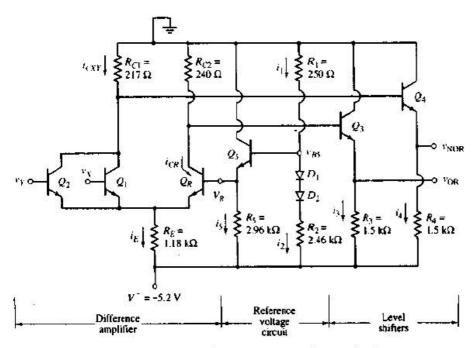

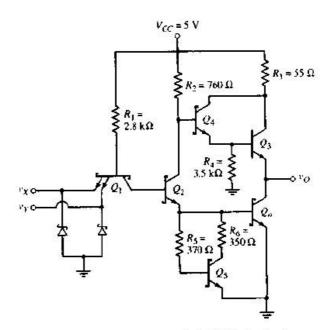

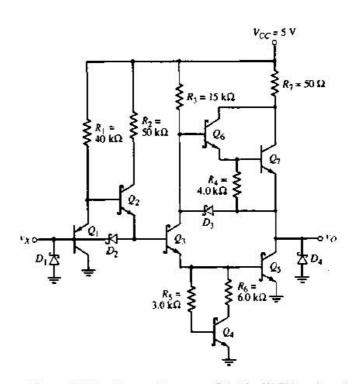

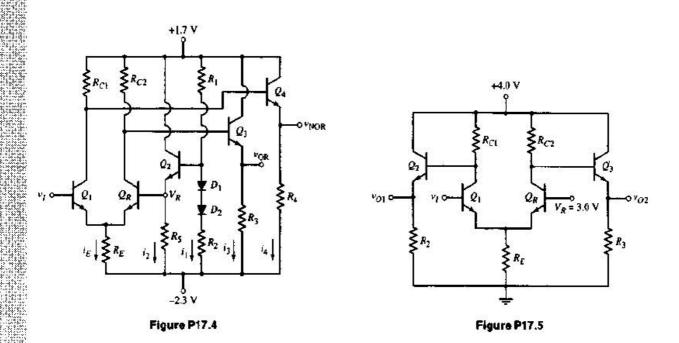

Another circuit is required to provide the reference voltage  $V_R$ . Consider the complete two-input ECL OR/NOR logic circuit shown in Figure 17.5. The reference circuit consists of resistors  $R_1$ ,  $R_2$ , and  $R_5$ , diodes  $D_1$  and  $D_2$ , and transistor  $Q_5$ . The reference portion of the circuit can be specifically designed to provide the desired reference voltage.

Figure 17.5 Basic ECL logic gate with reference circuit

Design Example 17.3 Objective: Design the reference portion of the ECL circuit.

Consider the circuit in Figure 17.5. The reference voltage  $V_R$  is to be  $-1.05\,\mathrm{V}$ .

Solution: We know that

$$v_{B5} = V_R + V_{BE}(\text{on}) = -1.05 + 0.7 = -0.35 \text{ V} = -i_1 R_1$$

Since there are two unknowns, we will choose one variable. Let  $R_1 = 0.25 \,\mathrm{k}\Omega$ . Then,

$$i_1 = \frac{0.35}{0.25} = 1.40 \,\mathrm{mA}$$

Since this current is on the same order of magnitude as other currents in the circuit, the chosen value of  $R_1$  is reasonable. Neglecting base currents, we can now write

$$i_1 = i_2 = \frac{0 - 2V_{\gamma} - V^{-}}{R_1 + R_2}$$

where  $V_{\nu}$  is the diode turn-on voltage and is assumed to be  $V_{\nu} = 0.7 \, \text{V}$ . We then have

$$1.40 = \frac{-1.4 - (-5.2)}{R_1 + R_2}$$

which yields

$$R_1 + R_2 = 2.71 \,\mathrm{k}\Omega$$

Since  $R_1 = 0.25 \,\mathrm{k}\Omega$ , resistance  $R_2$  is  $R_2 = 2.46 \,\mathrm{k}\Omega$ . Also, we know that

$$i_5 = \frac{V_R - V^-}{R_5}$$

If we let  $i_5 = i_1 = i_2 = 1.40 \text{ mA}$ , then

$$R_5 = \frac{V_R - V^2}{i_5} = \frac{-1.05 - (-5.2)}{1.40} = 2.96 \,\mathrm{k}\Omega$$

**Comment:** As with any design, there is no unique solution. The design presented will provide the required reference voltage to the base of  $Q_R$ .

## 17.1.3 ECL Logic Circuit Characteristics

In this section, we will determine the power dissipation, fanout, and propagation delay times for the ECL logic gate. We will also examine the advantage of using a negative power supply.

#### **Power Dissipation**

Power dissipation is an important characteristic of a logic circuit. The power dissipated in the basic ECL logic gate in Figure 17.5 is given by

$$P_D = (i_{Cxy} + i_{CR} + i_3 + i_1 + i_3 + i_4)(0 - V^-)$$

(17.3)

**Example 17.4 Objective:** Calculate the power dissipated in the ECL logic circuit. Consider the circuit in Figure 17.5. Let  $v_X = v_Y = -0.7 \text{ V} = \log c 1$ .

**Solution:** From our previous analysis, we have  $i_{Cxy} = 3.22 \,\text{mA}$ ,  $i_{CR} = 0$ ,  $i_5 = 1.40 \,\text{mA}$ , and  $i_1 = 1.40 \,\text{mA}$ , and the output voltages are  $v_{OR} = -0.7 \,\text{V}$  and  $v_{NOR} = -1.40 \,\text{V}$ . The currents  $i_3$  and  $i_4$  are

$$i_3 = \frac{v_{\text{OR}} - V^-}{R_3} = \frac{-0.7 - (-5.2)}{1.5} = 3.0 \,\text{mA}$$

and

$$i_4 = \frac{v_{NOR} - V^-}{R_A} = \frac{-1.40 - (-5.2)}{1.5} = 2.53 \text{ mA}$$

The power dissipation is then

$$P_D = (3.22 + 0 + 1.40 + 1.40 + 3.0 + 2.53)(5.2) = 60.0 \text{ mW}$$

Comment: This power dissipation is significantly larger than that in NMOS and CMOS logic circuits. The advantage of ECL, however, is the short propagation delay times, which can be less than 1 ns.

## Propagation Delay Time

The major advantage of ECL circuits is their small propagation delay time, on the order of 1 ns or less. The two reasons for the short propagation delay times are: (1) the transistors are not driven into saturation, which eliminates any charge storage effects; and (2) the logic swing in the ECL logic gate is small (about 0.7 V), which means that the voltages across the output capacitances do not have to change as much as in other logic circuits. Also, the currents in the ECL circuit are relatively large, which means that these capacitances can charge and discharge quickly. However, the trade-offs for the small propagation delay time are higher power dissipation and smaller noise margins.

ECL circuits are very fast, and they require that special attention be paid to transmission line effects. Improperly designed ECL circuit boards can experience ringing or oscillations. These problems have less to do with the ECL circuits than with the interconnections between the circuits. Care must therefore be taken to terminate the signal lines properly.

#### **Fanout**

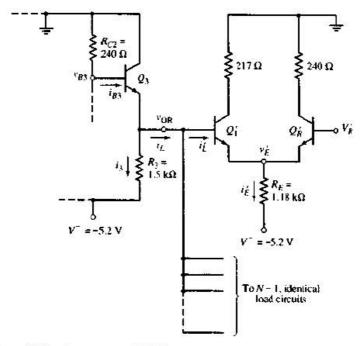

Figure 17.6 shows the emitter-follower output stage of the OR output of an ECL circuit used to drive the diff-amp input stage of an ECL load circuit. When  $v_{OR}$  is a logic 0, input load transistor  $Q_1'$  is cut off, effectively eliminating any load current from the driver output stage. With  $v_{OR}$  at a logic 1 level, the input load transistor is on and an input base current  $i_L$  exists. (Up to this point, we have neglected dc base currents; however, they are not zero.) The load current must be supplied through  $Q_3$ , whose base current is supplied through  $R_{C2}$ . As the load current  $i_L$  increases with the addition of more load circuits, a voltage drop occurs across  $R_{C2}$  and the output voltage decreases. The maximum fanout is determined partially by the maximum amplitude that the output voltage is allowed to drop from its ideal logic 1 value.

Figure 17.6 Output stage of ECL logic gate driving N identical ECL input stages

**Example 17.5 Objective:** Calculate the maximum fanout of an ECL logic gate, based on de loading effects.

Consider the circuit in Figure 17.6. Assume the current gain of the transistors is  $\beta = 50$ , which represents a worst-case scenario. Assume that the logic 1 level at the OR output is allowed to decrease by 50 mV at most from a value of -0.70 V to -0.75 V.

Solution: From the figure, we see that

$$i_E' = \frac{v_{\text{OR}} - V_{BE}(\text{on}) - V^-}{R_E} = \frac{-0.75 - 0.7 - (-5.2)}{1.18} = 3.18 \text{ mA}$$

The input base current to the load transistor is

$$i'_{B} = \frac{i'_{E}}{(1+\beta)} = \frac{3.18}{51} \Rightarrow 62.4 \,\mu\text{A} = i'_{L}$$

The total load current is therefore  $i_L = Ni'_L$ .

The base current  $i_{B3}$  required to produce both the load current  $i_L$  and current  $i_3$  is

$$i_{B3} = \frac{i_3 + i_L}{(1 + \beta)} = \frac{0 - v_{B3}}{R_{C2}} = \frac{0 - (v_{OR} + V_{BE}(on))}{R_{C2}}$$

(17.4)

Also, from the figure we see that

$$i_3 = \frac{v_{\text{OR}} - V^{-}}{R_3} = \frac{-0.75 - (-5.2)}{1.5} = 2.97 \,\text{mA}$$

From Equation (17.4), the maximum fanout for this condition is

$$\frac{2.97 + N(0.0624)}{51} = \frac{0 - (-0.75 + 0.7)}{0.24}.$$

which yields N = 122.

Comment: This maximum fanout is based on dc conditions and is unrealistic. In practice, the maximum fanout for ECL circuits is determined by the propagation delay time. Each load circuit increases the load capacitance by approximately 3 pF. A maximum fanout of about 15 is usually recommended to keep the propagation delay time within specified limits.

## The Negative Supply Voltage

In classic ECL circuits, it is common practice to ground the positive terminal of the supply voltage, reducing the noise signals at the output terminal. Figure 17.7(a) shows an emitter-follower output stage with the supply voltage  $V_{CC}$  in series with a noise source  $V_n$ . The noise signal may be induced by the effect of switching currents interacting with parasitic inductances and capacitances. The output voltage is measured with respect to ground; therefore, if the positive terminal of  $V_{CC}$  is grounded, voltage  $V_o$  is taken as the output voltage. If the negative terminal of  $V_{CC}$  is at ground, then  $V_o$  is the output voltage.

**Figure 17.7** (a) Equivalent circuit, ECL emitter-follower output stage and noise generator, and the (b) small-signal hybrid- $\pi$  equivalent circuit

To determine the effect of the noise voltage at the output, we assume that  $Q_R$  is cut off, and we evaluate the small-signal hybrid- $\pi$  equivalent circuit shown in Figure 17.7(b).

**Example 17.6 Objective:** Determine the effect of a noise signal on the output of an ECL gate.

Consider the small-signal equivalent circuit in Figure 17.7(b). Let  $\beta = 100$ . Find  $V_o$  and  $V_o$  as a function of  $V_o$ .

**Solution:** From a previous analysis, the quiescent collector current in  $Q_3$  for  $Q_R$  in cutoff is 3 mA. Then,

$$r_{\pi 3} = \frac{\beta V_T}{I_{CQ}} = \frac{(100)(0.026)}{3} = 0.867 \,\mathrm{k}\Omega$$

and

$$g_{m3} = \frac{I_{CQ}}{V_T} = \frac{3}{0.026} = 115 \,\text{mA/V}$$

We can also write that

$$V_n = I_{b3}(R_{C2} + r_{m3}) + (1 + \beta)I_{b3}R_3$$

which yields

$$I_{b3} = \frac{V_n}{R_{C2} + t_{\pi 3} + (1 + \beta)R_3} = \frac{V_n}{0.24 + 0.867 + (101)(1.5)} = \frac{V_n}{152.6}$$

The output voltage  $V_o$  is

$$V_a = -I_{b3}(R_{C2} + r_{n3}) = -\left(\frac{V_n}{152.6}\right)(0.24 + 0.867) = -0.0073V_n$$

and output voltage  $V'_{o}$  is

$$V_o' = (1 + \beta)I_{b3}R_3 = (101)\left(\frac{V_n}{152.6}\right)(1.5) = 0.99V_n$$

**Comment:** The effect of noise on the collector-emitter output voltage  $V_o$  is much less than on output voltage  $V_o$ . It is advantageous, then, to use  $V_o$ , which implies that the positive terminal of  $V_{CC}$  is grounded. The noise insensitivity gained with a negative power supply may be critical in a logic circuit with a low noise margin.

# 17.1.4 Voltage Transfer Characteristics

The voltage transfer curve indicates the circuit characteristics during transition between the two logic states. The voltage transfer characteristics can also be used to determine the noise margins.

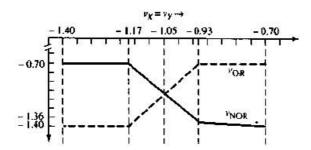

## DC Analysis

A good approximation of the voltage transfer characteristics can be derived from the piecewise linear model of the two input transistors and the reference transistor. Consider the ECL gate in Figure 17.5. If inputs  $v_X$  and  $v_Y$  are a logic 0, or  $-1.40 \,\mathrm{V}$ , then  $Q_1$  and  $Q_2$  are cut off and  $v_{\mathrm{NOR}} = -0.7 \,\mathrm{V}$ . The reference transistor  $Q_R$  is on and, as previously seen,  $i_E = i_{C2} = 2.92 \,\mathrm{mA}$ ,  $v_{B3} = -0.70 \,\mathrm{V}$ , and  $v_{\mathrm{OR}} = -1.40 \,\mathrm{V}$ . As long as  $v_X = v_Y$  remains less than  $V_R = 0.12 = -1.17 \,\mathrm{V}$ , the output voltages do not change from these values. During the interval when the inputs are within 120 mV of reference voltage  $V_R$ , the output voltage levels vary.

When  $v_X = v_Y = V_R + 0.12 = -0.93 \text{ V}$ , then  $Q_1$  and  $Q_2$  are on and  $Q_R$  is off. At this point,  $i_E = i_{C1} = 3.03 \text{ mA}$ ,  $v_{B4} = -0.657 \text{ V}$ , and  $v_{NOR} = -1.36 \text{ V}$ . As determined previously, when  $v_X = v_Y = -0.7 \text{ V}$ ,  $v_{NOR} = -1.40 \text{ V}$ . The voltage transfer curves are shown in Figure 17.8.

#### Noise Margin

For the ECL gate, we define the threshold logic levels  $V_{IL}$  and  $V_{IH}$  as the points of discontinuity in the voltage transfer curves. These values are  $V_{IL} = -1.17 \,\mathrm{V}$

Figure 17.8 ECL OR/NOR logic gate voltage transfer characteristics

and  $V_{IH} = -0.93 \,\text{V}$ . The high logic level is  $V_{OH} = -0.7 \,\text{V}$  and the low logic value is  $V_{OL} = -1.40 \,\text{V}$ .

The noise margins are defined as

$$NM_H = V_{OH} - V_{IH} \tag{17.5(a)}$$

and

$$NM_L = V_{IL} - V_{OL} \tag{17.5(b)}$$

Using the results from Figure 17.8, we find that  $NM_H = 0.23 \text{ V}$  and  $NM_L = 0.23 \text{ V}$ . The noise margins for the ECL circuit are considerably lower than those calculated for NMOS and CMOS circuits.

#### **Test Your Understanding**

17.5 Consider the ECL circuit in Figure 17.4. Using the results of Example 17.2, plot the voltage transfer characteristics for  $-1.40 \le v_x = v_y \le -0.7 \text{ V}$ . Find the noise margins NM<sub>H</sub> and NM<sub>L</sub>. (Ans. NM<sub>H</sub> = 0.23 V, NM<sub>L</sub> = 0.23 V)

## 17.2 MODIFIED ECL CIRCUIT CONFIGURATIONS

The large power dissipation in the basic ECL logic gate makes this circuit impractical for large-scale integrated circuits. Certain modifications can simplify the circuit design and decrease the power consumption, making the ECL more compatible with integrated circuits.

## 17.2.1 Low-Power ECL

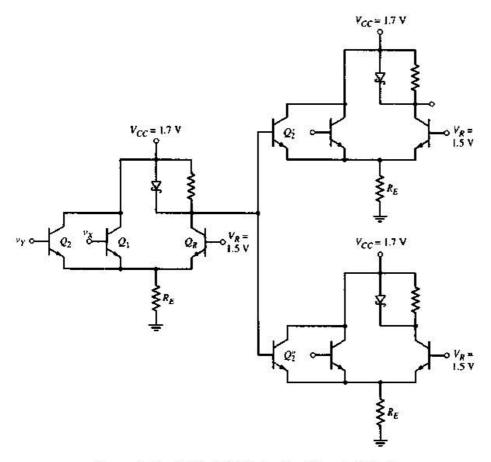

Figure 17.9(a) shows a basic ECL OR/NOR logic gate with reference voltage  $V_R$  and a positive voltage supply. We can make the output voltage states compatible with the input voltages, eliminating the need for the emitter-follower output stages. In some applications, both complementary outputs may not be required. If, for example, only the OR output is required, then we can eliminate resistor  $R_{C1}$ . Removing this resistor does not reduce the circuit power consumption, but it eliminates one element.

Figure 17.9 (a) Basic ECL OR/NOR logic gate and (b) modified ECL logic gate

Figure 17.9(b) shows the modified ECL gate. For  $v_x = v_y \log c \ 1 > V_R$ , transistors  $Q_1$  and  $Q_2$  are turned on and  $Q_R$  is off. The output voltage is  $v_{OR} = V_{CC}$ . For  $v_x = v_y = \log c \ 0 < V_R$ , then  $Q_1$  and  $Q_2$  are off and  $Q_R$  is on. The currents are

$$i_E = \frac{V_R - V_{BE}(\text{on})}{R_E} \cong i_{CR}$$

(17.6)

and the output voltage is

$$v_{\rm OR} = V_{\rm CC} - i_{\rm CR} R_{\rm C2} \tag{17.7}$$

If the resistance values of  $R_E$  and  $R_{C2}$  vary from one circuit to another because of fabrication tolerances, then current  $i_E$  and the logic 0 output voltage will vary from one circuit to another.

To establish a well-defined logic 0 output, we can insert a Schottky diode in parallel with resistor  $R_C$ , as shown in Figure 17.10. If the two inputs are a logic 0, then  $Q_1$  and  $Q_2$  are off and  $Q_R$  is on. For this condition, we want the Schottky diode to turn on. The output will then be  $v_{\rm OR} = V_{CC} - V_{\gamma}$ , where

Figure 17.10 Modified ECL logic gate with Schottky diode

$V_{\gamma}$  is the turn-on voltage of the Schottky diode. This logic 0 output voltage is a well-defined value. If the diode turns on, then current  $i_R$  is limited to  $i_R(\max) = V_{\gamma}/R_C$ . Since we must have  $i_E > i_R(\max)$ , the diode current is  $i_D = i_E - i_R(\max)$ .

Example 17.7 Objective: Analyze the modified ECL logic gate.

Consider the circuit in Figure 17.10 with parameters  $V_{CC} = 1.7 \,\text{V}$  and  $R_E = R_C = 8 \,\text{k}\Omega$ . Assume the diode and transistor piecewise linear parameters are  $V_V = 0.4 \,\text{V}$  and  $V_{BE}(\text{on}) = 0.7 \,\text{V}$ .

Solution: The output voltage values are

$$v_{OR} = logic I = V_{CC} = 1.7 \text{ V}$$

and

$$v_{OR} = logic \ 0 = V_{CC} - V_{y} = 1.7 - 0.4 = 1.3 \text{ V}$$

For the output voltages to be compatible with the inputs, the reference voltage  $V_R$  must be the average of the logic 1 and logic 0 values, or  $V_R = 1.5 \text{ V}$ . If  $v_x = v_y = \log c = 1.3 \text{ V}$ , then  $Q_R$  is on. Therefore,

$$i_E = \frac{V_R - V_{BE}(\text{on})}{R_E} = \frac{1.5 - 0.7}{8} \Rightarrow 100 \,\mu\text{A}$$

The maximum current in  $R_C$  is

$$i_R(\text{max}) = \frac{V_Y}{R_C} = \frac{0.4}{8} \Rightarrow 50 \,\mu\text{A}$$

and the current through the diode is

$$i_D = i_E - i_R(\text{max}) = 100 - 50 = 50 \,\mu\text{A}$$

For  $v_x = v_y = \text{logic } 0$ , the power dissipation is  $P = i_E V_{CC}$ , or

$$P = i_E V_{CC} = (100)(1.7) \approx 170 \,\mu\text{W}$$

For  $v_v = v_v = \text{logic } 1 = 1.7 \text{ V}$ , we have

$$i_E = \frac{v_x - V_{BE}(on)}{R_E} = \frac{1.7 - 0.7}{\$} \Rightarrow 125 \,\mu\text{A}$$

Therefore, the power dissipation for this condition is

$$P = i_E V_{CC} = (125)(1.7) = 213 \,\mu\text{W}$$

Comment: If the resistance values of  $R_E$  and  $R_C$  were to change by as much as  $\pm 20$  percent as a result of manufacturing tolerances, for example, the currents would still be sufficient to turn the Schottky diode on when  $Q_R$  is on. This means that the logic 0 output is well defined. Also, the power dissipation in this ECL gate is considerably less than that in the classic ECL OR/NOR logic circuit. The reduced power is a result of fewer components, lower bias voltage, and smaller currents.

When transistor  $Q_R$  is off, its collector voltage is 1.7V and the B-C junction is reverse biased by 0.2 V. When  $Q_R$  is conducting, its collector voltage is 1.3 V, the B-C junction is forward biased by 0.2 V, and the transistor is biased slightly in saturation. However, this slight saturation bias does not degrade the switching of  $Q_R$ , so the fast-switching characteristic of the ECL circuit is retained.

## **Test Your Understanding**

**D17.6** Design the basic ECL logic gate in Figure 17.11 such that the maximum power dissipation is  $0.2\,\mathrm{mW}$  and the logic swing is  $0.4\,\mathrm{V}$ . (Ans.  $I_Q=118\,\mu\mathrm{A}$ ,  $R_C=3.39\,\mathrm{k}\Omega$ ,  $V_R=1.5\,\mathrm{V}$ )

Figure 17.11 Figure for Exercise 17.6

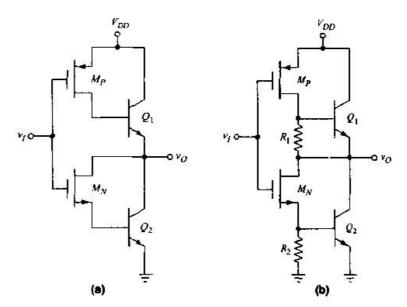

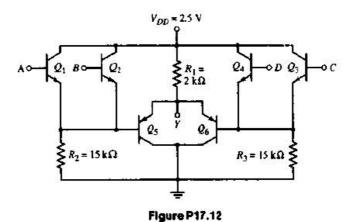

#### 17.2.2 Alternative ECL Gates

In an ECL system, as in all digital systems, a gate is used to drive other logic gates. Connecting load circuits to the basic ECL gate demonstrates changes that can be made to incorporate ECL into integrated circuits more effectively.

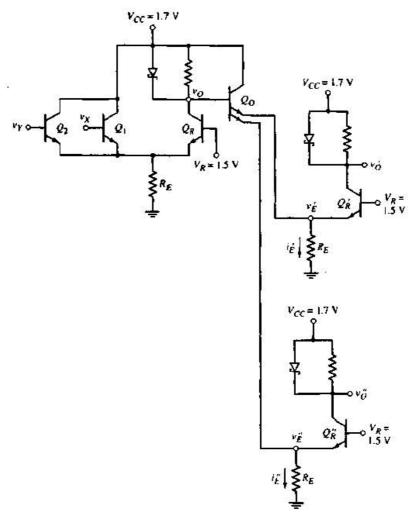

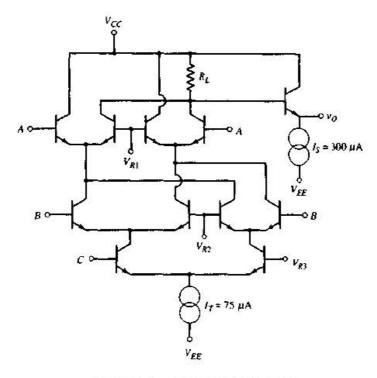

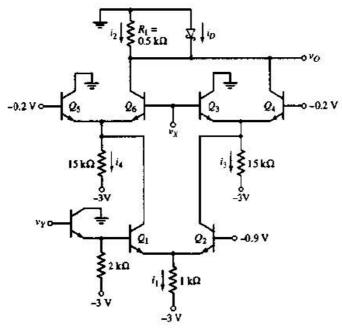

Figure 17.12 shows the basic ECL gate with two load circuits. In this configuration, the collectors of  $Q_2'$  and  $Q_2''$  are at the same potential, as are the bases of the two transistors. We can therefore replace  $Q_2'$  and  $Q_2''$  by a single multiemitter transistor.

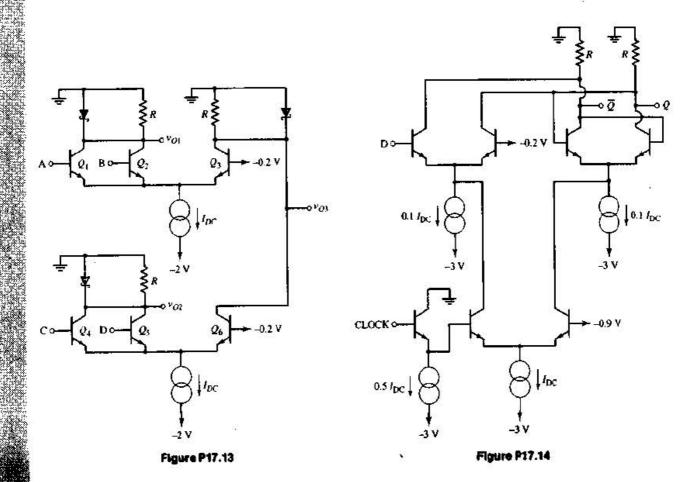

In Figure 17.13, the multiemitter transistor  $Q_0$  is part of the driver circuit. The operation of the circuit is as follows:

- $v_x = v_y = \text{logic } 1 = 1.7 \text{ V}$ : The two input transistors  $Q_1$  and  $Q_2$  are on,  $Q_R$  is off, and  $v_O = 1.7 \text{ V}$ . Since the base voltage of  $Q_O$  is higher than the base voltages of  $Q_R'$  and  $Q_R''$ , then  $Q_O$  is conducting,  $Q_R'$  and  $Q_R''$  are off, and  $v_E' = v_E'' = 1.7 0.7 = 1.0 \text{ V}$ . The currents  $i_E'$  and  $i_E''$  flow through the emitters of  $Q_O$ . The output voltages are  $v_O' = v_O'' = 1.7 \text{ V}$ .

- $v_x = v_y = \text{logic } 0 = 1.3 \,\text{V}$ : For this case, the two input transistors  $Q_1$  and  $Q_2$  are off,  $Q_R$  is on, and  $v_O = 1.3 \,\text{V}$ . The output transistor  $Q_O$  is off and both  $Q_R'$  and  $Q_R''$  are on. The output voltages are then  $v_O' = v_O'' = 1.3 \,\text{V}$ .

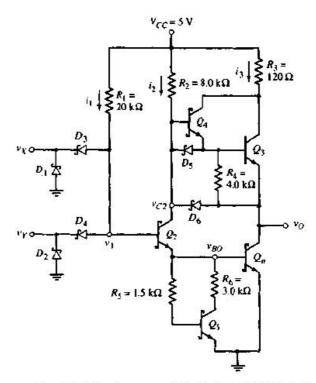

The two load circuits in Figure 17.13 each have only a single input, which limits the circuit functionality. The versatility of the circuit can be further enhanced by making the load transistor  $Q'_R$  a multiemitter transistor. This is shown in Figure 17.14. For simplicity, we show only a single input transistor to each of the two driver circuits. The operation of this circuit for various combinations of input voltages is as follows.

Figure 17.12 Modified ECL logic gate with two load circuits

- $v_1 = v_2 = \text{logic } 0 = 1.3 \text{ V}$ : The two input transistors  $Q_1$  and  $Q_2$  are off and the two reference transistors  $Q_{R1}$  and  $Q_{R2}$  are on. This means that  $v_{O1} = v_{O2} = 1.3 \text{ V}$  and both output transistors  $Q_{O1}$  and  $Q_{O2}$  are off. Both emitters of  $Q_R'$  are forward biased, currents  $i_{E1}$  and  $i_{E2}$  flow through  $Q_R'$ , and the output voltage is  $v_O' = \text{logic } 0 = 1.3 \text{ V}$ .

- $v_1 = 1.7 \text{V}$ ,  $v_2 = 1.3 \text{V}$ : For this case,  $Q_1$  is on,  $Q_{R1}$  is off,  $Q_2$  is off, and  $Q_{R2}$  is on. The output voltages are  $v_{O1} = 1.7 \text{V}$  and  $v_{O2} = 1.3 \text{V}$ . This means that  $Q_{O1}$  is on and  $Q_{O2}$  is off. With  $Q_{O1}$  on, current  $i_{E1}$  flows through  $Q_{O1}$  and no current flows in emitter  $E_1$ . With  $Q_{O2}$  off, emitter  $E_2$  is forward biased, current  $i_{E2}$  flows through  $Q_R$ , and the output voltage is  $v_O' = \log c = 1.3 \text{V}$ .

- $v_1 = 1.3 \,\mathrm{V}$ ,  $v_2 = 1.7 \,\mathrm{V}$ : This case is the complement of the one just discussed. Here,  $Q_{01}$  is off and  $Q_{02}$  is on. This means that  $i_{E1}$  flows through emitter  $E_1$  of  $Q_R'$ , and  $i_{E2}$  flows through  $Q_{02}$ . The output voltage is  $v_O' = \log i_0 = 1.3 \,\mathrm{V}$ .

- $v_1 = v_2 = 1.7 \text{ V}$ : The two input transistors  $Q_1$  and  $Q_2$  are on, the two reference transistors  $Q_{R1}$  and  $Q_{R2}$  are off, and  $v_{O1} = v_{O2} = 1.7 \text{ V}$ . This means that both  $Q_{O1}$  and  $Q_{O2}$  are on and  $Q'_R$  is off. Currents  $i_{E1}$  and  $i_{E2}$  flow through  $Q_{O1}$  and  $Q_{O2}$ , respectively, and the output voltage is  $v'_O = \log c \ 1 = 1.7 \text{ V}$ .

Figure 17.13 Modified ECL logic gate with multiemitter output transistor and two load circuits

These results are summarized in Table 17.1, which shows that this circuit performs the AND logic function. A more complicated or sophisticated logic function can be performed if multiple inputs are used in the driver circuits.

In integrated circuits, resistors  $R_E$  are replaced by current sources using transistors. Replacing resistors with transistors in integrated circuits usually results in reduced chip area.

**Table 17.1** Summary of results for the ECL circuit in Figure 17.14

| ν <sub>1</sub> (V) | r <sub>2</sub> (V) | $v_O'(V)$ |

|--------------------|--------------------|-----------|

| 1.3                | 1.3                | 1.3       |

| 1.7                | 1.3                | 1.3       |

| 1.3                | 1.7                | 1.3       |

| 1.7                | 1.7                | 1.7       |

Figure 17.14 Two ECL driver circuits with a multi-input load circuit

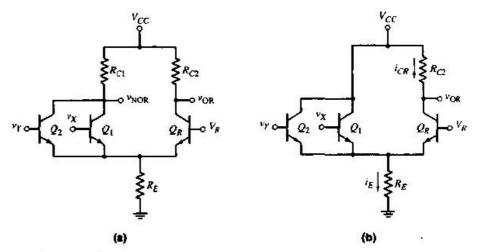

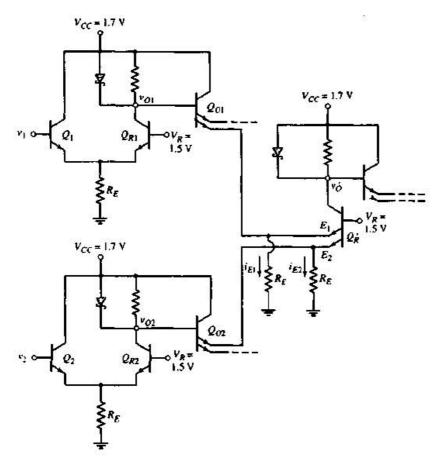

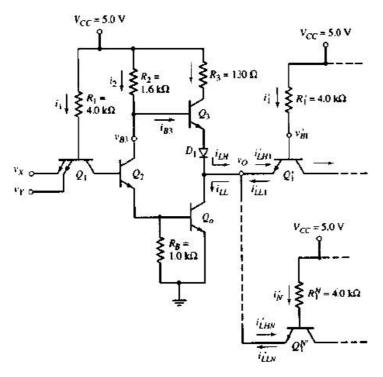

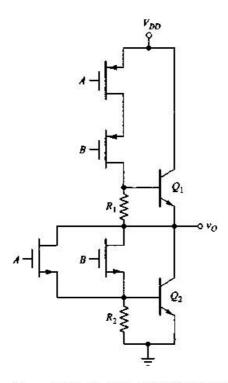

### 17.2.3 Series Gating

Series gating is a bipolar logic circuit technique that allows complex logic functions to be performed with a minimum number of devices and with maximum speed. Series gating is formed by using cascode stages.

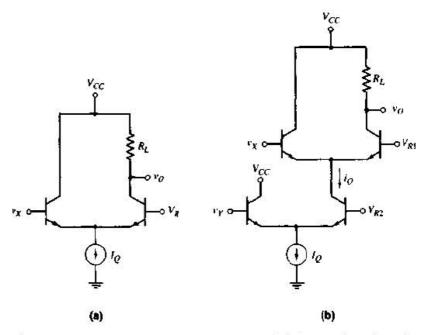

Figure 17.15(a) shows the basic emitter-coupled pair, and Figure 17.15(b) shows a cascode stage, also referred to as two-level series gating. Reference voltage  $V_{R1}$  is approximately 0.7 V greater than reference voltage  $V_{R2}$ . The input voltages  $v_x$  and  $v_y$  must also be shifted approximately 0.7 V with respect to each other.

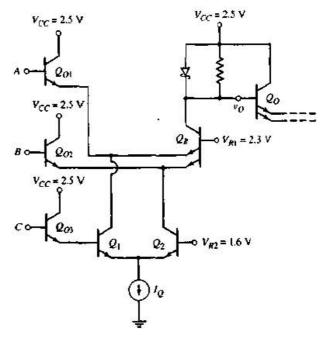

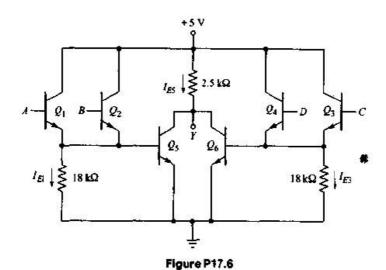

As an example, we use the multiemitter load circuit from Figure 17.14 as part of a cascode configuration as shown in Figure 17.16. Transistors  $Q_{O1}$ ,  $Q_{O2}$ , and  $Q_{O3}$  represent the output transistors of three ECL driver circuits. We assume a logic 1 level of 2.5 V and a logic 0 level of 2.1 V. The 0.4 V logic swing results from incorporating a Schottky diode in each output stage.

With three input signals, there are eight possible combinations of input states. We will only consider two combinations here:

• A = B = C = logic 0 = 2.1 V: In this case, transistors  $Q_{01}$  and  $Q_{02}$  are off and transistor  $Q_1$  is off. This means that current  $I_Q$  flows through  $Q_2$  and  $Q_R$ , and  $v_Q = \text{logic } 0 = 2.1 \text{ V}$ .

Figure 17.15 (a) Basic emitter-coupled pair and (b) ECL cascode configuration

Figure 17.16 ECL series gating example

• A = C = 2.1 V, B = 2.5 V: Transistors  $Q_{O1}$  and  $Q_1$  are off,  $Q_{O2}$  is on, and current  $I_Q$  flows through  $Q_2$  and  $Q_{O2}$ . Since  $Q_1$  is off, no current is available to flow through  $Q_R$ , even though  $Q_{O1}$  is off. The output is  $v_Q = \log i \ 1 = 2.5 \text{ V}$ .

For the output voltage  $v_0$  to be a logic 1, no current must flow through  $Q_R$ . This occurs when both  $Q_{01}$  and  $Q_{02}$  are on, or when a B-E junction of  $Q_R$  is

turned on but no current is available through  $Q_1$  or  $Q_2$ . We can show that this circuit performs the logic function

$$(A \text{ AND } C) \text{ OR } (B \text{ AND } \overline{C})$$

(17.8)

We are now beginning to integrate logic functions into a circuit rather than using separate, distinct logic gates. This reduces the number of devices required, as well as the propagation delay time.

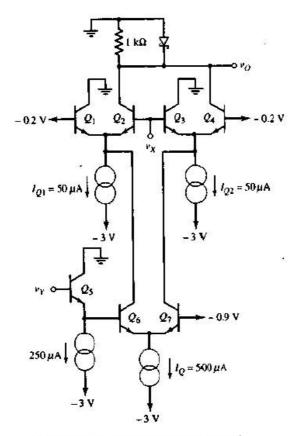

Another example of series gating is shown in Figure 17.17. A negative supply voltage is again used. The operation of the circuit is as follows.

- $v_x = v_y = \text{logic } 0 = -0.4 \text{ V}$ : Transistors  $Q_1$ ,  $Q_4$ , and  $Q_7$  are on, current  $I_Q$  flows through  $Q_7$  and  $Q_4$ , the diode turns on, and the output voltage is -0.4 V.

- $v_x = -0.4 \,\mathrm{V}$ ,  $v_y = 0$ : Transistors  $Q_1$ ,  $Q_4$ , and  $Q_6$  are on, current  $I_Q$  flows through  $Q_6$  and  $Q_1$  to ground, and current  $I_{Q2}$  flows through  $Q_4$  and the resistor. The output voltage is  $v_O = -R_C I_{Q2} = -(1)(0.05) = -0.05 \,\mathrm{V}$ . This voltage is not sufficient to turn the Schottky diode on. Although it is not zero volts, the voltage still represents a logic 1.

- $v_x = 0$ ,  $v_y = -0.4 \text{ V}$ : Transistors  $Q_2$ ,  $Q_3$ , and  $Q_7$  are on, current  $I_Q$  flows through  $Q_7$  and  $Q_3$  to ground, and current  $I_{Q1}$  flows through  $Q_2$  and the resistor. Again,  $v_Q = -0.05 \text{ V} = \text{logic 1}$ .

Figure 17.17 ECL series gating example

•  $v_x = v_y = \text{logic } 1 \cong 0 \text{ V}$ : Transistors  $Q_2$ ,  $Q_3$ , and  $Q_6$  are on,  $I_Q$  flows through  $Q_6$ ,  $Q_2$ , and the Schottky diode, and output voltage is  $v_Q = -0.4 \text{ V} = \text{logic } 0$ .

Table 17.2 Summary of logic levels for ECL circuit in Figure 17.17

| <b>r</b> , | <b>V</b> <sub>3</sub> ; | 40 |

|------------|-------------------------|----|

| 0          | 0                       | 0  |

| 0          | 1                       | 1  |

| t          | 0                       | 1  |

| Ĩ          | 1                       | 0  |

|            |                         |    |

These results are summarized in Table 17.2, in which the logic levels are given. The results show that the circuit performs the exclusive-OR logic function.

# 17.2.4 Propagation Delay Time

ECL is the fastest bipolar logic technology. Bipolar technology can produce small, very fast transistors with cutoff frequencies in the range of 3 to 15 GHz. Logic gates that use these transistors are so fast that interconnect line delays tend to dominate the propagation delay times. Minimizing these interconnect delays involves minimizing the metal lengths and using sufficient current drive capability.

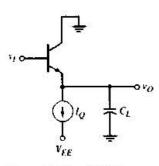

Speed is derived from low-signal logic swings, nonsaturating logic, and the ability to drive a load capacitance. Figure 17.18 is the emitter-follower output stage found in many ECL circuits, showing an effective load capacitance. Usually, the emitter-follower current  $I_Q$  is two to four times larger than the cell current.

In the pull-down cycle, the current  $I_Q$  discharges  $C_L$ . The current-voltage relationship of the capacitor is

$$i = C_L \frac{dv_O}{dt} \tag{17.9(a)}$$

or

$$v_O = \frac{1}{C_L} \int idt \tag{17.9(b)}$$

Assuming  $C_L$  and  $i = I_O$  are constants, the fall time is

$$\tau_F = (0.8) \frac{C_L V_S}{I_O} \quad . \tag{17.10}$$

where  $V_S$  is the logic swing, and the factor (0.8) occurs because  $\tau_F$  is defined as the time required for the output to swing from 10 percent to 90 percent of its final value.

As an example, if  $V_S = 0.4 \,\mathrm{V}$  and  $I_Q = 250 \,\mu\mathrm{A}$ , then for a minimum fall time of  $\tau_F = 0.8 \,\mathrm{ns}$ , the maximum load capacitance is  $C_L(\mathrm{max}) = 0.625 \,\mathrm{pF}$ . This calculation shows that the load capacitance must be minimized to realize short propagation delay times.

Figure 17.18 Emitterfollower stage with load capacitance

## **Test Your Understanding**

17.7 Consider the ECL circuit in Figure 17.16. For each of the eight possible combinations of input states, determine the conduction state (on or off) of each transistor. Verify that this circuit performs the logic function given by Equation (17.8).

Figure 17.19 Figure for Exercise 17.8

**17.8** The ECL circuit in Figure 17.19 is an example of three-level series gating. Determine the logic function that the circuit performs. (Ans.  $(A \oplus B) \oplus C$ )

### 17.3 TRANSISTOR-TRANSISTOR LOGIC

The bipolar inverter is the basic circuit from which most bipolar saturated logic circuits are developed, including diode-transistor logic (DTL) and transistor-transistor logic (TTL). However, the basic bipolar inverter suffers from loading effects. Diode-transistor logic combines diode logic (Chapter 2) and the bipolar inverter to minimize loading effects. Transistor-transistor logic, which evolved directly from DTL, provides reduced propagation delay times, as we will show.

In DTL and TTL circuits, bipolar transistors are driven between cutoff and saturation. Since the transistor is being used essentially as a switch, the current gain is not as important as in amplifier circuits. Typically, for transistors used in these circuits, the current gain is assumed to be in the range of 25 to 50. These transistors need not be fabricated to as tight a tolerance as that of high-gain amplifier transistors.

Table 17.3 lists the piecewise linear parameters used in the analysis of bipolar digital circuits, along with their typical values. Also included is the pn junction diode turn-on voltage  $V_{\gamma}$ . Generally, the B-E voltage increases as the transistor is driven into saturation, since the base current increases. When the transistor is biased in the saturation region, the B-E voltage is  $V_{BE}(\text{sat})$ , where  $V_{BE}(\text{sat}) > V_{BE}(\text{on})$ .

Table 17.3 Piecewise linear parameters for a pn junction diode and npn bipolar transistor

| Parameter             | Value |  |

|-----------------------|-------|--|

| <i>Y</i> .            | 0.7 V |  |

| V <sub>BE</sub> (on)  | 0.7 V |  |

| V <sub>BE</sub> (sat) | 0.8 V |  |

| V <sub>CE</sub> (sat) | 0.1 V |  |

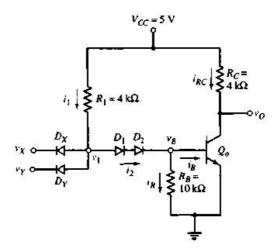

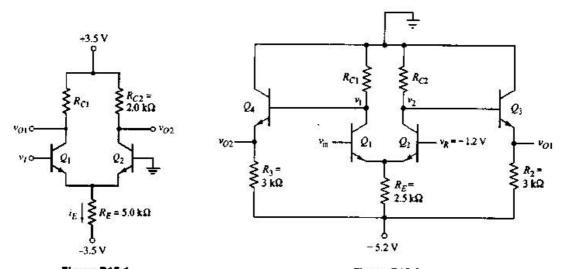

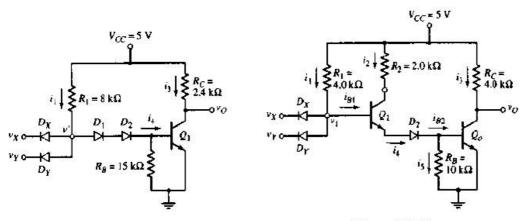

## 17.3.1 Basic Diode—Transistor Logic Gate

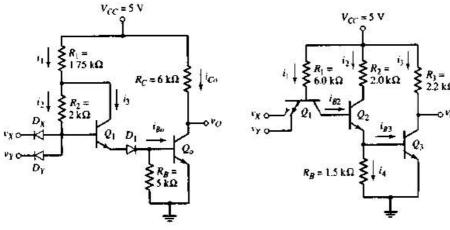

The basic diode-transistor logic (DTL) gate is shown in Figure 17.20. The circuit is designed such that the output transistor operates between cutoff and saturation. This provides the maximum output voltage swing, minimizes loading effects, and produces the maximum noise margins. When  $Q_o$  is in saturation, the output voltage is  $v_O = V_{CE}(\text{sat}) \cong 0.1 \text{ V}$  and is defined as logic 0 for the DTL circuit. As we will see, the basic DTL logic gate shown in Figure 17.20 performs the NAND logic function.

Figure 17.20 Basic diode-transistor logic gate

## Basic DTL NAND Circuit Operation

If both input signals  $v_X$  and  $v_Y$  are at logic 0, then the two input diodes  $D_X$  and  $D_Y$  are forward biased through resistor  $R_1$  and voltage source  $V_{CC}$ . The input diodes conduct, and voltage  $v_1$  is clamped to a value that is one diode drop above the input voltage. If  $v_X = v_Y = 0.1 \text{ V}$  and  $V_Y = 0.7 \text{ V}$ , then  $v_1 = 0.8 \text{ V}$ . Diodes  $D_1$  and  $D_2$  and output transistor  $Q_a$  are nonconducting and are off. If  $D_1$  and  $D_2$  were conducting, then voltage  $v_B$  would be -0.6 V for  $V_Y = 0.7 \text{ V}$ . However, no mechanism exists for  $v_B$  to become negative and still have a forward-biased diode current. Thus, the current in  $D_1$  and  $D_2$ , the current in  $Q_a$ , and the voltage  $v_B$  are all zero. Since  $Q_a$  is cut off, then the output voltage is  $v_O = V_{CC}$ . This is the largest possible output voltage and is therefore defined as the logic 1 level. This same condition applies as long as at least one input is at logic 0.

When both  $v_X$  and  $v_Y$  are at logic 1, which is equal to  $V_{CC}$ , both  $D_X$  and  $D_Y$  are cut off. Diodes  $D_1$  and  $D_2$  become forward biased, output transistor  $Q_o$  is driven into saturation, and  $v_O = V_{CE}(\text{sat})$ , which is the smallest possible output voltage and is defined as the logic 0 level.

This circuit is a two-input DTL NAND logic gate. However, the circuit is not limited to two inputs. Additional input diodes may be included to increase the fan-in.

Example 17.8 Objective: Determine the currents and voltages in the DTL logic circuit.

Consider the DTL circuit in Figure 17.20. Assume the transistor parameters are as given in Table 17.3 and let  $\beta = 25$ .

**Solution:** Let  $v_X = v_Y = \log i c \ 0 = 0.1 \text{ V}$ . For this case,

$$v_1 = v_X + V_y = 0.1 + 0.7 = 0.8 \text{ V}$$

and

$$i_1 = \frac{V_{CC} - v_1}{R_1} = \frac{5 - 0.8}{4} = 1.05 \,\text{mA}$$

Since diodes  $D_1$  and  $D_2$  and output transistor  $Q_0$  are nonconducting, we assume that current  $i_1$  divides evenly between the matched diodes  $D_X$  and  $D_Y$ . In this case, the currents  $i_2 = i_R = i_C = 0$  and the output voltage is  $v_O = 5 \text{ V} = \log i_C 1$ .

If  $v_X = 0.1 \text{ V}$  and  $v_Y = 5 \text{ V}$ , or  $v_X = 5 \text{ V}$  and  $v_Y = 0.1 \text{ V}$ , then the output transistor is still cut off and  $v_Q = 5 \text{ V} = \text{logic } 1$ .

If  $v_X = v_Y = \text{logic } 1 = 5 \text{ V}$ , it is impossible for input diodes  $D_X$  and  $D_Y$  to be forward biased. In this case, diodes  $D_1$  and  $D_2$  and the output transistor are biased on, which means that, starting at ground potential at the emitter of  $Q_0$ ,  $v_1$  is

$$v_1 = V_{BE}(\text{sat}) + 2V_v = 0.8 + 2(0.7) = 2.2 \text{ V}$$

Voltage  $v_1$  is clamped at this value and cannot increase. We see that  $D_X$  and  $D_Y$  are indeed reverse biased and turned off, as assumed.

Currents i, and i2 are

$$i_1 = i_2 = \frac{V_{CC} - v_1}{R_t} = \frac{5 - 2.2}{4} = 0.70 \text{ mA}$$

and current in is

$$i_R = \frac{V_{BE}(\text{sat})}{R_B} = \frac{0.8}{10} = 0.08 \text{ mA}$$

The base current into the output transistor is then

$$i_B = i_2 - i_B = 0.70 - 0.08 = 0.62 \,\mathrm{mA}$$

Since the circuit is to be designed such that  $Q_o$  is driven into saturation, the collector current is

$$i_C = \frac{V_{CC} - V_{CE}(\text{sat})}{R_C} = \frac{5 - 0.1}{4} = 1.23 \text{ mA}$$

Finally, the ratio of collector to base current is

$$\frac{i_C}{i_B} = \frac{1.23}{0.62} = 1.98 < \beta$$

Comment: Since the ratio of the collector current to base current is less than  $\beta$ , the output transistor is biased in the saturation region. Since the output transistor is biased between cutoff and saturation, the maximum swing between logic 0 and logic 1 is obtained.

## **Test Your Understanding**

[Note: In the following exercises, assume the piecewise linear transistor parameters are as listed in Table 17.3.]

**17.9** The DTL circuit in Figure 17.20 has new circuit parameters of  $R_1 = 6 \,\mathrm{k}\,\Omega$ ,  $R_C = 5 \,\mathrm{k}\,\Omega$ , and  $R_B = 15 \,\mathrm{k}\,\Omega$ . Assume  $V_{CC} = 5 \,\mathrm{V}$  and  $\beta = 25$ . Determine  $i_1, i_2, i_R, i_B, i_{RC}$ , and  $v_O$  for: (a)  $v_X = v_Y = 0.1 \,\mathrm{V}$ , (b)  $v_X = 5 \,\mathrm{V}$ ,  $v_Y = 0.1 \,\mathrm{V}$ , and (c)  $v_X = v_Y = 5 \,\mathrm{V}$ . (Ans. (a)  $i_1 = 0.7 \,\mathrm{mA}$ ,  $i_2 = i_R = i_B = i_{RC} = 0$ ,  $v_O = 5 \,\mathrm{V}$  (b) same as part (a) (c)  $i_1 = i_2 = 0.467 \,\mathrm{mA}$ ,  $i_R = 0.053 \,\mathrm{mA}$ ,  $i_B = 0.414 \,\mathrm{mA}$ ,  $i_{RC} = 0.98 \,\mathrm{mA}$ ,  $v_O = 0.1 \,\mathrm{V}$ )

**17.10** Consider the basic DTL circuit in Figure 17.20 with circuit and transistor parameters given in Example 17.8. Assume no load is connected to the output. Calculate the power dissipated in the circuit for (a)  $v_X = v_Y = 5$  V and (b)  $v_X = v_Y = 0$ .

# Minimum $\beta$

To ensure that the output transistor is in saturation, the common-emitter current gain  $\beta$  must be at least as large as the ratio of collector current to base current. For example 17.8, the minimum  $\beta$ , or  $\beta_{\min}$ , is 1.98. If the common-emitter current gain were less than 1.98, then  $Q_o$  would not be driven into saturation, and the currents and voltages in the circuit would have to be recalculated. A current gain greater than 1.98 ensures that  $Q_o$  is driven into saturation for the given circuit parameters and for the no-load condition.

### **Pull-Down Resistor**

In the basic DTL NAND logic circuit in Figure 17.20, a resistor  $R_B$  is connected between the base of the output transistor and ground. This resistor is called a pull-down resistor, and its purpose is to decrease the output transistor switching time as it goes from saturation to cutoff. As previously discussed, excess minority carriers must be removed from the base before a transistor can be switched to cutoff. This base charge removal produces a current out of the transistor base terminal until the transistor is turned off. Without the pull-down resistor, this reverse base current would be limited to the reverse-bias leakage current in diodes  $D_1$  and  $D_2$ , resulting in a relatively long turn-off time. The pull-down resistor provides a path for the reverse base current.

The base charge can be removed more rapidly if the value of  $R_B$  is reduced. The larger the reverse base current, the shorter the transistor turn-off time. However, a trade-off must be made in choosing the value of  $R_B$ . A small  $R_B$  provides faster switching, but lowers the base current to the transistor in the on state by diverting some drive current to ground. A lower base current reduces the circuit drive capability, or maximum fanout.

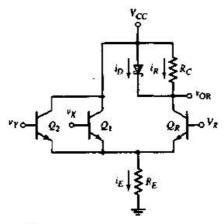

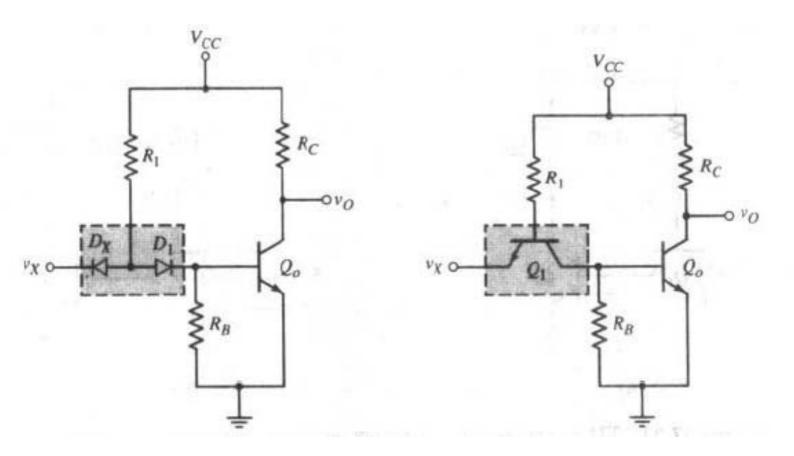

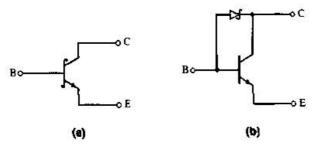

### 17.3.2 The Input Transistor of TTL

Figure 17.21(a) shows a basic DTL circuit with one input diode  $D_X$  and one offset diode  $D_1$ . The structure of these back-to-back diodes is the same as an npn transistor, as indicated in Figure 17.21(b). The base-emitter junction of  $Q_1$  corresponds to input diode  $D_X$  and the base-collector junction corresponds to offset diode  $D_1$ .

(a) (b)

Figure 17.21 (a) Basic DTL gate and (b) basic TTL gate

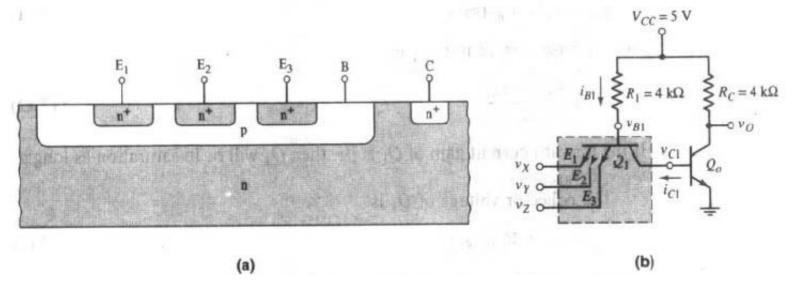

In isoplanar integrated circuit technology, the emitter of a bipolar transistor is fabricated in the base region. More emitters can then be added in the same base region to form a multiemitter, multi-input device. Figure 17.22(a) shows a simplified cross section of a three-emitter transistor, which is used as the input device in a TTL circuit. Figure 17.22(b) shows the basic TTL circuit with the multiemitter input transistor.

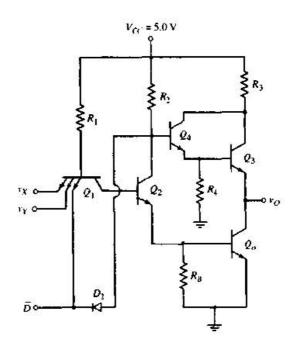

Figure 17.22 (a) Simplified cross section of three-emitter transistor and (b) TTL circuit with three-emitter input transistor

This circuit performs the same NAND operation as its DTL counterpart. The multiemitter transistor reduces the silicon area required, compared to the DTL input diodes, and it increases the switching speed. Transistor  $Q_1$  assists in pulling output transistor  $Q_0$  out of saturation and into cutoff during a low-to-high transition of the output voltage. Pull-down resistor  $R_B$  in Figure 17.21(b) is no longer necessary, since the excess minority carriers in the base of  $Q_0$  use transistor  $Q_1$  as a path to ground.

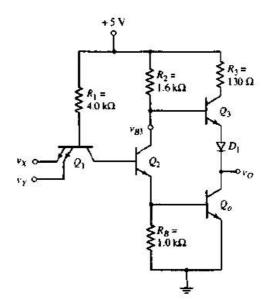

Figure 17.23 TTL circuit (a) with at least one input low and (b) with all inputs high

The operation of input transistor  $Q_1$  is somewhat unconventional. In Figure 17.23(a), if either or both of the two inputs to  $Q_1$  are in a low state, the base-emitter junction is forward biased through  $R_1$  and  $V_{CC}$ . The base current enters  $Q_1$ , and the emitter current exits the specific emitter connected to the low input. Transistor action forces the collector current into  $Q_1$ , but the only steady-state collector current in this direction is a reverse-bias saturation current out of the base of  $Q_0$ . The steady-state collector current of  $Q_1$  is usually much smaller than the base current, implying that  $Q_1$  is biased in saturation.

If at least one input is low such that  $Q_1$  is biased in saturation, then from Figure 17.23(a), we see that the base voltage of  $Q_1$  is

$$v_{B1} = v_X + V_{BE}(\text{sat}) \tag{17.11}$$

and the base current into  $Q_1$  is

$$i_{B1} = \frac{V_{CC} - v_{B1}}{R_1} \tag{17.12}$$

If the forward current gain of  $Q_1$  is  $\beta_F$ , then  $Q_1$  will be in saturation as long as  $i_{C1} < \beta_F i_{B1}$ .

The collector voltage of  $Q_i$  is

$$v_{C1} = v_X + V_{CE}(\text{sat}) \tag{17.13}$$

If both  $v_X$  and  $V_{CE}(\text{sat})$  are approximately 0.1 V, then  $v_{Cl}$  is small enough for the output transistor to cut off and  $v_0 = V_{CC} = \text{logic } 1$ .

If all inputs are high,  $v_X = v_Y = 5 \text{ V}$ , as shown in Figure 17.23(b), then the base-emitter junctions of the input transistor are reverse biased. Base voltage  $v_{B|}$  increases, which forward-biases the B-C junction of  $Q_1$  and drives output transistor  $Q_0$  into saturation. Since the B-E junction of  $Q_1$  is reverse biased and the B-C junction is forward biased,  $Q_1$  is biased in the inverse-active mode. In this bias mode, the roles of the emitter and collector are interchanged.

When input transistor  $Q_1$  is biased in the inverse-active mode, base voltage  $v_{B1}$  is

$$v_{B1} = V_{BE}(\text{sat})_{Q_n} + V_{BC}(\text{on})_{Q_1}$$

(17.14)

where  $V_{BC}(\text{on})$  is the B-C junction turn-on voltage. We assume that the B-C junction turn-on voltage is equal to the B-E junction turn-on voltage. The terminal current relationships for  $Q_1$  are therefore

$$i_{EX} = i_{EY} = \beta_R i_{B1}$$

(17.15)

and

$$i_{C1} = i_{B1} + i_{EV} + i_{EY} = (1 + 2\beta_R)i_{B1}$$

(17.16)

where  $\beta_R$  is the inverse-active mode current gain of each input emitter of the input transistor.

Since a bipolar transistor is not symmetrical, the inverse and forward current gains are not equal. The inverse current gain is generally quite small, usually less than one. In Figure 17.23(b), the input transistor has a fan-in of two. Transistor  $Q_1$  may be considered as two separate transistors with their bases and collectors connected. For simplicity, when all inputs are high, we assume that current  $i_{ER}$  splits evenly between the input emitters.

The inverse-active mode current into the emitters of  $Q_1$  is not desirable, since this is a load current that must be supplied by a driver logic circuit when its output voltage is in its high state. Because of the transistor action, these currents tend to be larger than the reverse saturation currents of DTL circuit input diodes. The major advantage of TTL over DTL is faster switching of the output transistor from saturation to cutoff.

If all inputs are initially high and then at least one input switches to the logic 0 state, 0.1 V, the B-E junction of  $Q_1$  becomes forward biased and base voltage  $v_{B1}$  becomes approximately 0.1 + 0.7 = 0.8 V. Collector voltage  $v_{C1}$  is held at 0.8 V as long as output transistor  $Q_0$  remains in saturation. At this instant in time,  $Q_1$  is biased in the forward-active mode. A large collector current into  $Q_1$  can exist, which pulls the excess minority carrier charge out of the base of  $Q_0$ . A large reverse base current from  $Q_0$  will very quickly pull the output transistor out of saturation. In the TTL circuit, the action of the input transistor reduces the propagation delay time compared to that of DTL logic circuits. For example, the propagation delay time is reduced from approximately 40 ns in a DTL NAND gate to approximately 10 ns in an equivalent TTL circuit.

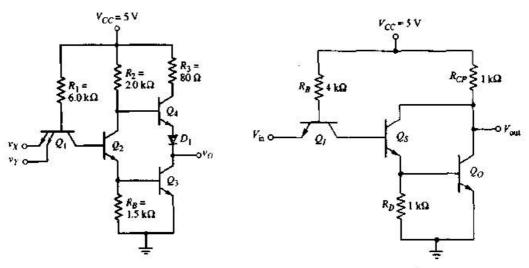

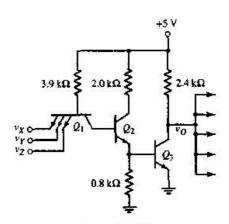

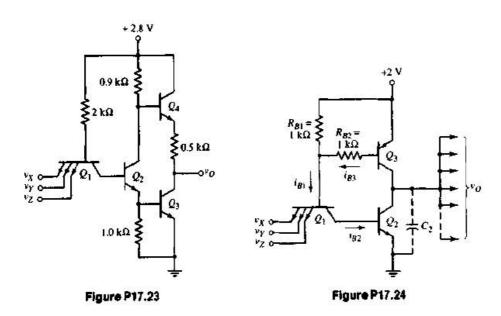

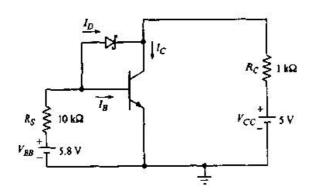

### 17.3.3 Basic TTL NAND Circuit

We can improve the circuit performance of the simple TTL circuit in Figure 17.23 by adding a second current gain stage. The resulting basic TTL NAND circuit is shown in Figure 17.24. In this circuit, both transistors  $Q_2$  and  $Q_o$  are driven into saturation when  $v_X = v_Y = \log c$ . When at least one input switches from high to low, input transistor  $Q_1$  very quickly pulls  $Q_2$  out of saturation and pull-down resistor  $R_B$  provides a path for the excess charge in  $Q_o$ , which means that the output transistor can turn off fairly quickly.