A KVL equation around the B-E loop produces

$$V_{cm} = \left(\frac{V_{\pi}}{r_{\pi}/2}\right) \left(\frac{R_B}{2}\right) + V_{\pi} + \left(\frac{V_{\pi}}{r_{\pi}/2} + 2g_m V_{\pi}\right) \left[R_o \left\| \left(\frac{1}{sC_o}\right)\right\| \right]$$

(11.115(a))

or

$$V_{cm} = V_{\pi} \left\{ \frac{R_B}{r_{\pi}} + 1 + 2 \left( \frac{1+\beta}{r_{\pi}} \right) \left( \frac{R_o}{1 + sR_oC_o} \right) \right\}$$

(11.115(b))

Solving for  $V_{\pi}$  and substituting the result into Equation (11.114) yields the common-mode gain, which is

$$A_{cm} = \frac{V_o}{V_{cm}} = \frac{-g_m R_C}{\frac{R_B}{r_a} + 1 + \frac{2(1+\beta)}{r_a} \left(\frac{R_o}{1 + sR_oC_o}\right)}$$

(11.116(a))

OΓ

$$A_{cm} = \frac{-g_m R_C (1 + s R_o C_o)}{\left(1 + \frac{R_B}{r_\pi}\right) (1 + s R_o C_o) + \frac{2(1 + \beta) R_o}{r_\pi}}$$

(11.116(b))

Equation (11.116(b)) shows that there is a zero in the common-mode gain. To explain, capacitor  $C_o$  is in parallel with  $R_o$ , and it acts as a bypass capacitor. At very low frequency,  $C_o$  is effectively an open circuit and the common-mode signal "sees"  $R_o$ . As the frequency increases, the impedance of the capacitor decreases and  $R_o$  is effectively bypassed; hence, the zero in Equation (11.116(b)). The frequency analysis of an emitter bypass capacitor also showed the presence of a zero in the voltage gain expression.

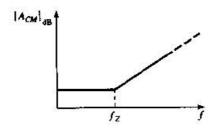

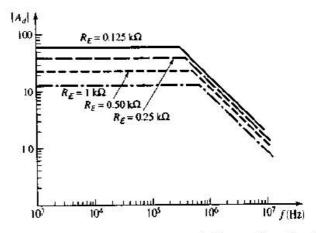

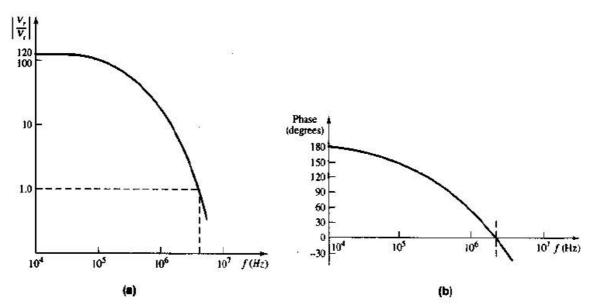

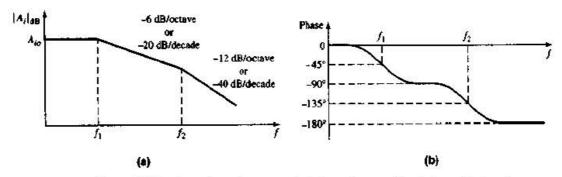

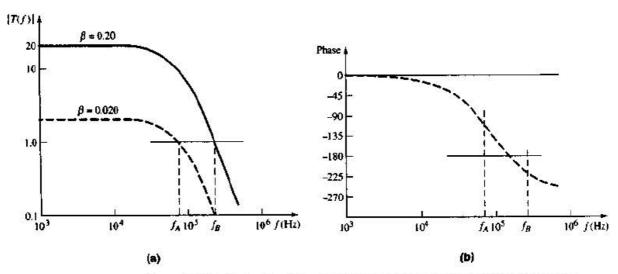

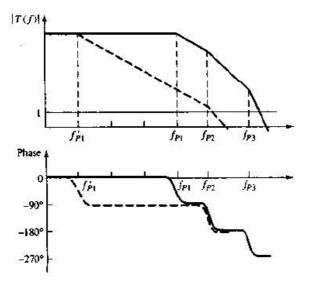

The common-mode gain frequency response is shown in Figure 11.51. The frequency of the zero is

$$f_z = \frac{1}{2\pi R_a C_a} \tag{11.117}$$

Figure 11.51 Frequency response of common-mode gain

Since the output resistance  $R_o$  of a constant-current source is normally large, a small capacitance  $C_o$  can result in a small  $f_z$ . For frequencies greater than  $f_z$ , the common-mode gain increases at the rate of 6 dB/octave.

Equation (11.116(b)) also shows that there is a pole associated with the common-mode gain. Rearranging the terms in that equation, we see that the frequency of the pole is

$$f_p = \frac{1}{2\pi R_{eq} C_o} {(11.118)}$$

where

$$R_{eq} = \frac{R_o \left( 1 + \frac{R_B}{r_\pi} \right)}{1 + \frac{R_B}{r_\sigma} + \frac{2(1+\beta)R_o}{r_\pi}}$$

(11.119)

The denominator of Equation (11.119) is very large, because of the term  $(1+\beta)R_o$ . This implies that  $R_{eq}$  is small, which means that the frequency  $f_p$  of the pole is very large.

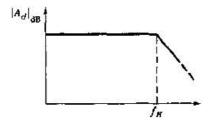

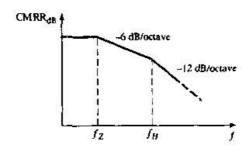

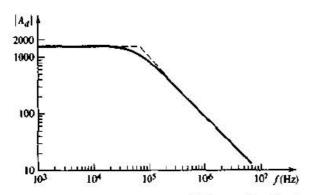

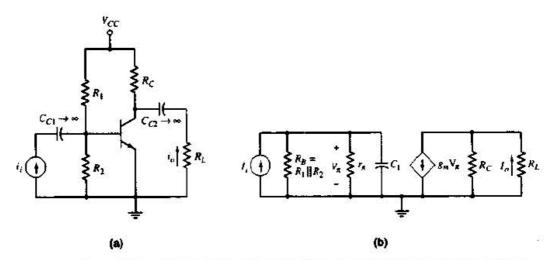

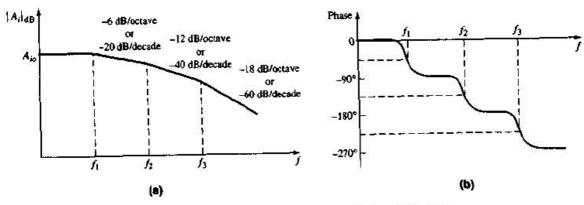

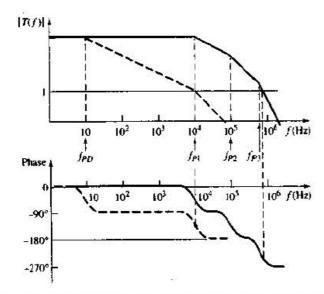

The differential-mode gain is shown in Figure 11.52. The frequency response of the common-mode rejection ratio is found by combining Figures 11.51 and 11.52, and is shown in Figure 11.53.

Figure 11.52 Frequency response of differential-mode gain

Figure 11.53 Frequency response of common-mode rejection ratio

Example 11.20 Objective: Determine the zero and pole frequencies in the common-mode gain.

Consider a diff-amp biased with a constant-current source. The output resistance is  $R_0=10\,\mathrm{M}\Omega$  and the output capacitance is  $C_0=1\,\mathrm{pF}$ . Assume the circuit and transistor parameters are  $R_B=0.5\,\mathrm{k}\Omega$ ,  $r_\pi=10\,\mathrm{k}\Omega$ , and  $\beta=100$ .

Solution: In the common-mode gain, the frequency of the zero is

$$f_z = \frac{1}{2\pi R_o C_o} = \frac{1}{2\pi (10 \times 10^6)(1 \times 10^{-12})} \Rightarrow 15.9 \text{ kHz}$$

Also in the common-mode gain, the frequency of the pole is

$$f_F = 1/(2\pi R_{eq}C_e)$$

where

$$R_{eq} = \frac{R_o \left( 1 + \frac{R_B}{r_\pi} \right)}{1 + \frac{R_B}{r_\pi} + \frac{2(1 + \beta)R_o}{r_\pi}} = \frac{(10 \times 10^6) \left( 1 + \frac{0.5}{10} \right)}{1 + \frac{0.5}{10} + \frac{2(101)(10 \times 10^6)}{10 \times 10^3}}$$

or

$$R_{eq} = 51.98 \,\Omega$$

The frequency of the pole is therefore

$$f_P = \frac{1}{2\pi(51.98)(1 \times 10^{-12})} \Rightarrow 3.06 \,\text{GHz}$$

**Comment:** The frequency of the zero in the common-mode gain is fairly low, while the frequency of the pole is extremely large. The relatively low frequency of the zero justifies neglecting the effect of  $C_{\pi}$  and  $C_{\mu}$ . The CMRR frequency response is shown in Figure 11.53, where  $f_{\pi}$  is the zero frequency of the common-mode gain and  $f_{H}$  is the upper 3 dB frequency of the differential-mode gain.

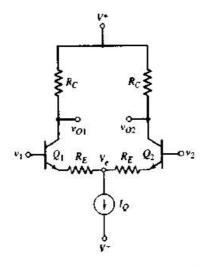

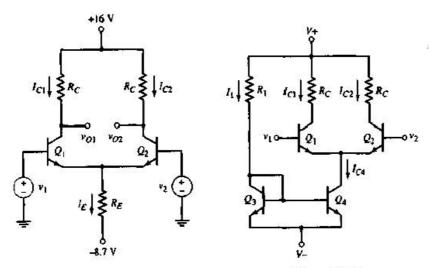

# 11.8.3 With Emitter-Degeneration Resistors

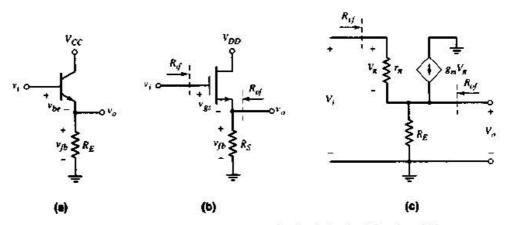

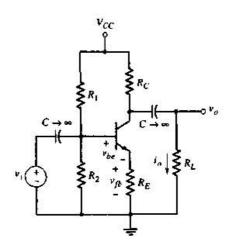

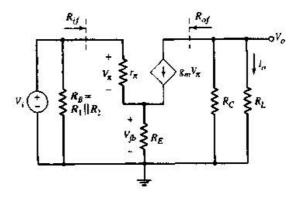

Figure 11.54 shows a bipolar diff-amp with two resistances  $R_E$  connected in the emitter portion of the circuit. One effect of including an emitter resistor is to reduce the voltage gain, so the presence of these resistors is termed emitter degeneration.

In Chapter 7, we found that an emitter-follower circuit, which includes an emitter resistance, is a wide-bandwidth amplifier. Therefore, one effect of

Figure 11.54 BJT differential amplifier with emitter-degeneration resistors

resistors  $R_E$  is an increase in the bandwidth of the differential amplifier. We rely on a computer simulation to evaluate emitter degeneration effects.

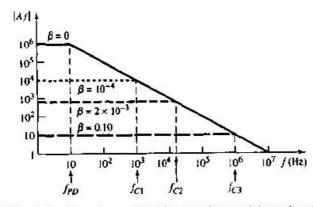

Figure 11.55 shows the frequency response of a one-sided differential-mode gain, obtained from a PSpice analysis for four  $R_E$  resistance values. The diff-amp is biased at  $I_Q=0.5\,\mathrm{mA}$  and the  $R_C$  resistors are  $R_C=30\,\mathrm{k}\Omega$ . The transistor capacitances are  $C_\pi=34.6\,\mathrm{pF}$  and  $C_\mu=4.3\,\mathrm{pF}$ . As the emitter degeneration increases, the differential-mode voltage gain decreases, but the bandwidth increases, as previously indicated. The figure-of-merit for amplifiers, the gain-bandwidth product, is approximately a constant for the results shown in Figure 11.55.

Figure 11.55 PSpice results for frequency response of diff-amp with emitter-degeneration

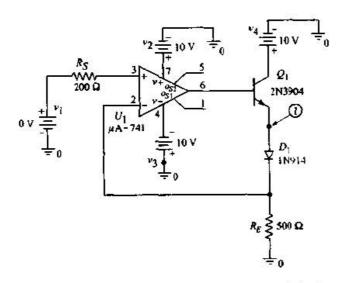

#### 11.8.4 With Active Load

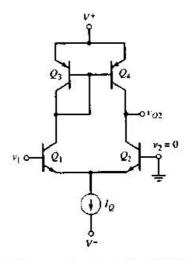

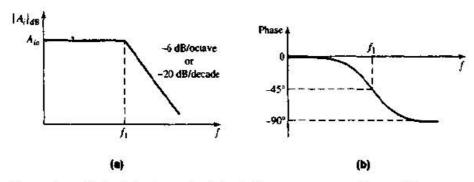

Figure 11.56 shows a bipolar diff-amp with an active load and a single input at  $v_1$ . The base and collector junctions of  $Q_3$  are connected together, and a one-sided output is taken at  $v_{02}$ .

Figure 11.56 BJT diff-amp with active load and single-sided input signal

With the connection of  $Q_3$ , the equivalent load resistance in the collector of  $Q_1$  is on the order of  $r_\pi/(1+\beta)$ . This small resistance minimizes the Miller multiplication factor in  $Q_1$ . Also, with the base of  $Q_2$  at ground potential, one side of  $C_{\mu 2}$  is grounded, and the Miller multiplication in  $Q_2$  is zero. Therefore, we expect the bandwidth of the diff-amp with an active load to be relatively wide. At high frequencies, however, the effective impedance in the collector of  $Q_1$  also includes the input capacitances of  $Q_3$  and  $Q_4$ . These additional capacitances also affect the frequency response of the diff-amp, potentially narrowing the bandwidth.

Again, we rely on a computer analysis to determine the frequency characteristics of the diff-amp with an active load. Figure 11.57 shows the results of the computer simulation. The diff-amp is biased at  $I_Q=0.5\,\mathrm{mA}$ , and the Early voltage of each transistor is assumed to be 80 V. The transistor capacitances are  $C_\pi=34.6\,\mathrm{pF}$  for each transistor,  $C_\mu=3.8\,\mathrm{pF}$  in  $Q_1$  and  $Q_2$ , and  $C_\mu=7\,\mathrm{pF}$  and 5.5 pF in  $Q_3$  and  $Q_4$ , respectively.

Figure 11.57 PSpice results for frequency response of diff-amp with active load and singlesided input signal

The low-frequency voltage gain is 1560 and the upper 3dB frequency is 64 kHz. The large gain is as expected for an active load amplifier, but the 3dB frequency is lower than expected. However, the gain-bandwidth product for the active load diff-amp is approximately four times that of the diff-amp shown in Figure 11.54. The increased gain-bandwidth product implies a reduced Miller multiplication factor in the active load diff-amp, as predicted.

#### 11.9 SUMMARY

- The ideal differential amplifier amplifies only the difference between two input signals.

- The differential-mode input voltage is defined as the difference between the two input signals and the common-mode input voltage is defined as the average of the two input signals.

- When a differential input voltage is applied, one transistor of the differential pair turns on more than the second transistor of the differential pair so that the currents become unbalanced, producing a signal output voltage.

- A common-mode output signal is generated because of a finite output resistance of the current source.

- The common-mode rejection ratio, CMRR, is defined in terms of decibels as  $CMRR_{dB} = 20 \log_{10} |A_d/A_{cm}|$ , where  $A_d$  and  $A_{cm}$  are the differential-mode voltage gain and common-mode voltage gain, respectively.

- Differential amplifiers are usually designed with active loads to increase the differential-mode voltage gain.

- BiCMOS circuits may be designed to incorporate the best parameters and characteristics of BJTs and MOSFETs in the same circuit.

- A BJT Darlington pair is typically used as a second stage to a BJT diff-amp. The

input impedance is large, which tends to minimize loading effects on the diff-amp,

and the effective current gain of the pair is the product of the individual gains.

#### CHECKPOINT

After studying this chapter, the reader should have the ability to:

- ✓ Describe the mechanism by which a differential-mode signal and common-mode signal are produced in a BJT diff-amp. (Section 11.2)

- Describe the dc transfer characteristics of a BJT diff-amp. (Section 11.2)

- ✔ Define common-mode rejection ratio. (Section 11.2)

- ✓ Describe the mechanism by which a differential-mode signal and common-mode signal are produced in a MOSFET diff-amp. (Section 11.3)

- Describe the dc transfer characteristics of a MOSFET diff-amp. (Section 11.3)

- Design a MOSFET diff-amp with an active load to yield a specified differential-mode voltage gain. (Section 11.4)

- ✓ Analyze BiCMOS circuits. (Section 11.5)

- ✓ Analyze a simplified BJT operational amplifier circuit. (Section 11.7)

#### **REVIEW QUESTIONS**

- Define differential-mode and common-mode input voltages.

- 2. Sketch the de transfer characteristics of a BJT differential amplifier.

- From the dc transfer characteristics, qualitatively define the linear region of operation for a differential amplifier.

- 4. What is meant by matched transistors?

- 5. Explain how a differential-mode output signal is generated.

- 6. Explain how a common-mode output signal is generated.

- 7. Define the common-mode rejection ratio, CMRR. What is the ideal value?

- 8. What design criteria will yield a large value of CMRR in an emitter-coupled pair?

- Sketch the differential-mode and common-mode half-circuit models for an emittercoupled diff-amp.

- 10. Define differential-mode and common-mode input resistances.

- 11. Sketch the dc transfer characteristics of a MOSFET differential amplifier.

- 12. Sketch and describe the advantages of a MOSFET cascode current source used with a MOSFET differential amplifier.

- 13. Sketch a simple MOSFET differential amplifier with an active load.

- 14. Explain the advantages of an active load.

- Sketch and describe the advantages of a MOSFET cascode active load with a MOSFET differential pair.

- Discuss one advantage of a BiCMOS circuit.

- 17. Describe the effect of connecting a second stage to the output of the diff-amp on the differential-mode voltage gain of the first stage.

- 18. Explain the frequency response of the differential-mode voltage gain.

- 19. Sketch a BJT Darlington pair circuit and explain the advantages.

- 20. Describe the three stages of a simple BJT operational amplifier.

#### **PROBLEMS**

#### Section 11.2 Basic BJT Differential Pair

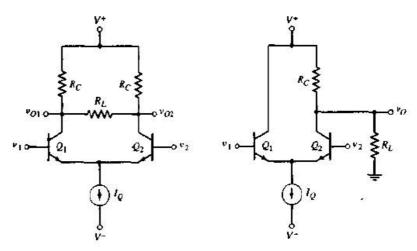

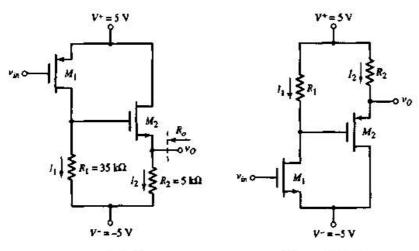

**RD11.1** Consider the differential amplifier shown in Figure P11.1, with transistor parameters:  $\beta = 200$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . (a) Redesign the circuit such that the Q-point values are  $I_{C1} = I_{C2} = 2.0 \text{ mA}$  and  $V_{O2} = 8 \text{ V}$  when  $v_1 = v_2 = 0$ . (b) Draw the dc load line and plot the Q-point for transistor  $Q_2$ . (c) What are the maximum and minimum values of the common-mode input voltage?

Figure P11.1

Figure P11.2

D11.2 The diff-amp configuration shown in Figure P11.2 is biased at  $\pm 3$  V. The maximum power dissipation in the entire circuit is to be no more than 1.2 mW when  $v_1 = v_2 = 0$ . The available transistors have parameters:  $\beta = 120$ ,  $V_{BE}(\text{on}) = 0.7$  V, and  $V_A = \infty$ . Design the circuit to produce the maximum possible differential-mode voltage gain, but such that the common-mode input voltage can be within the range  $-1 \le v_{CM} \le 1$  V and the transistors are still biased in the forward-active region. What is the value of  $A_d$ ? What are the current and resistor values?

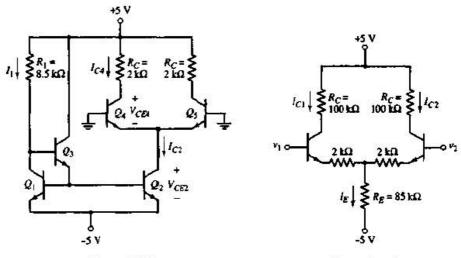

11.3 The differential amplifier in Figure P11.3 is biased with a three-transistor current source. The transistor parameters are:  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . (a) Determine  $I_1$ ,  $I_{C2}$ ,  $I_{C4}$ ,  $V_{CE2}$ , and  $V_{CE4}$ . (b) Determine a new value of  $R_1$  such that  $V_{CE4} = 2.5 \text{ V}$ . What are the values of  $I_{C4}$ ,  $I_{C2}$ ,  $I_{11}$ , and  $I_{12}$ ?

11.4 Consider the circuit in Figure P11.4, with transistor parameters:  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . (a) For  $v_1 = v_2 = 0$ , find  $I_{C1}$ ,  $I_{C2}$ ,  $I_E$ ,  $V_{CE1}$ , and  $V_{CE2}$ . (b) Determine the maximum and minimum values of the common-mode input voltage.

(c) Calculate  $A_d$  for a one-sided output at the collector of  $Q_2$ .

Figure P11.3

Figure P11.4

11.5 Consider the differential amplifier in Figure P11.5. Neglect base currents, assume  $V_A = \infty$  for all transistors, and let  $I_O = 2 \text{ mA}$ . The emitter currents can be written as

$$I_{E1} = I_{S1} e^{V_{BE1}/V_T}$$

and  $I_{E2} = I_{S2} e^{V_{BE2}/V_T}$

(a) If  $v_1 = v_2 = 0$  and  $I_{S1} = I_{S2} = 1 \times 10^{-13} \,\text{A}$ , find  $(v_{o1} - v_{o2})$  when: (i)  $R_{C1} = R_{C2} \approx 8 \,\text{k}\Omega$ , and (ii)  $R_{C1} = 8 \,\text{k}\Omega$ ,  $R_{C2} = 7.9 \,\text{k}\Omega$ . (b) Repeat part (a) if  $I_{S1} = 1 \times 10^{-13} \,\text{A}$  and  $I_{S2} = 1.1 \times 10^{-13} \,\text{A}$ .

Figure P11.5

11.6 For the diff-amp in Figure 11.2, determine the value of  $v_d = v_1 - v_2$  that produces  $i_{C2} = 0.90I_Q$ .

\*RD11.7 The diff-amp for the experimental system described in Example 11.4 needs to be redesigned. The range of the output voltage has increased to  $-2 \le V_O \le 2$  While the differential-mode voltage gain is still  $A_d = 100$ . The common-mode input voltage has increased to  $v_{CM} = 3.5$  V. The value of CMRR needs to be increased to 80 dB.

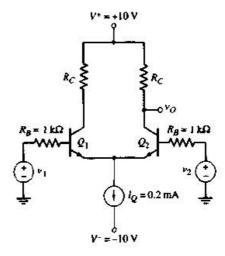

\*11.8 The transistor parameters for the circuit in Figure P11.8 are:  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . (a) Determine  $R_E$  such that  $I_E = 150 \,\mu\text{A}$ . (b) Find  $A_d$ ,  $A_{cm}$ , and CMRR<sub>dB</sub> for a one-sided output at  $v_{O2}$ . (c) Determine the differential- and common-mode input resistances.

Figure P11.8

Figure P11.10

\*11.9 The transistor parameters for the circuit in Figure P11.8 are:  $\beta = 120$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . (a) Determine  $R_E$  such that  $I_E = 0.25 \text{ mA}$ . (b) Assume the  $R_B$  resistance connected to the base of  $Q_1$  is zero while the  $R_B$  resistance connected to the base of  $Q_1$  remains at 0.5 k $\Omega$ . (i) Determine the differential-mode voltage gain for a one-sided output at  $v_{O2}$ . (ii) Determine the common-mode voltage gain for a one-sided output at  $v_{O2}$ .

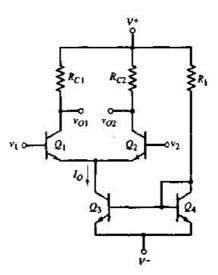

\*RD11.10 For the transistors in the circuit in Figure P11.10, the parameters are  $\beta=100$  and  $V_{BE}(\text{on})=0.7\,\text{V}$ . The Early voltage is  $V_A=\infty$  for  $Q_1$  and  $Q_2$ , and is  $V_A=50\,\text{V}$  for  $Q_3$  and  $Q_4$ . (a) Redesign resistor values such that  $I_3=400\,\mu\text{A}$  and  $V_{CE1}=V_{CE2}=10\,\text{V}$ . (b) Find  $A_d$ ,  $A_{cm}$ , and CMRR<sub>dB</sub> for a one-sided output at  $v_{O2}$ . (c) Determine the differential- and common-mode input resistances.

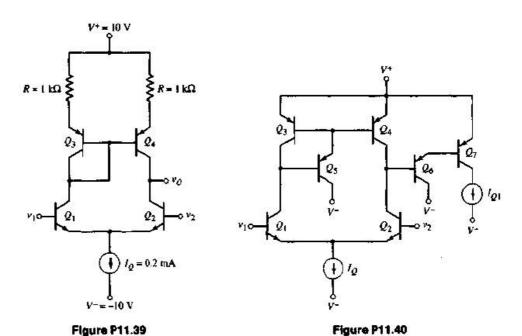

\*11.12 Consider the circuit in Figure P11.12. Assume the Early voltage of  $Q_1$  and  $Q_2$  is  $V_A = \infty$ , and assume the current source  $I_Q$  is ideal. Derive the expressions for the one-sided differential-mode gain  $A_{v1} = v_{o1}/v_d$  and  $A_{v2} = v_{o2}/v_d$ , and for the two-sided differential-mode gain  $A_d = (v_{o2} - v_{o4})/v_d$ .

11.13 The Early voltage of transistors  $Q_1$  and  $Q_2$  in the circuit in Figure P11.13 is  $V_A = \infty$ . Assuming an ideal current source  $I_Q$ , derive the expression for the differential-mode gain  $A_d = v_O/v_d$ .

Figure P11.12

Figure P11.13

\*11.14 Consider the small-signal equivalent circuit of the differential-pair configuration shown in Figure 11.8. Derive the expressions for the differential- and common-mode voltage gains if the output is a two-sided output defined as  $V_o = V_{c2} - V_{c1}$ .

\*D11.15 Consider a BJT diff-amp with the configuration in Figure P11.15. The signal sources have nonzero source resistances as shown. The transistor parameters are:  $\beta = 150$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . The range of the common-mode input voltage is to be  $-3 \le v_{CM} \le 3 \text{ V}$  and the CMRR is to be 75dB. (a) Design the diff-amp to produce the maximum possible differential-mode voltage gain. (b) Design the current source to produce the desired bias current and CMRR.

Figure P11.15

11.16 A diff-amp has a differential-mode voltage gain of 180 and a CMRR of 85 dB. A differential-mode input signal of  $v_d = 2 \sin \omega t \, mV$  is applied, along with a common-mode voltage of  $V_{cm} = 2 \sin \omega t \, V$ . Determine the ideal output voltage and the actual output voltage.

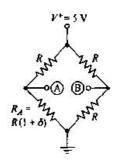

\*11.17 The bridge circuit in Figure P11.17 is a temperature transducer in which the resistor  $R_A$  is a thermistor (a resistor whose resistance varies with temperature). The value of  $\delta$  varies over the range of  $-0.01 \le \delta \le 0.01$  as temperature varies over a particular range. Assume the value of  $R = 10 \,\mathrm{k}\Omega$ . The bridge circuit is to be connected to the diff-amp in Figure 11.2. The transistor parameters are:  $\beta = 120$ ,  $V_{BE}(\mathrm{on}) = 0.7 \,\mathrm{V}$ , and  $V_A = \infty$ . The circuit parameters are:  $I_Q = 0.5 \,\mathrm{mA}$ ,  $R_C = 3 \,\mathrm{k}\Omega$ , and dc bias voltages  $= \pm 5 \,\mathrm{V}$ . Terminal A of the bridge circuit is connected to the base of  $Q_1$  and terminal B is connected to the base of  $Q_2$ . Determine the range of output voltage  $v_{O2}$  as  $\delta$  changes. [Hint: Make a Thevenin equivalent circuit at terminals A and B of the bridge circuit.]

11.18 A diff-amp is biased with a constant-current source  $I_Q = 0.4 \,\mathrm{mA}$ , for which the output resistance is  $R_o = 1 \,\mathrm{M}\Omega$ . The bipolar transistor parameters are  $\beta = 180$  and  $V_A = 125 \,\mathrm{V}$ . Determine: (a) the differential-mode input resistance, and (b) the common-mode input resistance.

**D11.19** The transistor parameters for the circuit shown in Figure P11.19 are:  $\beta = 180$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$  at 1 mA, and  $V_A = 100 \text{ V}$ . (a) Determine  $R_1$  and  $R_2$  such that  $I_1 = 1 \text{ mA}$  and  $I_Q = 100 \mu\text{A}$ . (b) Determine the common-mode input resistance. (c) For  $R_C = 50 \text{ k}\Omega$ , determine the common-mode voltage gain.

Figure P11.17

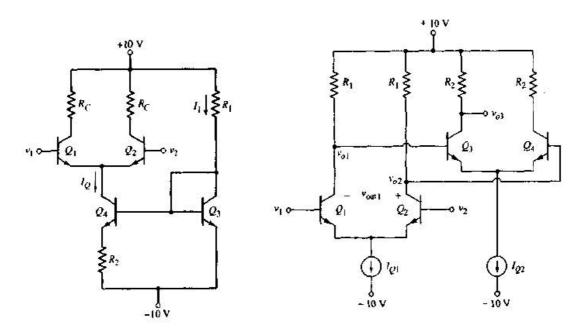

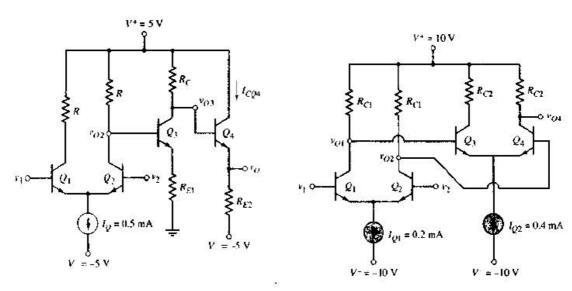

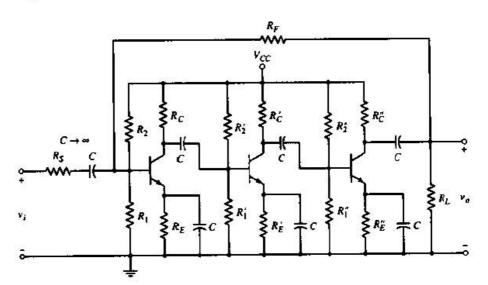

**D11.20** Figure P11.20 shows a two-stage cascade diff-amp with resistive loads. Power supply voltages of  $\pm 10 \, \text{V}$  are available. Assume transistor parameters of:  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \, \text{V}$ , and  $V_A = \infty$ . Design the circuit such that the two-sided differential-mode voltage gain is  $A_{d1} = (v_{o1} - v_{o1})/(v_1 - v_2) = 20$  for the first stage, and that the one-sided differential-mode voltage gain is  $A_{d2} = v_{o3}/(v_{o2} - v_{o1}) = 30$  for the second stage. The circuit is to be designed such that the maximum differential-mode voltage swing is obtained in each stage.

Figure P11.19

Figure P11.20

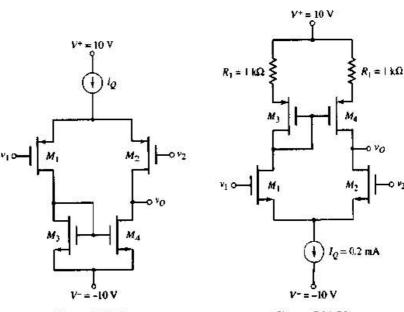

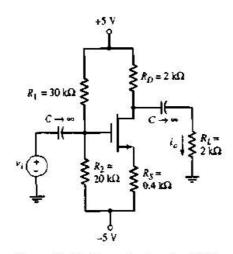

#### Section 11.3 Basic FET Differential Pair

11.21 For the differential amplifier in Figure P11.21 the parameters are  $R_1 = 50 \,\mathrm{k}\Omega$  and  $R_D = 24 \,\mathrm{k}\Omega$ . The transistor parameters are:  $K_n = 0.25 \,\mathrm{mA/V^2}$ ,  $\lambda = 0$ , and  $V_{TN} = 2 \,\mathrm{V}$ . (a) Determine  $I_1$ ,  $I_Q$ ,  $I_{D1}$ ,  $V_{DS1}$ , and  $V_{DS4}$  when  $v_1 = v_2 = 0$ . (b) Draw the dc load line and plot the Q-point for transistor  $M_2$ . (c) What are the maximum and minimum values of the common-mode input voltage?

**RD11.22** The transistor parameters in the differential amplifier in Figure P11.21 are:  $K_{n1} = K_{n2} = 100 \,\mu\text{A}/\text{V}^2$ ,  $K_{n3} = K_{n4} = 200 \,\mu\text{A}/\text{V}^2$ ,  $\lambda_1 = \lambda_2 = 0$ ,  $\lambda_3 = \lambda_4 = 0.01 \,\text{V}^{-1}$ , and  $V_{TN} = 1.2 \,\text{V}$  (all transistors). (a) Design the circuit such that  $V_{DS1} = V_{DS2} = 12 \,\text{V}$  and  $I_{D1} = I_{D2} = 120 \,\mu\text{A}$  when  $v_1 = v_2 = -5.4 \,\text{V}$ . What are the values of  $I_Q$  and  $I_1$ ? (b) Calculate the change in  $I_Q$  if  $v_1 = v_2 = 0$ .

11.23 The transistor parameters for the differential amplifier in Figure P11.23 are:  $K_n = 0.4 \,\mathrm{mA/V^2}, \ \lambda = 0$ , and  $V_{TN} = 2 \,\mathrm{V}$ . (a) Find  $R_D$  and  $I_Q$  such that  $I_{D1} = I_{D2} = 0.5 \,\mathrm{mA}$  and  $v_{O2} = 7 \,\mathrm{V}$  when  $v_1 = v_2 = 0$ . (b) Draw the dc load line, and plot the Q-point for transistor  $M_2$ . (c) What are the maximum and minimum common-mode input voltages?

11.24 Consider the differential amplifier in Figure P11.24. Assume  $\lambda=0$  and  $V_{TN}=0.8\,\mathrm{V}$  for all transistors, and let  $I_Q=1\,\mathrm{mA}$ . The drain currents can be written as

$$I_{D1} = K_{n1}(V_{GS1} - V_{TN})^2$$

and  $I_{D2} = K_{n2}(V_{GS2} - V_{TN})^2$

(a) If  $v_1 = v_2 = 0$  and  $K_{n1} = K_{n2} = 0.4 \,\mathrm{mA/V^2}$ , find  $(v_{o1} - v_{o2})$  when: (i)  $R_{D1} = R_{D2} = 6 \,\mathrm{k}\Omega$ , and (ii)  $R_{D1} = 6 \,\mathrm{k}\Omega$ ,  $R_{D2} = 5.9 \,\mathrm{k}\Omega$ . (b) Repeat part (a) if  $K_{n1} = 0.4 \,\mathrm{mA/V^2}$  and  $K_{n2} = 0.44 \,\mathrm{mA/V^2}$ .

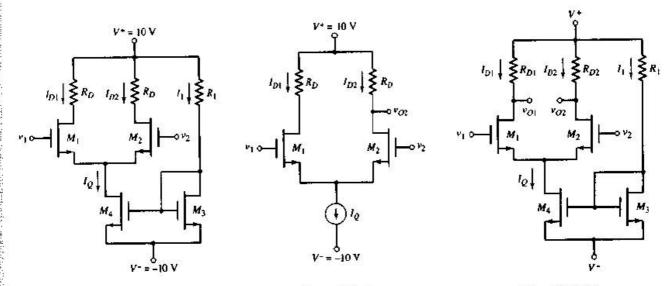

Figure P11.21

Figure P11.23

Figure P11.24

11.25 The transistor parameters for the diff-amp shown in Figure 11.19 are:  $K_n = 0.1 \,\text{mA/V}^2$ ,  $\lambda = 0$ , and  $V_{TN} = 1 \,\text{V}$ . The bias current is  $I_Q = 0.25 \,\text{mA}$ . (a) Determine the value of  $v_d = v_{G1} - v_{G2}$  that produces  $i_{D2} = 0.90 \, I_Q$ . (b) At what value of  $v_d$  does  $i_{D1} = I_Q$ ?

\*D11.26 The Hall effect experimental arrangement was described in Example 11.4. The required diff-amp is to be designed in the circuit configuration in Figure P11.24.

The transistor parameters are  $V_{TN} = 0.8 \text{ V}$ ,  $k_n' = 80 \,\mu\text{A/V}^2$ ,  $\lambda_1 = \lambda_2 = 0$ , and  $\lambda_3 = \lambda_4 = 0.01 \,\text{V}^{-1}$ . If the CMRR requirement cannot be met, a more sophisticated current source may have to be designed.

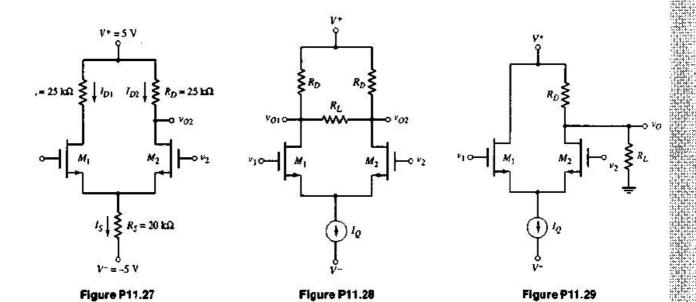

\*11.27 Consider the diff-amp in Figure P11.27. The transistor parameters are:  $K_{n1} = K_{n2} = 50 \,\mu\text{A/V}^2$ ,  $\lambda_1 = \lambda_2 = 0.02 \,\text{V}^{-1}$ , and  $V_{TN1} = V_{TN2} = 1 \,\text{V}$ . (a) Determine  $I_S$ ,  $I_{D1}$ ,  $I_{D2}$ , and  $v_{O2}$  for  $v_1 = v_2 = 0$ . (b) Using the small-signal equivalent circuit, determine the differential-mode voltage gain  $A_d = v_{o2}/v_d$ , the common-mode voltage gain  $A_{cm} = v_{a2}/v_{cm}$ , and the CMRR<sub>dB</sub>.

11.28 Consider the circuit shown in Figure PI I.28. Assume that  $\lambda=0$  for  $M_1$  and  $M_2$ . Also assume an ideal current source  $I_Q$ . Derive the expression for the one-sided differential mode gains  $A_{d1}=\nu_{o1}/\nu_d$  and  $A_{d2}=\nu_{o2}/\nu_d$ , and the two-sided differential-mode gain  $A_d=(\nu_{o2}-\nu_{o1})/\nu_d$ .

11.29 Assume  $\lambda_1 = \lambda_2 = 0$  for the transistors  $M_1$  and  $M_2$  in the circuit in Figure P11.29. Assuming an ideal current source  $I_Q$ , derive the expression for the differential-mode gain  $A_d = v_o/v_d$ .

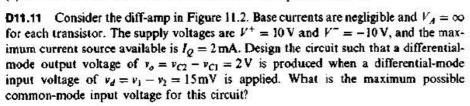

\*RD11.30 Consider the diff-amp in Figure 11.19. Assume  $\lambda = 0$  and  $V_{TN} = 1 \text{ V}$  for each transistor. The supply voltages are  $V^+ = 10 \text{ V}$  and  $V^- = -10 \text{ V}$ , and the maximum current source available is  $I_Q = 0.5 \text{ mA}$ . Redesign the circuit such that a differential-mode output voltage of  $v_o = 2 \text{ V}$  is produced when a differential-mode input voltage of  $v_d = v_1 - v_2 = 200 \text{ mV}$  is applied. What is the maximum possible common-mode input voltage that can be applied to this circuit?

11.31 Consider the small-signal equivalent circuit in Figure 11.23. Assume the output is a two-sided output defined as  $V_o = V_{d2} - V_{d1}$ , where  $V_{d2}$  and  $V_{d1}$  are the signal voltages at the drains of  $M_2$  and  $M_1$ , respectively. Derive expressions for the differential-and common-mode voltage gains.

\*D11.32 Consider a MOSFET diff-amp with the configuration in Figure P11.23. The transistor parameters are  $V_{TN} = 1 \text{ V}$ ,  $k_n' = 80 \mu\text{A/V}^2$ ,  $(W/L)_1 = (W/L)_2 = 10$ , and  $\lambda = 0$ . Let  $I_Q = 0.2 \text{ mA}$ . The range of the common-mode input voltage is  $-3 \le v_{CM} \le 3 \text{ V}$  and the CMRR is to be 45 dB. (a) Design the diff-amp to produce the maximum possible differential-mode voltage gain. (b) Design an all-MOSFET current

source to produce the desired bias current and CMRR. (The minimum W/L ratio of any transistor is to be 0.8.)

11.33 Consider the bridge circuit and diff-amp described in Problem 11.17. The BJT pair is to be replaced with a MOSFET pair whose parameters are  $V_{TN} = 0.5 \text{ V}$ ,  $K_n = 0.25 \text{ mA/V}^2$ , and  $\lambda = 0$ . Determine the range of output voltage  $v_{O2}$  as  $\delta$  changes. Explain the advantages and disadvantages of this circuit configuration compared to that in Problem 11.17.

**'D11.34** Figure P11.34 shows a two-stage cascade diff-amp with resistive loads. Power supply voltages of  $\pm 10 \,\mathrm{V}$  are available. Assume transistor parameters of  $V_{TN}=1 \,\mathrm{V}$ ,  $k_n'=60 \,\mu\mathrm{A/V^2}$ , and  $\lambda=0$ . Design the circuit such that the two-sided differential-mode voltage gain is  $A_{d1}=(v_{o2}-v_{o1})/(v_1-v_2)=20$  for the first stage, and that the one-sided differential-mode voltage gain is  $A_{d2}=v_{o3}/(v_{o2}-v_{o1})=30$  for the second stage. The circuit is to be designed such that the maximum differential-mode voltage swing is obtained in each stage.

Figure P11.34

\*11.35 Figure P11.35 shows a matched JFET differential pair biased with a current source  $I_Q$ . (a) Starting with

$$i_D = I_{DSS} \left( 1 - \frac{v_{GS}}{V_D} \right)^2$$

show that

$$\frac{l_{D1}}{I_Q} = \frac{1}{2} + \left(\frac{1}{-2V_P}\right) v_d \sqrt{2\left(\frac{I_{DSS}}{I_Q}\right) - \left(\frac{I_{DSS}}{I_Q}\right)^2 \left(\frac{v_d}{V_P}\right)^2}$$

and

$$\frac{i_{B2}}{I_O} = \frac{1}{2} - \left(\frac{1}{-2V_F}\right) v_d \sqrt{2\left(\frac{I_{DSS}}{I_O}\right) - \left(\frac{I_{DSS}}{I_O}\right)^2 \left(\frac{v_d}{V_F}\right)^2}$$

(b) Show that the  $I_Q$  bias current is switched entirely to one transistor or the other when

$$|v_d| = |V_P| \sqrt{\frac{I_Q}{I_{DSS}}}$$

(c) Show that the maximum forward transconductance is given by

$$g_f(\max) = \frac{di_{D1}}{dv_d}\Big|_{v_d=0} = \left(\frac{1}{-V_P}\right) \sqrt{\frac{I_Q \cdot I_{DSS}}{2}}$$

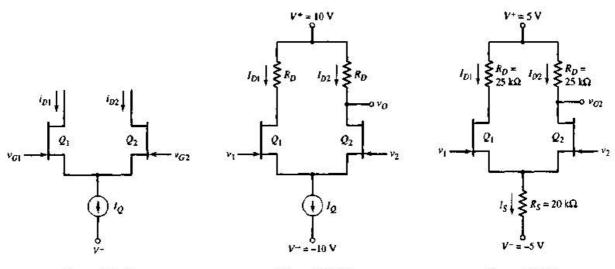

11.36 A JFET differential amplifier is shown in Figure P11.36. The transistor parameters are:  $V_P = -4 \text{ V}$ ,  $I_{DSS} = 2 \text{ mA}$ , and  $\lambda = 0$ . (a) Find  $R_D$  and  $I_Q$  such that  $I_{D1} = I_{D2} = 0.5 \text{ mA}$  and  $v_{o2} = 7 \text{ V}$  when  $v_1 = v_2 = 0$ . (b) Calculate the maximum forward transconductance. (c) Determine the one-sided differential-mode voltage gain  $A_d = v_o/v_d$ .

\*11.37 Consider the JFET diff-amp shown in Figure P11.37. The transistor parameters are:  $I_{DSS} = 0.8 \,\mathrm{mA}$ ,  $\lambda = 0.02 \,\mathrm{V}^{-1}$ , and  $V_P = -2 \,\mathrm{V}$ . (a) Determine  $I_S$ ,  $I_{D1}$ ,  $I_{D2}$ , and  $v_{o2}$  for  $v_1 = v_2 = 0$ . (b) Using the small-signal equivalent circuit, determine the differential-mode voltage gain  $A_d = v_{o2}/v_d$ , the common-mode voltage gain  $A_{cm} = v_o/v_{cm}$ , and the CMRR<sub>dB</sub>.

Figure P11.35

Figure P11.36

Figure P11.37

\*11.38 Consider the circuit in Figure P11.38. Assume that  $\lambda=0$  for the transistors, and assume an ideal current source  $I_Q$ . Derive the expressions for the one-sided differential-mode gains  $A_{d1} = v_{o1}/v_d$  and  $A_{d2} = v_{o2}/v_d$ , and for the two-sided differential-mode gain  $A_d = (v_{o2} - v_{o1})/v_d$ .

#### Section 11.4 Differential Amplifier with Active Load

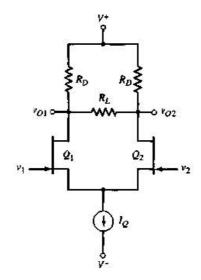

\*11.39 Consider the diff-amp with active load in Figure P11.39. The Early voltages are  $V_{AN} = 120 \,\mathrm{V}$  for  $Q_1$  and  $Q_2$  and  $V_{AP} = 80 \,\mathrm{V}$  for  $Q_3$  and  $Q_4$ . (a) Determine the open-circuit differential-mode voltage gain. (b) Compare this value to the gain obtained when R = 0. (c) Determine the output resistance  $R_0$  for parts (a) and (b).

Figure P11.38

- 11.40 The diff-amp in Figure P11.40 has a three-transistor active load circuit and a Darlington pair configuration connected to the output. Determine the bias current  $I_{Q1}$  in terms of  $I_Q$  such that the diff-amp dc currents are balanced.

- 11.41 For the diff-amp in Figure 11.30, the parameters are:  $V^+ = 10 \text{ V}$ ,  $V^- = -10 \text{ V}$ , and  $I_Q = 0.8 \text{ mA}$ . The transistor parameters are:  $\beta = 150$ ,  $V_{A1} = V_{A2} = 150 \text{ V}$ , and  $V_{A3} = V_{A4} = 100 \text{ V}$ . (a) Determine the open-circuit differential-mode voltage gain. (b) Find the load resistance  $R_L$  that will reduce the differential-mode voltage gain to one-half the open-circuit value.

- \*11.42 Consider the circuit in Figure Pi1.42, in which the input transistors to the diffamp are Darlington pairs. Assume transistor parameters of  $\beta(npn) = 120$ ,  $\beta(pnp) = 80$ ,  $V_A(npn) = 100 \text{ V}$ , and  $V_A(pnp) = 80 \text{ V}$ . Let the power supply voltages be  $\pm 10 \text{ V}$  and let

Figure P11.42

$I_Q = 1 \text{ mA}$ . (a) Determine the output resistance  $R_o$ . (b) Calculate the differential-mode voltage gain. (c) Find the differential-mode input resistance  $R_d$ .

\*D11.43 Design a differential amplifier as shown in Figure 11.28 incorporating a basic two-transistor current source to establish  $I_Q$ . The bias voltages are  $V^+ = 15 \,\mathrm{V}$  and  $V^- = -15 \,\mathrm{V}$ , the transistor parameters are  $\beta = 180$  and  $V_A = 100 \,\mathrm{V}$ , and the maximum forward transconductance is to be  $8 \,\mathrm{mA/V}$ . (a) Show the complete circuit, with all component values. (b) What are the values of open-circuit differential-mode voltage gain, differential-mode input resistance, and output resistance? (c) Determine the common-mode input voltage range and the common-mode input resistance.

11.44 . The differential amplifier shown in Figure P11.44 has a pair of pnp bipolars as input devices and a pair of npn bipolars connected as an active load. The circuit bias is  $I_Q = 0.2 \,\mathrm{mA}$ , and the transistor parameters are  $\beta = 100$  and  $V_A = 100 \,\mathrm{V}$ . (a) Determine  $I_Q$  such that the dc currents in the diff-amp are balanced. (b) Find the open-circuit differential-mode voltage gain. (c) Determine the differential-mode voltage gain if a load resistance  $R_L = 250 \,\mathrm{k}\Omega$  is connected to the output.

Figure P11.44

\*11.45 Reconsider the circuit in Figure P11.44 excep that  $1 \text{ k}\Omega$  resistors are inserted at the emitters of the active load transistors  $Q_3$  and  $Q_4$  as in the circuit in Figure P11.39. Assume the same transistor parameters as in Problem 11.44. (a) Determine the output resistance looking into the output of the diff-amp circuit. (b) Find the open-circuit differential-mode voltage gain.

**\*D11.46** For the transistors in the diff-amp circuit in Figure 11.30 the parameters are:  $\beta = 150$ ,  $V_{A1} = V_{A2} = 125 \text{ V}$ , and  $V_{A3} = V_{A4} = 80 \text{ V}$ . The supply voltages are  $V^+ = 10 \text{ V}$  and  $V^- = -10 \text{ V}$ , and the maximum current source available is  $I_Q = 2 \text{ mA}$ . A load resistance of  $R_L = 200 \text{ k}\Omega$  is connected to the output. (a) Design the circuit such that the differential-mode voltage gain is 1000. (b) If  $V_{BE}(\text{on}) = 0.6 \text{ V}$ , what is the maximum possible common-mode input voltage that can be applied to the circuit?

D11.47 Design a BJT diff-amp with an active load similar to the configuration in Figure P11.42 except that the input devices are to be pnp transistors and the active load will have npn transistors. Using the same parameters as in Problem 11.42, determine the small-signal differential-mode voltage gain.

11.48 The differential amplifier in Figure P11.48 has a pair of PMOS transistors as input devices and a pair of NMOS transistors connected as an active load. The circuit is biased with  $I_Q = 0.2 \,\text{mA}$ , and the transistor parameters are:  $K_n = K_p = 0.1 \,\text{mA/V}^2$ ,  $\lambda_n = 0.01 \,\text{V}^{-1}$ ,  $\lambda_p = 0.015 \,\text{V}^{-1}$ ,  $V_{TN} = 1 \,\text{V}$ , and  $V_{TP} = -1 \,\text{V}$ . (a) Determine the quiescent drain-to-source voltage in each transistor. (b) Find the open-circuit differential-mode voltage gain. (c) What is the output resistance?

11.49 For the differential amplifier in Figure 11.32, the parameters are:  $V^+ = 5 \text{ V}$ ,  $V^- = -5 \text{ V}$ , and  $I_Q = 0.15 \text{ mA}$ . The PMOS parameters are:  $K_p = 100 \, \mu\text{A}/\text{V}^2$ ,  $\lambda_p = 0.02 \, \text{V}^{-1}$ , and  $V_{TP} = -0.8 \, \text{V}$ . The NMOS parameters are:  $K_n = 120 \, \mu\text{A}/\text{V}^2$ ,  $\lambda_n = 0.015 \, \text{V}^{-1}$ , and  $V_{TN} = +0.8 \, \text{V}$ . Determine the differential-mode voltage gain  $A_d = v_o/v_d$ .

\*11.50 Consider the diff-amp in Figure P11.50. The PMOS parameters are:  $K_p = 80 \,\mu\text{A/V}^2$ ,  $\lambda_p = 0.02 \,\text{V}^{-1}$ ,  $V_{TP} = -2 \,\text{V}$ . The NMOS parameters are:  $K_n = 80 \,\mu\text{A/V}^2$ ,  $\lambda_n = 0.015 \,\text{V}^{-1}$ ,  $V_{TN} = +2 \,\text{V}$ . (a) Determine the open-circuit differential-mode voltage

Figure P11.48

Figure P11.50

- gain. (b) Compare this value to the gain obtained when  $R_1 = 0$ , (c) What is the output resistance of the diff-amp for parts (a) and (b)?

- **D11.51** Reconsider the diff-amp specifications listed in Problem 11.26. (a) Design an all-CMOS diff-amp with the configuration in Figure 11.32 to meet the specifications. Assume NMOS parameters of  $V_{TN} = 0.8 \text{ V}$ ,  $k_n' = 80 \,\mu\text{A/V}^2$ , and  $\lambda_n = 0.02 \,\text{V}^{-1}$  and PMOS parameters of  $V_{TP} = -0.8 \,\text{V}$ ,  $k_p' = 35 \,\mu\text{A/V}^2$ , and  $\lambda_p = 0.025 \,\text{V}^{-1}$ . (b) Determine the common-mode voltage gain using a computer simulation.

- **D11.52** Design an all-CMOS diff-amp, including the current source circuit, with the configuration in Figure 11.32 to have a differential-mode voltage gain of  $A_d = 80$ . The circuit is to be biased at  $\pm 3$  V and the total power dissipated in the circuit is to be no more than 0.5 mW. The available transistors have parameters of  $V_{TN} = 0.4$  V,  $k'_n = 80 \,\mu\text{A}/\text{V}^2$ ,  $\lambda_n = 0.015 \,\text{V}^{-1}$ ,  $V_{TP} = -0.4 \,\text{V}$ ,  $k'_p = 40 \,\mu\text{A}/\text{V}^2$ , and  $\lambda_p = 0.02 \,\text{V}^{-1}$ . Verify the differential-mode voltage gain of the design with a computer simulation. Also, determine the common-mode gain with a computer simulation.

- **RD11.53** Redesign the cascode active load CMOS diff-amp in Figure 11.36 to achieve a differential-mode voltage gain of  $A_d = 400$ . Assume  $k_n' = 80 \,\mu\text{A/V}^2$  and  $k_p' = 40 \,\mu\text{A/V}^2$  and use other transistor parameters described in Example 11.15.

- \*11.54 Consider the fully cascoded diff-amp in Figure 11.37. Assume  $I_Q = 80 \,\mu\text{A}$  and transistor parameters of:  $V_{TN} = 0.8 \,\text{V}$ ,  $k_n' = 60 \,\mu\text{A}/\text{V}^2$ ,  $\lambda_n = 0.015 \,\text{V}^{-1}$ ,  $V_{TP} = -0.8 \,\text{V}$ ,  $k_p' = 25 \,\mu\text{A}/\text{V}^2$ , and  $\lambda_p = 0.02 \,\text{V}^{-1}$ . The transistor width-to-length ratios are W/L = 60/4 for transistors  $M_1 M_4$ , W/L = 40/4 for transistors  $M_5 M_6$ , and W/L = 4/4 for transistors  $M_7 M_8$ . (a) Determine the output resistance of the diff-amp. (b) Calculate the differential-mode voltage gain of the diff-amp. (c) Find the common-mode voltage gain of the diff-amp using a computer simulation.

#### Section 11.5 BiCMOS Circuits

- **11.55** The Darlington pair circuit in Figure 11.45 has new bias current levels of  $I_{\text{BIAS1}} = 0.25 \,\text{mA}$  and  $I_{\text{BIAS2}} = 1 \,\text{mA}$ . The transistor parameters are:  $K_n = 0.2 \,\text{mA/V}^2$ ,  $V_{TN} = 1 \,\text{V}$ , and  $\lambda = 0$  for  $M_1$ ; and  $\beta = 120$ ,  $V_{BE}(\text{on}) = 0.7 \,\text{V}$ , and  $V_A = \infty$  for  $Q_2$ . Determine the small-signal parameters for each transistor, and find the composite transconductance.

- 11.56 Consider the BiCMOS diff-amp in Figure 11.44, biased at  $I_U = 0.4 \,\text{mA}$ . The transistor parameters for  $M_1$  and  $M_2$  are:  $K_n = 0.2 \,\text{mA/V}^2$ ,  $V_{TN} = 1 \,\text{V}$ , and  $\lambda = 0.01 \,\text{V}^{-1}$ . The parameters for  $Q_1$  and  $Q_2$  are:  $\beta = 120$ ,  $V_{EB}(\text{on}) = 0.7 \,\text{V}$ , and  $V_A = 80 \,\text{V}$ . (a) Determine the differential-mode voltage gain. (b) If the output resistance of the current source is  $R_0 = 500 \,\text{k}\Omega$ , determine the common-mode voltage gain using a computer simulation analysis.

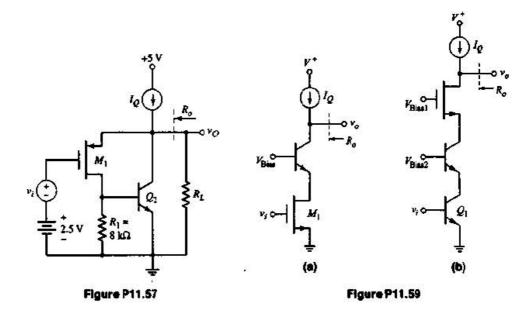

- \*11.57 The BiCMOS circuit in Figure P11.57 is equivalent to a pnp bipolar transistor with an infinite input impedance. The bias current is  $I_Q = 900 \,\mu\text{A}$ . The transistor parameters are:  $K_\rho = 1 \,\text{mA/V}^2$ ,  $V_{TP} = -1 \,\text{V}$ , and  $\lambda = 0$  for  $M_1$ : and  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \,\text{V}$ , and  $V_A = \infty$  for  $Q_2$ . (a) Sketch the small-signal equivalent circuit. (b) Determine the small-signal parameters for each transistor. (c) Determine the small-signal voltage gain  $A_V = V_0/V_1$ .

- \*11.58 Consider the BiCMOS circuit in Figure P11.57. The bias current is  $I_Q = 1.2 \,\text{mA}$ , and the transistor parameters are the same as described in Problem 11.57. (a) Determine the small-signal transistor parameters. (b) Find the output impedance  $R_p$ .

- \*11.59 The bias current  $I_Q$  is 25  $\mu$ A in each circuit in Figure P11.59. The BJT parameters are  $\beta = 100$  and  $V_A = 50 \, \text{V}$ , and the MOSFET parameters are  $V_{TN} = 0.8 \, \text{V}$ ,  $K_A = 0.25 \, \text{mA/V}^2$ , and  $\lambda = 0.02 \, \text{V}^{-1}$ . Assume the two amplifying transistors  $M_1$  and

$Q_i$  are biased in the saturation region and forward-active region, respectively. Determine the small-signal voltage gain  $A_v = v_o/v_i$  and the output resistance  $R_o$  for each circuit.

11.60 For the circuit shown in Figure P11.60, determine the small-signal voltage gain,  $A_t = v_o/v_t$ . Assume transistor parameters of  $V_{TN} = 1 \text{ V}$ ,  $K_n = 0.2 \text{ mA/V}^2$ , and  $\lambda = 0$  for  $M_1$  and  $\beta = 80$  and  $V_A = \infty$  for  $Q_1$ .

Figure P11.60

## Section 11.6 Gain Stage and Simple Output Stage

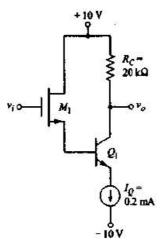

11.61 Consider the circuit in Figure P11.61. The output stage is a Darlington pair emitter-follower configuration. Assume  $\beta = 100$  for all transistors, and let  $V_A = 100 \text{ V}$  for  $Q_7$  and  $Q_{11}$ . Determine the output resistance  $R_0$ .

Figure P11.61

Figure P11.62

\*11.62 For the circuit in Figure P11.62, the transistor parameters are  $\beta = 100$  and  $V_A = \infty$ . The bias currents in the transistors are indicated on the figure. Determine the input resistance  $R_i$ , the output resistance  $R_o$ , and the small-signal voltage gain  $A_r = v_o/v_{in}$ .

11.63 Consider the circuit in Figure P11.63. The bias currents  $I_1$  and  $I_2$  are such that a zero dc output voltage is established. The transistor parameters are:  $K_p = 0.2 \text{ mA/V}^2$ ,  $K_N = 0.5 \text{ mA/V}^2$ ,  $V_{TP} = -0.8 \text{ V}$ ,  $V_{TN} = +0.8 \text{ V}$ , and  $\lambda_N = \lambda_p = 0.01 \text{ V}^{-1}$ . Determine the small-signal voltage gain  $A_T = v_o/v_{th}$  and the output resistance  $R_o$ .

11.64 The circuit shown in Figure P11.64 has bias currents  $I_1 = 0.1 \,\mathrm{mA}$  and  $I_2 = 0.5 \,\mathrm{mA}$ . The transistor parameters are:  $K_n = 100 \,\mathrm{\mu A/V^2}$ ,  $K_p = 250 \,\mathrm{\mu A/V^2}$ ,  $V_{TN} = 1 \,\mathrm{V}$ ,  $V_{TP} = -1 \,\mathrm{V}$ , and  $\lambda_n = \lambda_p = 0.01 \,\mathrm{V^{-1}}$ . (a) Determine the resistor values  $R_1$  and  $R_2$  such that the dc value of the output voltage is zero. (b) Find the small-signal voltage gain  $A_v = v_o/v_{v1}$  and the output resistance  $R_o$ .

Figure P11.63

Figure P11.64

# Section 11.7 Simplified Op-Amp Circuits

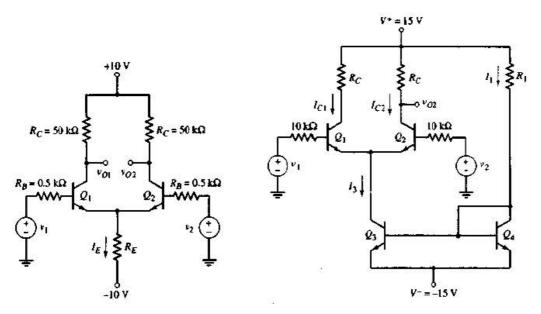

**11.65** Consider the multistage bipolar circuit in Figure P11.65, in which base currents are negligible. Assume the transistor parameters are:  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = \infty$ . The output resistance of the constant-current source is  $R_o = 100 \text{ k}\Omega$ . (a) For  $v_1 = v_2 = 0$ , design the circuit such that:  $v_{o2} = 2 \text{ V}$ ,  $v_{o3} = 3 \text{ V}$ ,  $v_o = 0$ ,  $I_{CQ3} = 0.5 \text{ mA}$ , and  $I_{CQ4} = 3 \text{ mA}$ . (b) Determine the differential-mode voltage gains  $A_{d1} = v_{o2}/v_{d1}$  and  $A_{d2} = v_{o2}/v_{d2}$ . (c) Determine the common-mode voltage gains  $A_{cm1} = v_{o2}/v_{cm1}$  and  $A_{cm1} = v_{o2}/v_{cm2}$ , and the overall CMRR<sub>dB</sub>.

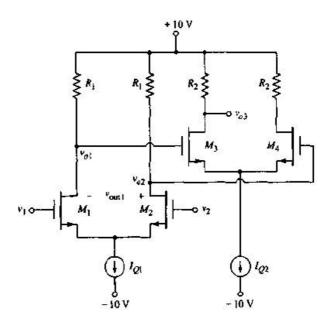

**\*D11.66** The circuit in Figure P11.66 has two bipolar differential amplifiers in cascade, biased with ideal current sources  $I_{Q1}$  and  $I_{Q2}$ . Assume the transistor parameters are  $\beta = 180$  and  $V_A = \infty$ . (a) Design the circuit such that  $v_{o1} = v_{o2} = 2$  V and  $v_{O4} = 6$  V when  $v_1 = v_2 = 0$ . (b) Determine the differential-mode voltage gains  $A_{d1} = (v_{o1} - v_{o2})/v_d$  and  $A_d = v_{o4}/v_d$ .

Figure P11.65

Figure P11.66

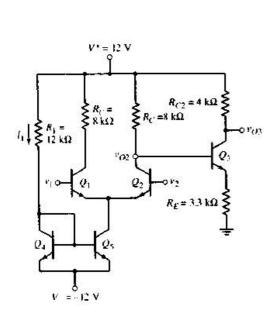

\*11.67 The transistor parameters for the circuit in Figure P11.67 are:  $\beta = 200$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = 80 \text{ V}$ . (a) Determine the differential-mode voltage gain  $A_{cm} = v_{a3}/v_{cm}$ . (b) Determine the output voltage  $v_{a3}$  if  $v_1 = 2.015 \sin \omega t \text{ V}$  and  $v_2 = 1.985 \sin \omega t \text{ V}$ . Compare this output to the ideal output that would be obtained if  $A_{cm} = 0$ . (c) Find the differential-mode and common-mode input resistances.

\*11.68 For the transistors in the circuit in Figure P11.68, the parameters are:  $K_n = 0.2 \,\mathrm{mA/V^2}$ ,  $V_{TN} = 2 \,\mathrm{V}$ , and  $\lambda = 0.02 \,\mathrm{V^{-1}}$ . (a) Determine the differential-mode voltage gain  $A_d = v_{o3}/v_d$  and the common-mode voltage gain  $A_{cm} = v_{o3}/v_{cm}$ . (b) Determine the output voltage  $v_{o3}$  if  $v_1 = 2.15 \sin \omega t \,\mathrm{V}$  and  $v_2 = 1.85 \sin \omega t \,\mathrm{V}$ . Compare this output to the ideal output that would be obtained if  $A_{cm} = 0$ .

#### Section 11.8 Diff-Amp Frequency Response

11.69 Consider the differential amplifier in Figure 11.49(a), with parameters:  $I_Q = 1 \text{ mA}$ ,  $R_C = 10 \text{ k}\Omega$ , and  $R_\beta = 0.5 \text{ k}\Omega$ . The transistor parameters are:  $\beta = 100$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ ,  $V_A = \infty$ ,  $C_\pi = 8 \text{ pF}$ , and  $C_\mu = 2 \text{ pF}$ . Determine the low-frequency

Figure P11.67

Figure P11.68

differential-mode gain and the upper 3 dB frequency. What is the equivalent Miller capacitance of each transistor?

11.70 The differential amplifier in Figure 11.50(a) has the same circuit and transistor parameters as in Problem 11.69. The equivalent impedance parameters of the current source are  $R_n = 5 \,\mathrm{M}\Omega$  and  $C_n = 0.8 \,\mathrm{pF}$ . (a) Determine the frequency of the zero in the common-mode gain. (b) Plot CMRR<sub>dB</sub> versus frequency, showing the frequencies  $f_n$  and  $f_{H}$ .

11.71 A BJT diff-amp is biased with a current source  $I_Q=2\,\mathrm{mA}$ , and the circuit parameters are  $R_C=10\,\mathrm{k}\Omega$  and  $R_B=1\,\mathrm{k}\Omega$ . The transistor parameters are:  $\beta=120$ ,  $f_T=800\,\mathrm{MHz}$ , and  $C_\mu=1\,\mathrm{pF}$ . (a) Determine the upper 3dB frequency of the differential-mode gain. (b) If the current source impedance parameters are  $R_0=10\,\mathrm{M}\Omega$  and  $C_\mu=1\,\mathrm{pF}$ , find the frequency of the zero in the common-mode gain.

11.72 Consider the diff-amp in Figure 11.54. The circuit and transistor parameters are the same as in Problem 11.69. For a one-sided output at  $v_{o2}$ , determine the differential-mode gain for: (a)  $R_E = 100 \,\Omega$ , and (b)  $R_E = 250 \,\Omega$ .

# COMPUTER SIMULATION PROBLEMS

11.73 For the transistors in the circuit in Figure P11.73, the parameters are:  $\beta = 100$ ,  $I_S = 2 \times 10^{-15}$  A, and  $V_A = 100$  V. From a PSpice analysis, determine: (a) the quiescent currents  $I_1$ ,  $I_Q$ ,  $I_{C1}$ , and  $I_{C2}$ , and (b) the differential- and common-mode gains for (i)  $R_L = 10 \text{ M}\Omega$ , and (ii)  $R_L = 200 \text{ k}\Omega$ .

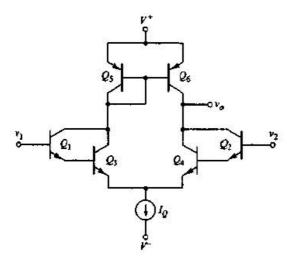

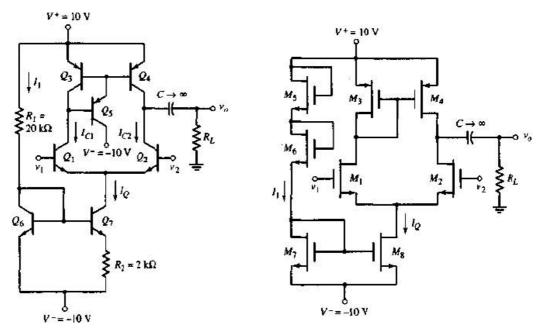

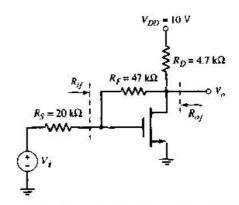

11.74 Consider the circuit in Figure P11.74. The transistor parameters are:  $V_{TN} = 2 \text{ V}$  (all NMOS devices),  $V_{TP} = -2 \text{ V}$  (all PMOS devices),  $K_{n5} = K_{n6} = 50 \,\mu\text{A}/\text{V}^2$ ,  $K_{n7} = K_{n8} = 200 \,\mu\text{A}/\text{V}^2$ ,  $K_{n1} = K_{n2} = K_{p3} = K_{p4} = 100 \,\mu\text{A}/\text{V}^2$ , and  $\lambda = 0.01 \,\text{V}^{-1}$  (all devices). From a computer analysis, determine: (a) the quiescent currents  $I_1$  and  $I_Q$ ; and (b) the differential- and common-mode gains for (i)  $R_L = 10 \,\text{M}\Omega$  and (ii)  $R_L = 400 \,\text{k}\Omega$ .

Figure P11.73

Figure P11.74

11.75 For the circuit in Figure 11.46 the parameters are:  $V^+ = 10 \text{ V}$ ,  $V^- = -10 \text{ V}$ ,  $R_1 = 19 \text{ k}\Omega$ ,  $R_2 = R_3 = 0.2 \text{ k}\Omega$ , and  $R_4 = 10 \text{ k}\Omega$ . The transistor parameters are:  $\beta = 100$ ,  $I_S = 2 \times 10^{-15} \text{ A}$ , and  $V_A = 100 \text{ V}$ . (a) From a computer analysis, determine the quiescent currents  $I_1$ ,  $I_Q$ ,  $I_{C1}$ ,  $I_{C2}$ ,  $I_{B5}$ ,  $I_O$ , and  $I_{C7}$ . (b) Also from a computer analysis, determine the input resistance  $R_i$ , output resistance  $R_o$ , and voltage gain  $A_v = v_O/v_{O2}$ . (c) Compare these results to those obtained in Examples 11.16 and 11.17.

11.76 Consider the circuit in Figure P11.67, with circuit and transistor parameters described in Problem 11.67. Let  $I_S = 2 \times 10^{-15}$  A. From a computer analysis, determine: (a) the differential-mode voltage gain, (b) the common-mode voltage gain, (c) the input differential-mode resistance, and (d) the input common-mode resistance.

11.77 Consider the diff-amp described in Problems 11.69 and 11.70. Using a computer analysis, determine the CMRR<sub>dB</sub> versus frequency characteristic.

# **DESIGN PROBLEMS**

[Note: Each design is to be correlated with a computer simulation analysis.]

\*D11.78 Design a basic BJT diff-amp with an active load, to provide an open-circuit differential-mode gain of  $|A_d| = 2000$  and a common-mode rejection ratio of CMRR<sub>dB</sub> = 80 dB. Specify the bias currents, minimum Early voltage, and minimum output impedance of the current source. Design the current source to achieve the specified output impedance.

\*D11.79 Design a basic MOSFET diff-amp with an active load, to provide an open-circuit differential-mode gain of  $|A_d| = 200$  and a common-mode rejection ratio of CMRR<sub>dB</sub> = 70 dB. Specify the bias currents, conduction parameter values, minimum  $\lambda$  values, and minimum output impedance of the current source. Design the current source to achieve the specified output impedance specification.

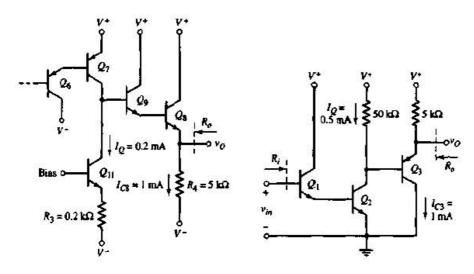

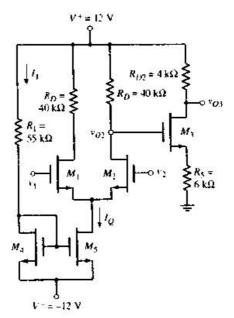

Figure P11.82

\*D11.80 Consider the BiCMOS diff-amp in Figure 11.44. Design the circuit to provide a differential-mode gain of  $\{A_d\} = 500$  and a common-mode rejection ratio of CMRR<sub>dB</sub> = 70 dB. Specify the bias currents, MOSFET conduction parameter values, minimum bipolar Early voltage, MOSFET  $\lambda$  values, and minimum output resistance of the current source. Design the current source to achieve this specified output resistance.

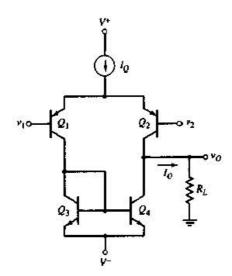

\*D11.81 Consider the bipolar op-amp configuration in Figure 11.48. The bias voltages are  $\pm 10 \text{ V}$ , as shown, the current  $I_{R7}$  is to be  $I_{R7} = 3 \text{ mA}$ , and the maximum dc power dissipation in the circuit is to be 120 mW. The output voltage is to be  $v_0 = 0$  for  $v_1 = v_2 = 0$ . Design the circuit, using reasonable resistance and current values. What is the overall differential-mode voltage gain?

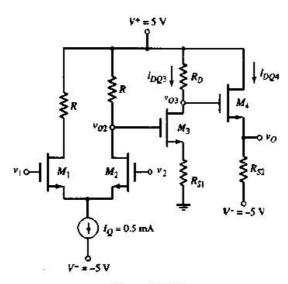

**\*D11.82** The transistor parameters for the circuit in Figure P11.82 are:  $K_n = 0.2 \,\mathrm{mA/V^2}$ ,  $V_{TN} = 0.8 \,\mathrm{V}$ , and  $\lambda = 0$ . The output resistance of the constant-current source is  $R_o = 100 \,\mathrm{k}\Omega$ . (a) For  $v_1 = v_2 = 0$ , design the circuit such that:  $v_{o2} = 2 \,\mathrm{V}$ ,  $v_{o3} = 3 \,\mathrm{V}$ ,  $v_o = 0$ ,  $I_{DQ3} = 0.25 \,\mathrm{mA}$ , and  $I_{DQ} = 2 \,\mathrm{mA}$ . (b) Determine the differential-mode gains  $A_{d1} = v_{o2}/v_{d1}$  and  $A_{d1} = v_{o2}/v_{d2}$  and  $A_{d2} = v_{o2}/v_{d3}$ . (c) Determine the common-mode voltage gains  $A_{cm1} = v_{o2}/v_{cm1}$  and  $A_{cm2} = v_{o2}/v_{cm2}$ , and the overall CMRR<sub>dB</sub>.

CHAPTER

12

# Feedback and Stability

#### 12.0 PREVIEW

Previously, we found that the small-signal voltage gain and other characteristics of discrete BJT and MOSFET transistor circuit amplifiers are functions of the bipolar current gain and the MOSFET conduction parameter. In general, these transistor parameters vary with temperature and they have a range of values for a given type of transistor group, because of processing and material property tolerances. This means that the Q-point, voltage gain, and other circuit properties can vary from one circuit to another, and can be functions of temperature.

Transistor circuit characteristics can be made essentially independent of the individual transistor parameters by using feedback. The feedback process takes a portion of the output signal and returns it to the input to become part of the input excitation. We previously encountered feedback in our study of ideal op-amps and op-amp circuits. For example, resistors are connected between the output and input terminals of an ideal op-amp to form a feedback network. The voltage gain of these ideal circuits is a function only of the ratio of resistors and not of any individual transistor parameters. In this chapter, we formally study feedback and feedback circuits.

We begin the chapter by presenting general feedback theory and determining general properties of feedback circuits. We then analyze the four basic ideal feedback configurations. For each type of feedback topology, the output-to-input signal transfer function is determined and the expressions for input and output resistances are derived. We analyze various op-amp and discrete transistor circuits representing each of the four basic feedback configurations, and compare the transfer functions, input resistance, and output resistances to the ideal theory. Principal goals of this chapter are to understand the characteristics of the various types of feedback configurations to be able to determine the type of feedback circuit required for a specific design application and to design a stable feedback amplifier.

#### 12.1 INTRODUCTION TO FEEDBACK

Feedback is used in virtually all amplifier systems. Harold Black, an electronics engineer with the Western Electric Company, invented the feedback amplifier

in 1928 while searching for methods to stabilize the gain of amplifiers for use in telephone repeaters. In a feedback system, a signal that is proportional to the output is fed back to the input and combined with the input signal to produce a desired system response. As we will see, external feedback is used deliberately to achieve particular system benefits. However, feedback may be unintentional and an undesired system response may be produced.

We have already seen examples of feedback in previous chapters, although the term feedback may not have been used. For example, in Chapters 3 and 5 we introduced resistors at the emitter of BJT common-emitter circuits and at the source of MOSFET common-source circuits to stabilize the Q-point against variations in transistor parameters. This technique introduces negative feedback in the circuit. An increase in collector or drain current produces an increase in the voltage across these resistors which produces a decrease in the base-emitter or gate-source voltage. The decrease in these device voltages tends to reduce or oppose the change in collector or drain current. Opposition to change is suggested by use of the term negative feedback.

Feedback can be either negative or positive. In negative feedback, a portion of the output signal is subtracted from the input signal; in positive feedback, a portion of the output signal is added to the input signal. Negative feedback, for example, tends to maintain a constant value of amplifier voltage gain against variations in transistor parameters, supply voltages, and temperature. Positive feedback is used in the design of oscillators and in a number of other applications. In this chapter, we will concentrate on negative feedback.

# 12.1.1 Advantages and Disadvantages of Negative Feedback

Before we actually get into the analysis and design of feedback circuits, we will list some of the advantages and disadvantages of negative feedback. Although these characteristics and properties of negative feedback are not obvious at this point, they are listed here so that the reader can anticipate these results during the derivations and analysis.

## Advantages

- Gain sensitivity. Variations in the circuit transfer function (gain) as a result of changes in transistor parameters are reduced by feedback. This reduction in sensitivity is one of the most attractive features of negative feedback.

- Bandwidth extension. The bandwidth of a circuit that incorporates negative feedback is larger than that of the basic amplifier.

- 3. Noise sensitivity. Negative feedback may increase the signal-to-noise ratio if noise is generated within the feedback loop.

- 4. Reduction of nonlinear distortion. Since transistors have nonlinear characteristics, distortion may appear in the output signals, especially at large signal levels. Negative feedback reduces this distortion.

- Control of impedance levels. The input and output impedances can be increased or decreased with the proper type of negative feedback circuit.

#### Disadvantages

- Circuit gain. The overall amplifier gain, with negative feedback, is reduced compared to the basic amplifier used in the circuit.

- 2. Stability. There is a possibility that the feedback circuit may become unstable (oscillate) at high frequencies.

These advantages and disadvantages will be further discussed as we develop the feedback theory.

In the course of our discussion, we will analyze several feedback circuits, in both discrete and op-amp circuit configurations. First, however, we will consider the ideal feedback theory and derive the general characteristics of feedback amplifiers. In this section, we discuss the ideal signal gain, gain sensitivity, bandwidth extension, noise sensitivity, and reduction of nonlinear distortion of a generalized feedback amplifier.

## 12.1.2 Use of Computer Simulation

Conventional methods of analysis that have been used in the previous chapters apply directly to feedback circuits. That is, the same dc analysis techniques and the same small-signal transistor equivalent circuits apply directly to feedback circuits in this chapter. However, in the analysis of feedback circuits, several simultaneous equations can be obtained, the time involved may be quite long and the probability of introducing errors may become almost certain.

Therefore, computer simulation of feedback circuits may prove to be very useful and is used fairly often throughout this chapter. As always, a word of warning is in order concerning computer simulation. Computer simulation does not replace basic understanding. It is important for the reader to understand the concepts and characteristics of the basic types of feedback circuits. Computer simulation is used only as a tool for obtaining specific results.

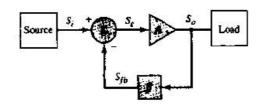

# 12.2 BASIC FEEDBACK CONCEPTS

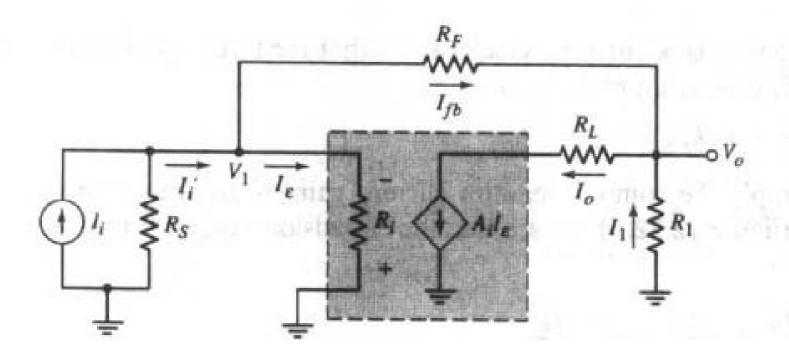

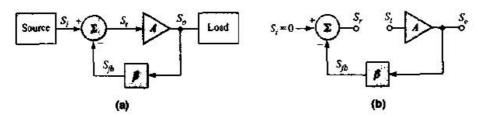

Figure 12.1 shows the basic configuration of a feedback amplifier. In the diagram, the various signals S can be either currents or voltages. The circuit contains a basic amplifier with an open-loop gain A and a feedback circuit that samples the output signal and produces a feedback signal  $S_B$ . The feedback signal is subtracted from the input source signal, which produces an error signal  $S_P$ . The error signal is the input to the basic amplifier and is the signal that is amplified to produce the output signal. The subtraction property produces the negative feedback.

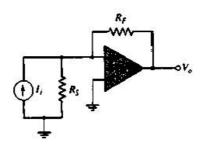

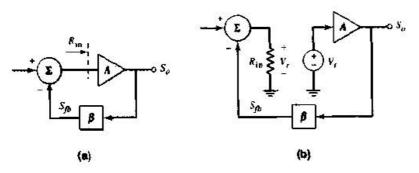

Figure 12.1 Basic configuration of a feedback amplifier

Implicit in the diagram in Figure 12.1 is the assumption that the input signal is transmitted through the amplifier only, none through the feedback network, and that the output signal is transmitted back through the feedback network only, none through the amplifier. Also, there are no loading effects in the ideal feedback system. The feedback network does not load down the output of the basic amplifier, and the basic amplifier and feedback network do not produce a loading effect on the input signal source. In actual feedback circuits, these assumptions and conditions are not entirely accurate. We will see later how nonideal conditions change the characteristics of actual feedback circuits with respect to those of the ideal feedback network.

# 12.2.1 Ideal Closed-Loop Signal Gain

From Figure 12.1, the output signal is

$$S_o = AS_c \tag{12.1}$$

where A is the amplification factor, and the feedback signal is

$$S_{th} = \beta S_{tt} \tag{12.2}$$

where  $\beta$  in this case is the feedback transfer function. At the summing node, we have

$$S_e = S_t - S_{tb} \tag{12.3}$$

where  $S_i$  is the input signal. Equation (12.1) then becomes

$$S_o = A(S_i - \beta S_a) = AS_i - \beta AS_o \tag{12.4}$$

Equation (12.4) can be rearranged to yield the closed-loop transfer function, or gain, which is

$$A_{1} = \frac{S_{o}}{S_{1}} = \frac{A}{(1 + \beta A)} \tag{12.5}$$

As mentioned, signals  $S_i$ ,  $S_o$ ,  $S_{fb}$ , and  $S_e$  can be either currents or voltages; however, they do not need to be all voltages or all currents in a given feedback amplifier. In other words, there may be a combination of current and voltage signals in the same circuit.

Equation (12.5) can be written

$$A_f = \frac{A}{(1+\beta A)} = \frac{A}{1+T}$$

(12.6)

where  $T = \beta A$  is the loop gain. For negative feedback, we assume T to be a positive real factor. We will see later that the loop gain can become a complex function of frequency, but for the moment, we will assume that T is positive for negative feedback. We will also see that in some cases the gain will be negative (180 degree phase difference between input and output signals) which means

<sup>&</sup>lt;sup>1</sup>In this chapter,  $\beta$  is the feedback transfer function, rather than the transistor current gain. The parameter  $h_{FE}$  will be used as the transistor current gain. Normally,  $h_{FE}$  indicates the dc current gain and  $h_{fe}$  indicates the ac current gain. However, as usual, we neglect any difference between the two parameters and assume  $h_{FE} = h_{fe}$ .

that the feedback transfer function  $\beta$  will also be a negative quantity for a negative feedback circuit.

Combining Equations (12.1) and (12.2), we obtain the loop gain relationship

$$T = A\beta = \frac{S_{fb}}{S_c} \tag{12.7}$$

Normally, the error signal is small, so the expected loop gain is large. If the loop gain is large so that  $\beta A \gg 1$ , then, from Equation (12.6), we have

$$A_f \cong \frac{A}{\beta A} = \frac{1}{\beta} \tag{12.8}$$

and the gain or transfer function of the feedback amplifier essentially becomes a function of the feedback network only.

The feedback circuit is usually composed of passive elements, which means that the feedback amplifier gain is almost completely independent of the basic amplifier properties, including individual transistor parameters. Since the feedback amplifier gain is a function of the feedback elements only, the closed-loop gain can be designed to be a given value. This property was demonstrated in Chapter 9, where we showed that the closed-loop gain of ideal op-amp circuits is a function of the feedback elements only. The individual transistor parameters may vary widely, and may depend on temperature and frequency, but the feedback amplifier gain is constant. The net results of negative feedback is stability in the amplifier characteristics.

In general, the magnitude and phase of the loop gain are functions of frequency, and they become important when we discuss the stability of feedback circuits.

**Example 12.1 Objective:** Calculate the feedback transfer function  $\beta$ , given A and  $A_{\ell}$ .

#### Case A:

Assume that the open-loop gain of a system is  $A = 10^5$  and the closed-loop gain is  $A_f = 50$ .

Solution: From Equation (12.5), the closed-loop gain is

$$A_f = \frac{A}{(1 + \beta A)}$$

Therefore,

$$50 = \frac{10^5}{1 + \beta(10^5)}$$

which yields  $\beta = 0.01999$  or  $1/\beta = 50.025$ .

#### Case B:

Now assume that the open-loop gain is  $A = -10^5$  and the closed-loop gain is  $A_f = -50$ .

Solution: Again, from Equation (12.5), the closed-loop gain is

$$A_f = \frac{A}{(1 + \beta A)}$$

so that

$$-50 = \frac{-10^5}{1 + \beta(-10^5)}$$

which yields  $\beta = -0.01999$  or  $1/\beta = -50.025$ .

**Comment:** From these typical parameter values, we see that  $A_f \cong 1/\beta$ , as Equation (12.8) predicts. We also see that if the open-loop gain A is negative, then the closed-loop gain  $A_f$  and feedback transfer function  $\beta$  will also be negative for a negative feedback network.

Assuming a large loop gain, the output signal, from Equation (12.5), becomes

$$S_{\alpha} = \left(\frac{A}{1 + \beta A}\right) S_{i} \cong \frac{1}{\beta} \cdot S_{i} \tag{12.9}$$

Substituting Equation (12.9) into (12.3), we obtain the error signal,

$$S_{i} = S_{i} - \beta S_{o} \cong S_{i} - \beta \left(\frac{S_{i}}{\beta}\right) = 0$$

(12.10)

With a large loop gain, the error signal decreases to almost zero. We will see this result again as we consider specific feedback circuits throughout the chapter.

## **Test Your Understanding**

**12.1** The open-loop gain of an amplifier is  $A = 10^4$ , and the closed-loop gain is  $A_f = 20$ . (a) What is the feedback transfer function  $\beta$ ? (b) What is the ratio of  $A_f$  to  $(1/\beta)$ ? (Ans. (a)  $\beta = 0.0499$  (b) 0.998)

**12.2** The closed-loop gain of a feedback amplifier is  $A_f = 80$ , and the feedback transfer function is  $\beta = 0.0120$ . What is the value of the open-loop gain A? (Ans. A = 2000)

# 12.2.2 Gain Sensitivity

As previously stated, if the loop gain  $T = \beta A$  is very large, the overall gain of the feedback amplifier is essentially a function of the feedback network only. We can quantify this characteristic.

If the feedback transfer function  $\beta$  is a constant, then taking the derivative of  $A_{\ell}$  with respect to  $A_{\ell}$ , from Equation (12.5), produces

$$\frac{dA_f}{dA} = \frac{1}{(1+\beta A)} - \frac{A}{(1+\beta A)^2} \cdot \beta = \frac{1}{(1+\beta A)^2}$$

(12.11(a))

$$dA_f = \frac{dA}{(1+\beta A)^2}$$

(12.11(b))

Dividing both sides of Equation (12.11(b)) by the closed-loop gain yields

$$\frac{dA_t}{A_f} = \frac{\frac{dA}{(1+\beta A)^2}}{\frac{A}{1+\beta A}} = \frac{1}{(1+\beta A)} \cdot \frac{dA}{A} = \left(\frac{A_t}{A}\right) \frac{dA}{A} \tag{12.12}$$

Equation (12.12) shows that the percent change in the closed-loop gain  $A_f$  is less than the corresponding percent change in the open-loop gain A by the factor  $(1 + \beta A)$ . The change in open-loop gain may result from variations in individual transistor parameters in the basic amplifier.

**Example 12.2 Objective:** Calculate the percent change in the closed-loop gain  $A_f$ , given a change in the open-loop gain A.

Using The same parameter values as in Example 12.1, we have  $A = 10^5$ ,  $A_f = 50$ , and  $\beta = 0.01999$ . Assume that the change in the open-loop gain is  $dA = 10^4$  (a 10 percent change).

Solution: From Equation (12.12), we have

$$dA_t = \frac{A_t}{(1+\beta A)} \cdot \frac{dA}{A} = \frac{50}{[1+(0.01999)(10^5)]} \cdot \frac{10^4}{10^5} = 2.5 \times 10^{-3}$$

The percent change is then

$$\frac{dA_f}{A_f} = \frac{2.5 \times 10^{-3}}{50} = 5 \times 10^{-5} \Rightarrow 0.005\%$$

compared to the 10 percent change assumed in the open-loop gain.

Comment: From this example, we see that the resulting percent change in the closed-loop gain is substantially less than the percent change in the open-loop gain. This is one of the principal advantages of negative feedback.

From Equation (12.12), the change in  $A_f$  is reduced by the factor  $(1 + \beta A)$  compared to the change in A. The term  $(1 + \beta A)$  is called the **densensitivity** factor.

#### **Test Your Understanding**

- **12.3** Consider a general feedback system with parameters  $A = 10^6$  and  $A_f = 100$ . If the magnitude of A decreases by 20 percent, what is the corresponding percent change in  $A_f$ ? (Ans. 0.002%)

- **12.4** The gain factors in a feedback system are  $A = 5 \times 10^5$  and  $A_f = 100$ . Parameter  $A_f$  must not change more than  $\pm 0.001$  percent because of a change in A. What is the maximum allowable variation in A? (Ans.  $\pm 5\%$ )

#### 12.2.3 Bandwidth Extension

The amplifier bandwidth is a function of feedback. Assume the frequency response of the basic amplifier can be characterized by a single pole. We can then write

$$A(s) = \frac{A_a}{1 + \frac{s}{\omega_H}} \tag{12.13}$$

where  $A_o$  is the low-frequency or midband gain, and  $\omega_H$  is the upper 3 dB or corner frequency.

The closed-loop gain of the feedback amplifier can be expressed as

$$A_f(s) = \frac{A(s)}{(1 + \beta A(s))}$$

(12.14)

where we assume that the feedback transfer function  $\beta$  is independent of frequency. Substituting Equation (12.13) into Equation (12.14), we can write the closed-loop gain in the form

$$A_f(s) = \frac{A_a}{(1 + \beta A_a)} \cdot \frac{1}{1 + \frac{s}{\omega_H(1 + \beta A_a)}}$$

(12.15)

From Equation (12.15), we see that the low-frequency closed-loop gain is smaller than the open-loop gain by a factor of  $(1 + \beta A_o)$ , but the closed-loop 3dB frequency is larger than the open-loop value by a factor of  $(1 + \beta A_o)$ .

If we multiply the low-frequency open-loop gain  $A_o$  by the bandwidth (3 dB frequency)  $\omega_H$ , we obtain  $A_o\omega_H$ , which is the gain-bandwidth product. The product of the low-frequency closed-loop gain and the closed-loop bandwidth is

$$\frac{A_o}{(1+\beta A_o)}[\omega_H(1+\beta A_o)] = A_o\omega_H \tag{12.16}$$

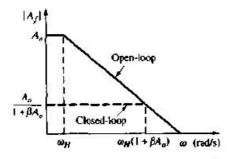

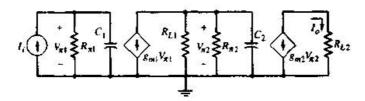

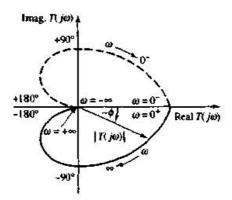

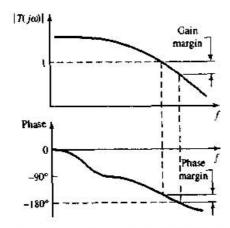

Equation (12.16) states that the gain-bandwidth product of a feedback amplifier is a constant. That is, for a given circuit, we can increase the gain at the expense of a reduced bandwidth, or we can increase the bandwidth at the expense of a reduced gain. This property is illustrated in Figure 12.2.

Figure 12.2 Open-loop and closed-loop gain versus frequency, illustrating bandwidth extension

Example 12.3 Objective: Determine the bandwidth of a feedback amplifier.

Consider a feedback amplifier with an open-loop low-frequency gain of  $A_n = 10^4$ , an open-loop bandwidth of  $\omega_R = (2\pi)(100)$  rad/s, and a closed-loop low-frequency gain of  $A_I(0) = 50$ .

Solution: From Equation (12.15), the low-frequency closed-loop gain is

$$A_f(0) = \frac{A_o}{(1 + \beta A_o)}$$

OF

$$50 = \frac{10^4}{(1 + \beta A_0)}$$

which yields

$$(1+\beta A_o) = \frac{10^4}{50} = 200$$

From Equation (12.15), the closed-loop bandwidth is

$$\omega_{H} = \omega_{H}(1 + \beta A_{0}) = (2\pi)(100)(200) = (2\pi)(20 \times 10^{3})$$

**Comment:** The bandwidth increases from 100 Hz to 20 kHz as the gain decreases from  $10^4$  to 50.

#### **Test Your Understanding**

- **12.5** A feedback amplifier has an open-loop low-frequency gain of  $A_0 = 10^5$ , an open-loop bandwidth of  $\omega_B = (2\pi)(10)$  rad/s, and a closed-loop low-frequency gain of  $A_f(0) = 100$ . Determine the bandwidth of the closed-loop system. (Ans.  $\omega = (2\pi)(10^4)$  rad/s)

- **12.6** In a feedback amplifier, the open-loop low-frequency gain is  $A_0 = 10^6$  and the open-loop 3 dB frequency is 8 Hz. If the bandwidth of the closed-loop system is 250 kHz, what is the maximum allowable value of the closed-loop low-frequency gain? (Ans.  $A_f$  (0) = 32)

#### 12.2.4 Noise Sensitivity

In any electronic system, unwanted random and extraneous signals may be present in addition to the desired signal. These random signals are called **noise**. Electronic noise can be generated within an amplifier, or may enter the amplifier along with the input signal. Negative feedback may reduce the noise level in amplifiers; more accurately, it may increase the **signal-to-noise ratio**. More precisely, feedback can help reduce the effect of noise generated in an amplifier, but it cannot reduce the effect when the noise is part of the input signal.

The input signal-to-noise ratio is defined as

$$(SNR)_i = \frac{S_i}{N_i} = \frac{v_i}{v_n}$$

(12.17)

where  $S_i = v_i$  is the input source signal and  $N_i = v_n$  is the input noise signal. The output signal-to-noise ratio is

$$(SNR)_o = \frac{S_o}{N_o} = \frac{A_{Ti}S_i}{A_{To}N_i}$$

(12.18)

where the desired output signal is  $S_o = A_{Ti}S_i$  and the output noise signal is  $N_o = A_{Tn}N_i$ . The parameter  $A_{Ti}$  is the amplification factor that multiplies the source signal, and the parameter  $A_{Ti}$  is the amplification factor that multiplies the noise signal. A large signal-to-noise ratio allows the signal to be detected without any loss of information. This is a desirable characteristic.

The following example compares the signal and noise amplification factors, which may or may not be equal.

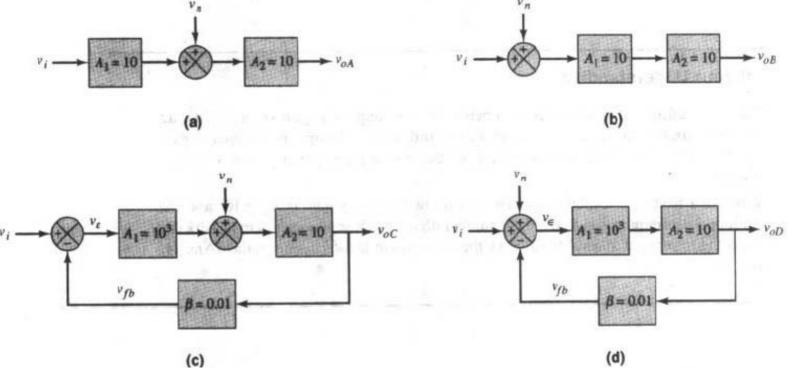

**Example 12.4 Objective:** Determine the effect of feedback on the source signal and noise signal levels.

Consider the four possible amplifier configurations shown in Figure 12.3. The amplifiers are designed to provide the same output signal voltage. Determine the effect of the noise signal  $v_n$ .

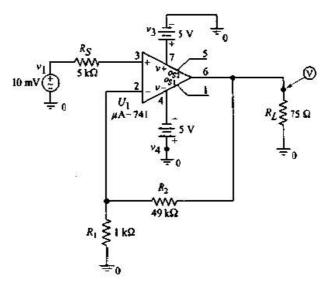

Figure 12.3 Four amplifier configurations with different input noise sources

Solution: Figure 12.3(a): Two open-loop amplifiers are in a cascade configuration, and the noise signal is generated between the two amplifiers. The output voltage is

$$v_{oa} = A_1 A_2 v_i + A_2 v_n = 100 v_i = 10 v_n$$

Therefore, the output signal-to-noise ratio is

$$\frac{S_o}{N_a} = \frac{100v_i}{10v_n} = 10\frac{S_i}{N_i}$$

Solution: Figure 12.3(b): Two open-loop amplifiers are in a cascade configuration, and the noise is part of the input signal. The output voltage is

$$v_{ob} = A_1 A_2 v_i + A_1 A_2 v_n = 100 v_i + 100 v_n$$

Therefore, the output signal-to-noise ratio is

$$\frac{S_o}{N_o} = \frac{100v_i}{100v_n} = \frac{S_i}{N_i}$$

Solution: Figure 12.3(c): Two amplifiers are in a feedback configuration, and the noise signal is generated between the two amplifiers. The output voltage is

$$v_{oc} = A_1 A_2 v_c + A_2 v_n$$

and the feedback signal is

$$v_{tb} = \beta v_{ac}$$

Then.

$$v_{\epsilon} = v_i - v_{fh} = v_f - \beta v_{oc}$$

therefore,

$$v_{oc} = A_1 A_2 (v_i - \beta v_{oc}) + A_2 v_n$$

10

$$v_{oi} = \frac{A_1 A_2}{(1 + \beta A_1 A_2)} \cdot v_i + \frac{A_2}{(1 + \beta A_1 A_2)} \cdot v_H \cong 100 v_i + 0.1 v_u$$

The output signal-to-noise ratio is

$$\frac{S_o}{N_o} = \frac{100v_i}{0.1v_o} = 1000 \frac{S_i}{N_i}$$

Solution: Figure 12.3(d): A basic feedback configuration, and the noise is part of the input signal. The output voltage is

$$v_{od} = \frac{A_1 A_2}{(1 + \beta A_1 A_2)} (v_i + v_n) \cong 100 v_i + 100 v_n$$

Therefore, the output signal-to-noise ratio is

$$\frac{S_o}{N_o} = \frac{100v_i}{100v_o} = \frac{S_i}{N_o}$$

**Comment:** Comparing the four configurations, we see that Figure 12.3(c) produces the largest output signal-to-noise ratio. This configuration may occur when amplifier  $A_2$  is an audio power-amplifier stage, in which large currents can produce excessive noise, and when amplifier  $A_1$  corresponds to a low-noise preamplifier, which provides most of the voltage gain.

We must emphasize that the increased signal-to-noise ratio due to feed-back occurs only in specific situations. As indicated in Figure 12.3(d), when noise is effectively part of the amplifier input signal, the feedback mechanism does not improve the ratio.

#### 12.2.5 Reduction of Nonlinear Distortion

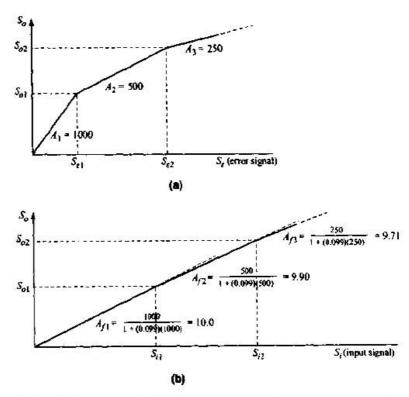

Distortion in an output signal is caused by a change in the basic amplifier gain or a change in the slope of the basic amplifier transfer function. The change in gain is a function of the nonlinear properties of bipolar and MOS transistors used in the basic amplifier.

Assume the basic amplifier, or open-loop, transfer function is as shown in Figure 12.4(a), which shows changes in gain as the input signal changes. The gain values are shown on the figure. When this amplifier is incorporated in a feedback circuit with a feedback transfer function of  $\beta = 0.099$ , the resulting closed-loop transfer characteristics are shown in Figure 12.4(b). This transfer function also has changes in gain but, whereas the open-loop gain changes by a factor of 2, the closed-loop gain changes by only 1 percent and 2 percent, respectively. A smaller change in gain means less distortion in the output signal of the negative feedback amplifier.

Figure 12.4 (a) Basic amplifier (open-loop) transfer characteristics; (b) closed-loop transfer characteristics

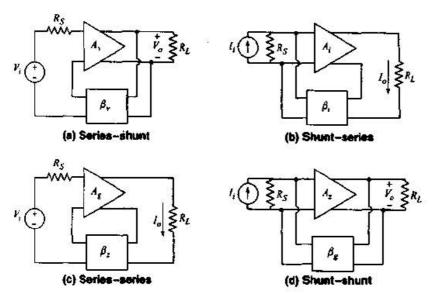

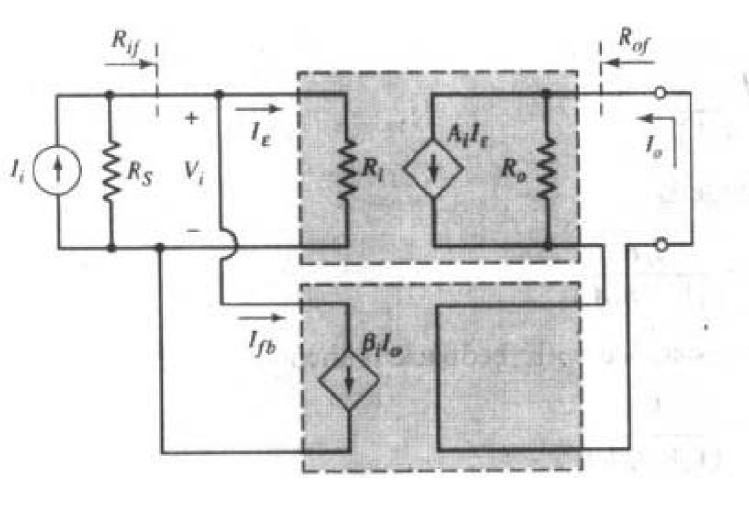

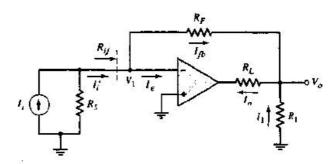

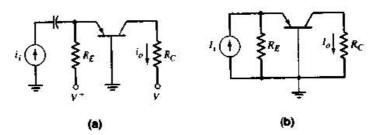

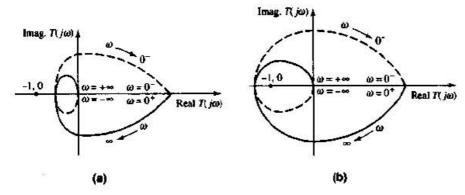

### 12.3 IDEAL FEEDBACK TOPOLOGIES

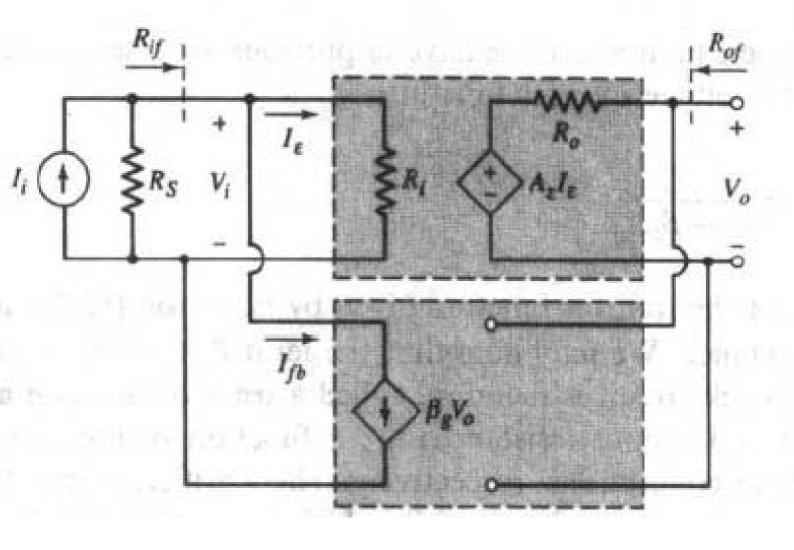

There are four basic feedback topologies, based on the parameter to be amplified (voltage or current) and the output parameter (voltage or current). The four feedback circuit categories can be described by the types of connections at the input and output of circuit. The four types of connections are shown in Figure 12.5. The four connections are referred to as: series—shunt (voltage amplifier), shunt—series (current amplifier), series—series (transconductance

Figure 12.5 Basic feedback connections

amplifier), and shunt-shunt (transresistance amplifier). The first term refers to the connection at the amplifier input, and the second term refers to the connection at the output. Also, the type of connection determines which parameter (voltage or current) is sampled at the output and which parameter is amplified. The connections also determine the feedback amplifier characteristics—in particular, the input and output resistances. The resistance parameters become an important circuit property, when, for example, we consider voltage amplifiers versus current amplifiers.

In this section, we will determine the ideal transfer functions and the ideal input and output resistances of each of the four feedback topologies. In later sections, we will compare actual versus ideal feedback circuit characteristics.

As a note, the ideal topologies are small-signal equivalent circuits; therefore, phasor notation is used throughout this analysis.

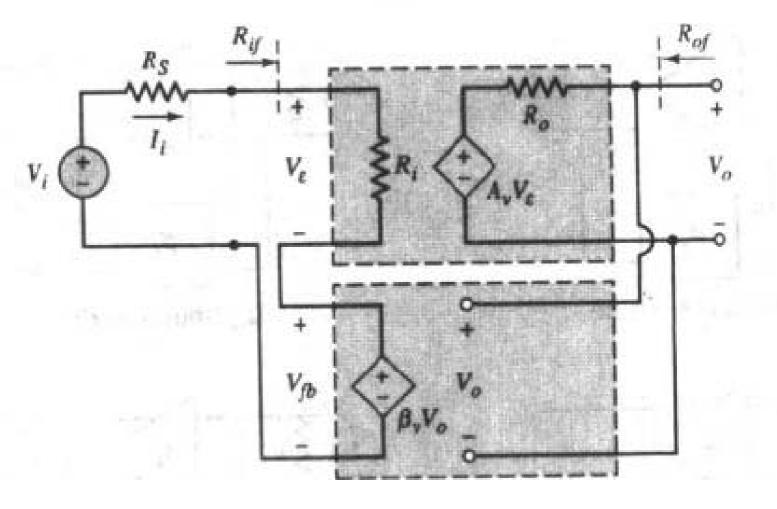

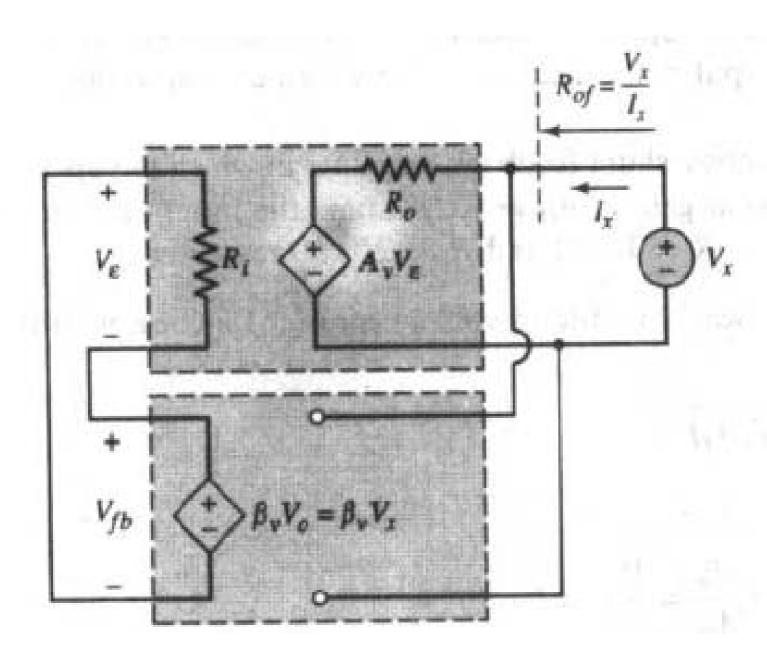

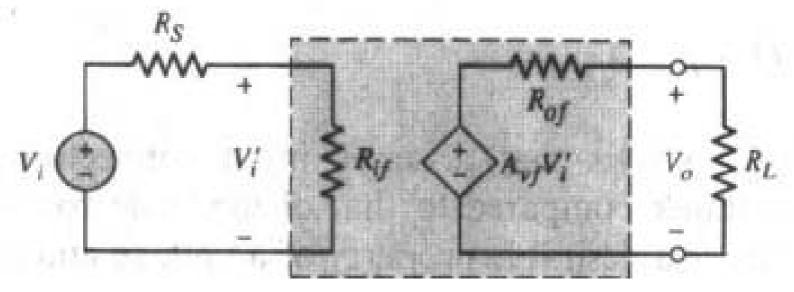

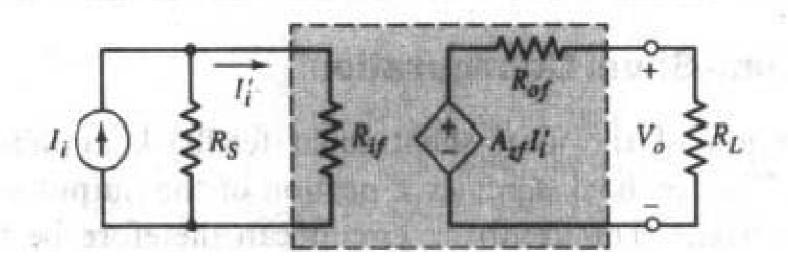

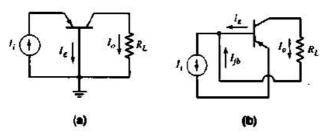

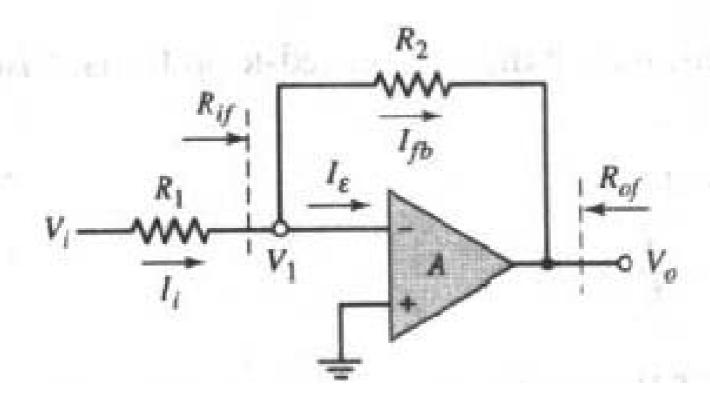

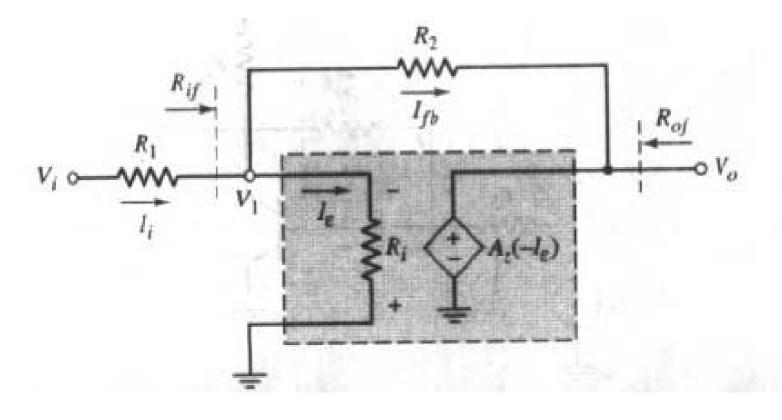

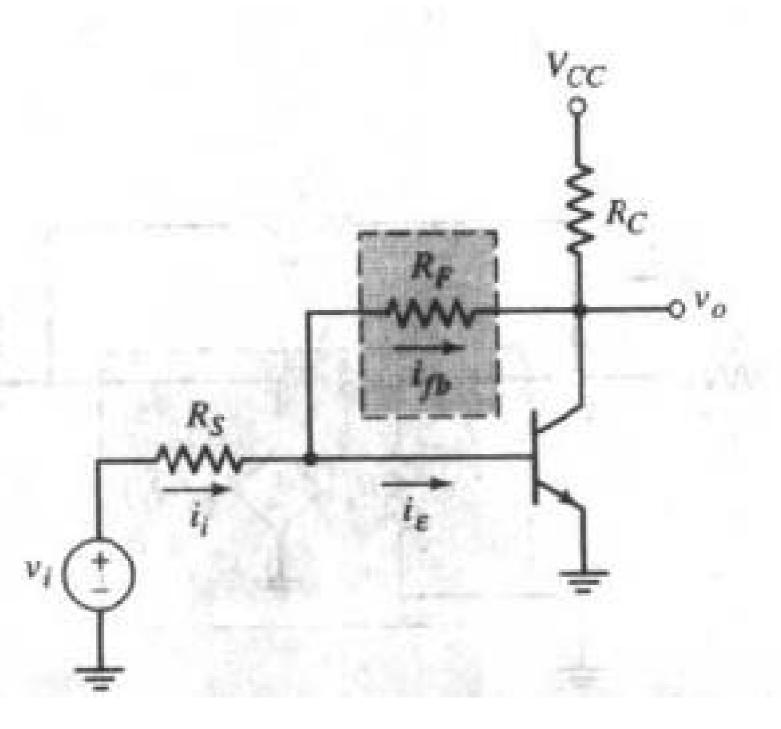

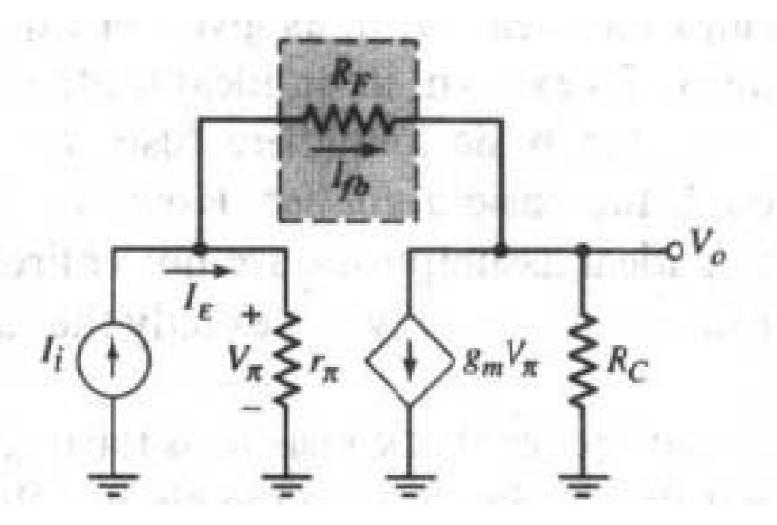

## 12.3.1 Series-Shunt Configuration

The configuration of an ideal series—shunt feedback amplifier is shown in Figure 12.6. The circuit consists of a basic voltage amplifier with an input resistance  $R_i$  and an open-loop voltage gain  $A_v$ . The feedback circuit samples the output voltage and produces a feedback voltage  $V_{fb}$ , which is in series with the input signal voltage  $V_i$ . In this ideal configuration, the input resistance to the feedback circuit is infinite; therefore, there is no loading effect on the output of the basic amplifier due to the feedback circuit.

Voltage  $V_{\epsilon}$  is the difference between the input signal voltage and the feedback voltage and is called an error signal. The error signal is amplified in the basic voltage amplifier. We can recognize the series connection on the input and the shunt connection of the output for this configuration.

The circuit is a voltage-controlled voltage source and is an ideal voltage amplifier. The feedback circuit samples the output voltage and provides a feedback voltage in series with the source voltage. For example, an increase

Flaure 12.6 Ideal series-shunt feedback topology

in the output voltage produces an increase in the feedback voltage, which in turn decreases the error voltage due to the negative feedback. Then, the smaller error voltage is amplified producing a smaller output voltage, which means that the output signal tends to be stabilized.