#

# **Analog Engineer's**

Circuit Cookbook: Op Amps

# **TEXAS INSTRUMENTS**

# Analog Engineer's Circuit Cookbook: Op Amps

First Edition SLYY137 - 03/2018

Edited by:

Tim Green, Pete Semig and Collin Wells

Special thanks for technical contribution:

Zak Kaye

Errol Leon

Tim Claycomb

Takahiro Saito

Masashi Miyagawa

Gustaf Falk Olson

Peter Iliya

# Analog Engineer's Circuit Cookbook: Op Amps (First Edition)

#### Message from the editors:

The Analog Engineer's Circuit Cookbook: Op Amps provides operational amplifier (op amp) sub-circuit ideas that can be quickly adapted to meet your specific system needs. Each circuit is presented as a "definition-by-example." They include step-by-step instructions, like a recipe, with formulas enabling you to adapt the circuit to meet your design goals. Additionally, all circuits are verified with SPICE simulations.

We've provided at least one recommended op amp for each circuit, but you can swap it with another device if you've found one that's a better fit for your design. You can search our large portfolio of op amps at <u>ti.com/opamps</u>.

Our circuits require a basic understanding of op amp concepts. If you're new to op amp design, we highly recommend completing our TI Precision Labs (TIPL) training series. TIPL includes courses on introductory topics, such as device architecture, as well as advanced, application-specific problem-solving, using both theory and practical knowledge. Check out our curriculum for op amps, ADCs and more at: ti.com/precisionlabs.

We hope you find this collection of op amp circuits helpful in developing your designs. Our goal is to regularly update the cookbook with valuable op-amp-circuit building blocks. You can check to see if your version is the latest at **ti.com/circuitcookbooks**. If you have input on any of the existing circuits or would like to request additional op amp cookbook circuits for the next edition please contact us at: **opampcookbook@list.ti.com**.

#### Additional resources to explore

#### **TI Precision Labs**

#### ti.com/precisionlabs

- On-demand courses and tutorials ranging from introductory to

- advanced concepts that focus on application-specific problem solving • Hands-on labs and evaluation modules (EVM) available

- TIPL Op Amps experimentation platform, ti.com/TIPL-amp-evm

- TIPL SAR ADC experimentation platform, ti.com/TIPL-adc-evm

#### Analog Engineer's Pocket Reference

#### ti.com/analogrefguide

- PCB, analog and mixed-signal design formulae; includes conversions, tables and equations

- e-book, iTunes app and hardcopy available

#### The Signal e-book

#### ti.com/signalbook

Op amp e-book with short, bite-sized lessons on design topics such as offset voltage, input bias current, stability, noise and more

#### **TI Designs**

#### ti.com/tidesigns

Ready-to-use reference designs with theory, calculations, simulations schematics, PCB files and bench test results

#### TINA-TI<sup>™</sup> simulation software

#### ti.com/tool/tina-ti

- Complete SPICE simulator for DC, AC, transient and noise analysis

- Includes schematic entry and post-processor for waveform math

#### Analog Engineer's Calculator

#### ti.com/analogcalc

ADC and amplifier design tools, noise and stability analysis, PCB and sensor tools

#### Analog Wire Blog

#### ti.com/analogwire

Technical blogs written by analog experts that include tips, tricks and design techniques

#### TI E2E<sup>™</sup> Community

#### ti.com/e2e

• Support forums for all TI products

#### Op Amp Parametric Quick Search

#### ti.com/opamp-search

Search for precision, high-speed, general-purpose, ultra-low-power, audio and power op amps

#### Op Amp Parametric Cross-Reference

#### ti.com/opampcrossreference

• Find similar TI op amps using competitive part numbers

# DIY Amplifier Circuit Evaluation Module (DIYAMP-EVM) ti.com/DIYAMP-EVM

Single-channel circuit evaluation module providing SC70, SOT23 and SOIC package options in 12 popular amplifier configurations

#### Dual-Channel DIY Amplifier Circuit Evaluation Module (DUAL-DIYAMP-EVM)

#### ti.com/dual-diyamp-evm

Dual-channel circuit evaluation module in an SOIC-8 package with 10

popular amplifier configurations

The platform bar is a trademark of Texas Instruments. © 2018 Texas Instruments Incorporated.

# **Table of Contents**

## **Basic Circuits**

| Buffer (Follower) Circuit                 | 5 |

|-------------------------------------------|---|

| Inverting Amplifier Circuit               | 9 |

| Non-inverting Amplifier Circuit14         | 4 |

| Inverting Summer Circuit18                | 8 |

| Difference Amplifier (Subtractor) Circuit | 3 |

| Integrator Circuit27                      | 7 |

| Differentiator Circuit                    | 2 |

# **Current Sensing**

| Transimpedance Amplifier Circuit                                 | 37  |

|------------------------------------------------------------------|-----|

| Single-Supply, Low-Side, Unidirectional Current Sensing Solution | ion |

| with Output Swing to GND Circuit                                 | 41  |

| Low-Side, Bidirectional Current Sensing Circuit                  | 45  |

| 3-Decade, Load Current Sensing Circuit                           | 50  |

# **Signal Sources**

# **Filters**

| AC Coupled (HPF) Inverting Amplifier Circuit     | 58 |

|--------------------------------------------------|----|

| AC Coupled (HPF) Non-Inverting Amplifier Circuit | 62 |

| Band Pass Filtered Inverting Attenuator Circuit  | 66 |

# Non-Linear Circuits (Rectifiers/Clamps/Peak Detectors)

| Half-Wave Rectifier Circuit                                  | 70  |

|--------------------------------------------------------------|-----|

| Full-Wave Rectifier Circuit                                  | 74  |

| Single-Supply, Low-Input Voltage Full-Wave Rectifier Circuit | .78 |

| Slew Rate Limiter Circuit                                    | 82  |

# **Signal Conditioning**

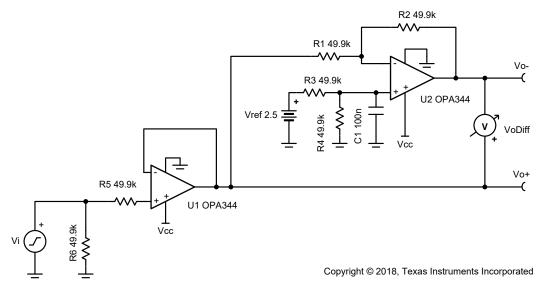

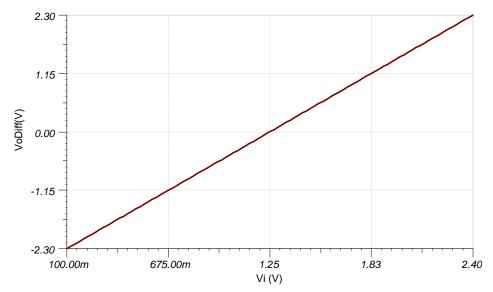

| Single-Ended Input to Differential Output Circuit                             | .86 |

|-------------------------------------------------------------------------------|-----|

| Inverting Op Amp With Inverting Positive Reference<br>Voltage Circuit         | .90 |

| Non-Inverting Op Amp With Inverting Positive Reference<br>Voltage Circuit     | .94 |

| Non-Inverting Op Amp With Non-Inverting Positive Reference<br>Voltage Circuit | .98 |

| Inverting Op Amp With Non-Inverting Positive Reference<br>Voltage Circuit     | 102 |

# Comparators

| Comparator With and Without Hysteresis Circuit | 106 |

|------------------------------------------------|-----|

| Window Comparator Circuit                      | 110 |

# **Sensor Acquisition**

| Photodiode Amplifier ( | Circuit | 113 |

|------------------------|---------|-----|

|------------------------|---------|-----|

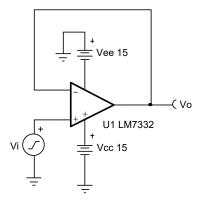

# Analog Engineer's Circuit: Op Amps SBOA269-February 2018

# Buffer (Follower) Circuit

#### **Design Goals**

| Input             |                   | Output            |                   | Freq.  | Freq. Supply    |                 |

|-------------------|-------------------|-------------------|-------------------|--------|-----------------|-----------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f      | V <sub>cc</sub> | V <sub>ee</sub> |

| -10V              | 10V               | -10V              | 10V               | 100kHz | 15V             | -15V            |

#### **Design Description**

This design is used to buffer signals by presenting a high input impedance and a low output impedance. This circuit is commonly used to drive low-impedance loads, analog-to-digital converters (ADC) and buffer reference voltages. The output voltage of this circuit is equal to the input voltage.

#### **Design Notes**

- 1. Use op amp linear output operating range, which is usually specified under the A<sub>OL</sub> test conditions.

- 2. The small-signal bandwidth is determined by the unity-gain bandwidth of the amplifier.

- 3. Check the maximum output voltage swing versus frequency graph in the datasheet to minimize slewinduced distortion.

- 4. The common mode voltage is equal to the input signal.

- 5. Do not place capacitive loads directly on the output that are greater than the values recommended in the datasheet.

- 6. High output current amplifiers may be required if driving low impedance loads.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the *Design References* section.

#### **Design Steps**

The tranfer function for this circuit is given below.

$V_0 = V_i$

Verify that the amplifier can acheive the desired output swing using the supply voltages provided. Use the output swing stated in the A<sub>OL</sub> test conditions. The output swing range of the amplifier must be greater than the output swing required for the design.

$-14V \le V_0 \le 14V$

- The output swing of the LM7332 using ±15-V supplies is greater than the required output swing of the design. Therefore, this requirement is met.

- Review the Output Voltage versus Output Current curves in the product datasheet to verify the desired output voltage can be acheived for the desired output current.

- 2. Verify the input common mode voltage of the amplifier will not be violated using the supply voltage provided. The input common mode voltage range of the amplifier must be greater than the input signal voltage range.

$-15.1 V \le V_{icm} \le 15.1 V$

- The input common-mode range of the LM7332 using ±15-V supplies is greater than the required input common-mode range of the design. Therefore, this requirement is met.

- 3. Calculate the minimum slew rate required to minimize slew-induced distortion.

$SR > 2 \times \pi \times Vp \times f = 2 \times \pi \times 10V \times 100 \text{kHz} = 6.28 \text{V} / \mu \text{s}$

- The slew rate of the LM7332 is 15.2V/ $\!\mu s.$  Therefore, this requirement is met.

- 4. Verify the device will have sufficient bandwidth for the desired output signal frequency.

fsignal < funity

100kHz < 7.5MHz

• The desired output signal frequency is less than the unity-gain bandwidth of the LM7332. Therefore, this requirement is met.

- ir

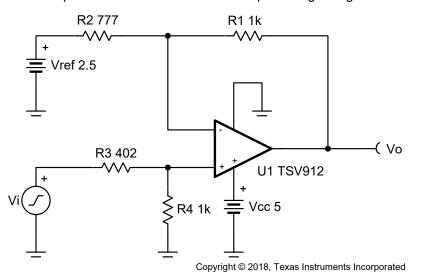

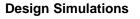

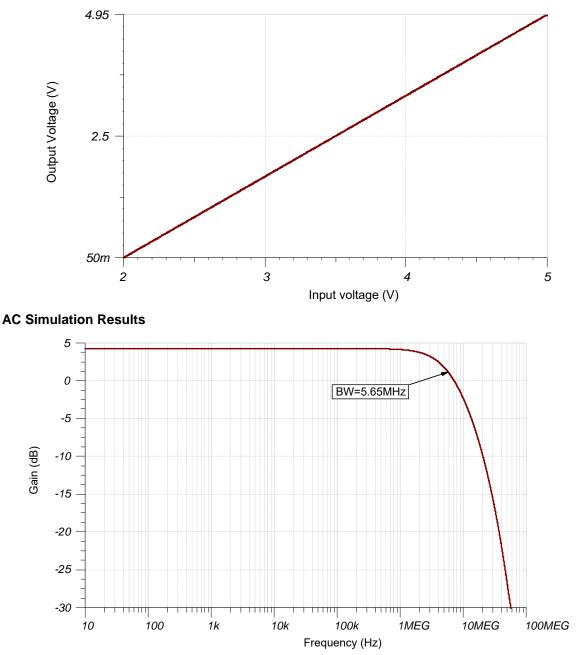

**Design Simulations**

Texas Instruments

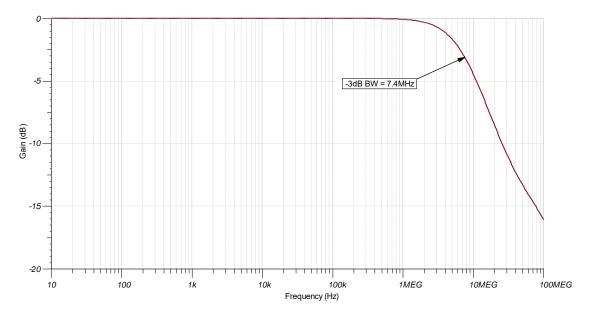

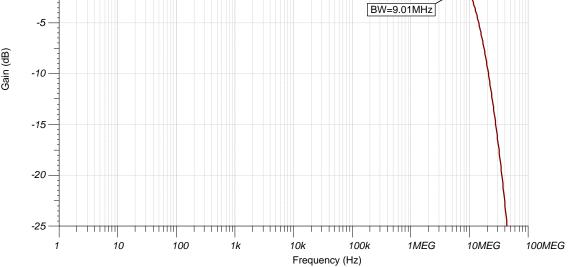

## **AC Simulation Results**

#### **Design References**

See TIPD128, www.ti.com/tool/tipd128

For more information on many op amp topics including common-mode range, output swing, bandwidth, slew rate, and how to drive an ADC please see TI Precision Labs.

#### Design Featured Op Amp

| LM7332                         |          |  |  |  |

|--------------------------------|----------|--|--|--|

| V <sub>ss</sub> 2.5V to 32V    |          |  |  |  |

| V <sub>inCM</sub> Rail-to-rail |          |  |  |  |

| V <sub>out</sub> Rail-to-rail  |          |  |  |  |

| <b>V</b> <sub>os</sub> 1.6mV   |          |  |  |  |

| l <sub>q</sub>                 | 2mA      |  |  |  |

| I <sub>b</sub>                 | 1µA      |  |  |  |

| UGBW 7.5MHz (±5-V supply)      |          |  |  |  |

| SR                             | 15.2V/µs |  |  |  |

| #Channels 2                    |          |  |  |  |

| www.ti.com/product/LM7332      |          |  |  |  |

#### **Design Alternate Op Amp**

| OPA192                     |              |  |  |  |

|----------------------------|--------------|--|--|--|

| V <sub>ss</sub>            | 4.5V to 36V  |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |  |

| <b>V</b> <sub>os</sub> 5μV |              |  |  |  |

| l <sub>q</sub> 1mA         |              |  |  |  |

| I <sub>b</sub>             | 5pA          |  |  |  |

| UGBW                       | 10MHz        |  |  |  |

| SR                         | 20V/µs       |  |  |  |

| #Channels                  | 1, 2, 4      |  |  |  |

| www.ti.com/product/opa192  |              |  |  |  |

# Analog Engineer's Circuit: Op Amps SBOA270-February 2018

# Inverting Amplifier Circuit

#### **Design Goals**

| Input             |                   | Output            |                   | Output Freq. Supply |                 | oply            |

|-------------------|-------------------|-------------------|-------------------|---------------------|-----------------|-----------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f                   | V <sub>cc</sub> | V <sub>ee</sub> |

| -7V               | 7V                | -14V              | 14V               | 3kHz                | 15V             | -15V            |

#### **Design Description**

This design inverts the input signal,  $V_i$ , and applies a signal gain of -2V/V. The input signal typically comes from a low-impedance source because the input impedance of this circuit is determined by the input resistor,  $R_1$ . The common-mode voltage of an inverting amplifier is equal to the voltage connected to the non-inverting node, which is ground in this design.

Copyright © 2018, Texas Instruments Incorporated

#### **Design Notes**

- 1. Use the op amp in a linear operating region. Linear output swing is usually specified under the A<sub>OL</sub> test conditions. The common-mode voltage in this circuit does not vary with input voltage.

- 2. The input impedance is determined by the input resistor. Make sure this value is large when compared to the source's output impedance.

- 3. Using high value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gainbandwidth product (GBP). Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>2</sub>. Adding a capacitor in parallel with R<sub>2</sub> will also improve stability of the circuit if high value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the Design References section.

#### **Design Steps**

The transfer function of this circuit is given below.

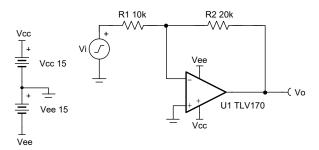

$$V_{o} = V_{i} \times \left(-\frac{R_{2}}{R_{1}}\right)$$

- 1. Determine the starting value of R<sub>1</sub>. The relative size of R<sub>1</sub> to the signal source's impedance affects the gain error. Assuming the signal source's impedance is low (for example, 100 $\Omega$ ), set R<sub>1</sub>=10k $\Omega$  for 1% gain error.

- $R_1 = 10 k\Omega$

- 2. Calculate the gain required for the circuit. Since this is an inverting amplifier use  $V_{iMin}$  and  $V_{oMax}$  for the calculation.

$$G = \frac{V_{oMax}}{V_{iMin}} = \frac{14V}{-7V} = -2\frac{V}{V}$$

3. Calculate R<sub>2</sub> for a desired signal gain of -2V/V.

$$\mathbf{G} = -\frac{\mathbf{R}_2}{\mathbf{R}_1} \rightarrow \mathbf{R}_2 = -\mathbf{G} \times \mathbf{R}_1 = -\left(-2\frac{\mathbf{V}}{\mathbf{V}}\right) \times 10 \mathbf{k}\Omega = 20 \mathbf{k}\Omega$$

4. Calculate the small signal circuit bandwidth to ensure it meets the 3kHz requirement. Be sure to use the noise gain, or non-inverting gain, of the circuit.

$$GBP_{TLV170} = 1.2MHz$$

٠

$$NG = \left(1 + \frac{R_2}{R_1}\right) = 3\frac{V}{V}$$

$$BW = \frac{GBP}{NG} = \frac{1.2MHz}{3V/V} = 400kHz$$

5. Calculate the minimum slew rate required to minimize slew-induced distortion.

$$V_p = \frac{SR}{2 \times \pi \times f} \rightarrow SR > 2 \times \pi \times f \times V_p$$

SR > 2 \times \pi \times 3kHz \times 14V = 263.89  $\frac{kV}{s} = 0.26 \frac{V}{\mu s}$

- SR<sub>TLV170</sub>=0.4V/ $\mu$ s, therefore it meets this requirement.

- 6. To avoid stability issues ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\begin{split} \frac{1}{2\times\pi\times(C_{cm}+C_{diff})\times(R_2\|R_1)} &> \frac{GBP}{NG} \\ \frac{1}{2\times\pi\times(3pF+3pF)\times\frac{20k\Omega\times10k\Omega}{20k\Omega+10k\Omega}} &> \frac{1.2MHz}{3V/V} \\ 43.77MHz &> 400kHz \end{split}$$

- C<sub>cm</sub> and C<sub>diff</sub> are the common-mode and differential input capacitances of the TLV170, respectively.

- Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

TEXAS INSTRUMENTS

#### www.ti.com

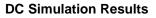

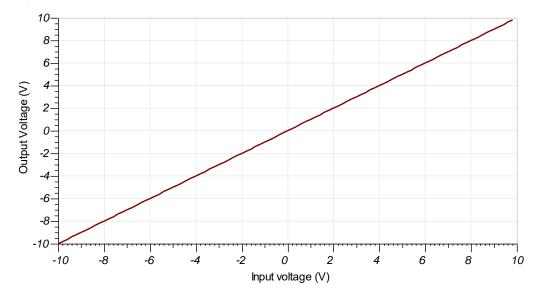

## **Design Simulations**

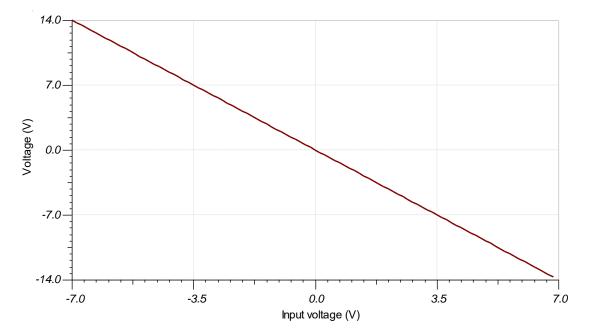

**DC Simulation Results**

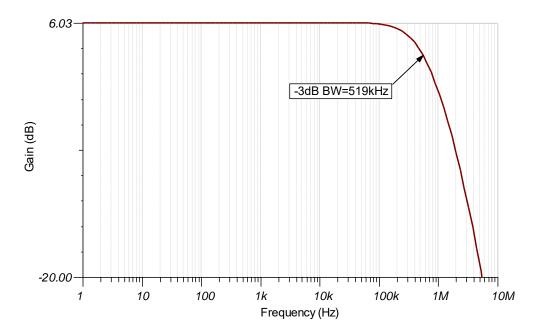

#### **AC Simulation Results**

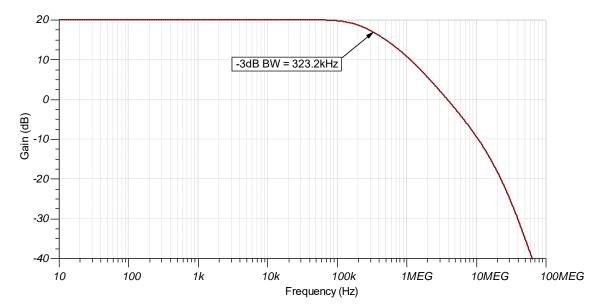

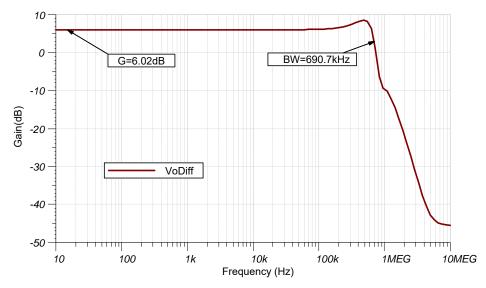

The bandwidth of the circuit depends on the noise gain, which is 3V/V. The bandwidth is determined by looking at the –3dB point, which is located at 3dB given a signal gain of 6dB. The simulation sufficiently correlates with the calculated value of 400kHz.

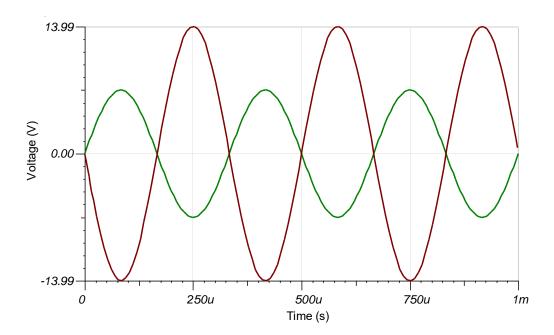

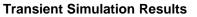

#### **Transient Simulation Results**

The output is double the magnitude of the input, and inverted.

#### **Design References**

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs.

#### **Design Featured Op Amp**

| TL                | TLV170                    |  |  |  |

|-------------------|---------------------------|--|--|--|

| V <sub>ss</sub>   | ±18V (36V)                |  |  |  |

| V <sub>inCM</sub> | (Vee-0.1V) to (Vcc-2V)    |  |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |  |

| V <sub>os</sub>   | 0.5mV                     |  |  |  |

| l <sub>q</sub>    | 125µA                     |  |  |  |

| l <sub>b</sub>    | 10pA                      |  |  |  |

| UGBW              | 1.2MHz                    |  |  |  |

| SR                | 0.4V/µs                   |  |  |  |

| #Channels         | 1, 2, 4                   |  |  |  |

| www.ti.com        | www.ti.com/product/tlv170 |  |  |  |

## **Design Alternate Op Amp**

| I                         | LMV358                                             |  |  |

|---------------------------|----------------------------------------------------|--|--|

| V <sub>ss</sub>           | 2.7 to 5.5V                                        |  |  |

| V <sub>inCM</sub>         | (V <sub>ee</sub> –0.2V) to (V <sub>cc</sub> –0.8V) |  |  |

| V <sub>out</sub>          | Rail-to-rail                                       |  |  |

| V <sub>os</sub>           | 1.7mV                                              |  |  |

| l <sub>q</sub>            | 210µA                                              |  |  |

| I <sub>b</sub>            | 15nA                                               |  |  |

| UGBW                      | 1MHz                                               |  |  |

| SR                        | 1V/µs                                              |  |  |

| #Channels                 | 1 (LMV321), 2 (LMV358), 4<br>(LMV324)              |  |  |

| www.ti.com/product/Imv358 |                                                    |  |  |

# Analog Engineer's Circuit: Op Amps SBOA271–January 2018

# Non-Inverting Amplifier Circuit

#### **Design Goals**

| Inj   | Input |       | tput  | Sup | oply |

|-------|-------|-------|-------|-----|------|

| ViMin | ViMax | VoMin | VoMax | Vcc | Vee  |

| -1V   | 1V    | -10V  | 10    | 15V | -15V |

#### **Design Description**

This design amplifies the input signal, V<sub>i</sub>, with a signal gain of 10V/V. The input signal may come from a high-impedance source (for example,  $M\Omega$ ) because the input impedance of this circuit is determined by the extremely high input impedance of the op amp (for example,  $G\Omega$ ). The common-mode voltage of a non-inverting amplifier is equal to the input signal.

#### **Design Notes**

- 1. Use the op amp linear output operating range, which is usually specified under the A<sub>OL</sub> test conditions. The common-mode voltage is equal to the input signal.

- 2. The input impedance of this circuit is equal to the input impedance of the amplifier.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. The small-signal bandwidth of a non-inverting amplifier depends on the gain of the circuit and the gain bandwidth product (GBP) of the amplifier. Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>1</sub>. Adding a capacitor in parallel with R<sub>1</sub> will also improve stability of the circuit if high-value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the *Design References* section.

#### **Design Steps**

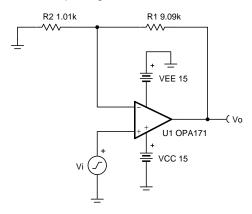

The transfer function for this circuit is given below.

$$V_{0} = V_{i} \times \left(1 + \frac{R_{1}}{R_{2}}\right)$$

1. Calculate the gain.

$$G = \frac{V_{o\_max} - V_{o\_min}}{V_{i\_max} - V_{i\_min}} \\ G = \frac{10V - (-10V)}{1 V - (-1V)} = 10V / V$$

2. Calculate values for R<sub>1</sub> and R<sub>2</sub>.

$$\begin{split} G &= 1 + \frac{R_1}{R_2} \\ Choose \quad R_1 &= 9.09 k\Omega \\ R_2 &= \frac{R_1}{G-1} = \frac{9.09 k\Omega}{(10 V/V) - 1} = 1.01 k\Omega \end{split}$$

3. Calculate the minimum slew rate required to minimize slew-induced distortion.

$SR > 2 \times \pi \times V_p \times f = 2 \times \pi \times 10V \times 20kHz = 1.257V / \mu s$

- The slew rate of the OPA171 is 1.5V/µs, therefore it meets this requirement.

- 4. To maintain sufficient phase margin, ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\begin{split} &\frac{1}{2\times\pi\times(C_{cm}+C_{diff})\times(R_1||R_2)} > \frac{GBP}{G} \\ &\frac{1}{2\times\pi\times(3pF+3pF)\times\frac{1.01k\Omega\times9.09k\Omega}{1.01k\Omega+9.09k\Omega}} > \frac{3MHz}{10V/V} \\ &29.18MHz > 300kHz \end{split}$$

- C<sub>om</sub> and C<sub>diff</sub> are the common-mode and differential input capacitances of the OPA171, respectively.

- Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

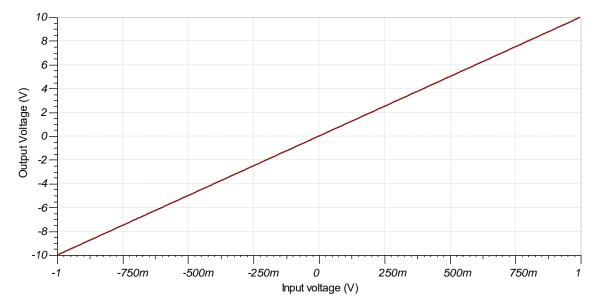

## **Design Simulations**

Texas Instruments

#### AC Simulation Results

#### **Design References**

For more information on many op amp topics including common-mode range, output swing, and bandwidth please visit TI Precision Labs.

#### **Design Featured Op Amp**

| OF                | OPA171                                           |  |  |

|-------------------|--------------------------------------------------|--|--|

| V <sub>ss</sub>   | 2.7V to 36V                                      |  |  |

| V <sub>inCM</sub> | (V <sub>ee</sub> –0.1V) to (V <sub>cc</sub> –2V) |  |  |

| V <sub>out</sub>  | Rail-to-rail                                     |  |  |

| V <sub>os</sub>   | 250µV                                            |  |  |

| l <sub>q</sub>    | 475µA                                            |  |  |

| I <sub>b</sub>    | 8pA                                              |  |  |

| UGBW              | 3MHz                                             |  |  |

| SR                | 1.5V/µs                                          |  |  |

| #Channels         | 1, 2, 4                                          |  |  |

| www.ti.com/       | www.ti.com/product/opa171                        |  |  |

## **Design Alternate Op Amp**

| OP                | OPA191                    |  |  |

|-------------------|---------------------------|--|--|

| V <sub>ss</sub>   | 4.5V to 36V               |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |

| V <sub>os</sub>   | 5µV                       |  |  |

| l <sub>q</sub>    | 140µA                     |  |  |

| l <sub>b</sub>    | 5pA                       |  |  |

| UGBW              | 2.5MHz                    |  |  |

| SR                | 7.5V/µs                   |  |  |

| #Channels         | 1, 2, 4                   |  |  |

| www.ti.com/p      | www.ti.com/product/OPA191 |  |  |

# Analog Engineer's Circuit: Op Amps SBOA272-February 2018

# **Inverting Summer Circuit**

#### **Design Goals**

| Inp                | ut 1               | Inp                | ut 2               | Out               | iput              | Freq. | Sup             | oply            |

|--------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------|-----------------|-----------------|

| V <sub>i1Min</sub> | V <sub>i1Max</sub> | V <sub>i2Min</sub> | V <sub>i2Max</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f     | V <sub>cc</sub> | V <sub>ee</sub> |

| –5V                | 5V                 | –250mV             | 250mV              | -4.9V             | 4.9V              | 10kHz | 5V              | -5V             |

#### **Design Description**

This design sums (adds) and inverts two input signals,  $V_{i1}$  and  $V_{i2}$ . The input signals typically come from low-impedance sources because the input impedance of this circuit is determined by the input resistors,  $R_1$  and  $R_2$ . The common-mode voltage of an inverting amplifier is equal to the voltage connected to the non-inverting node, which is ground in this design.

Copyright © 2018, Texas Instruments Incorporated

#### **Design Notes**

- 1. Use the op amp in a linear operating region. Linear output swing is usually specified under the A<sub>OL</sub> test conditions. The common-mode voltage in this circuit does not vary with input voltage.

- 2. The input impedance is determined by the input resistors. Make sure these values are large when compared to the output impedance of the source.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gainbandwidth product (GBP). Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>3</sub>. Adding a capacitor in parallel with R<sub>3</sub> will also improve stability of the circuit if high-value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the *Design References* section.

#### **Design Steps**

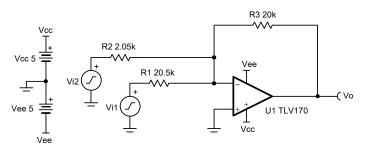

The transfer function for this circuit is given below.

$$V_{0} = V_{i 1} \times \left(-\frac{R_{3}}{R_{1}}\right) + V_{i 2} \times \left(-\frac{R_{3}}{R_{2}}\right)$$

- 1. Select a reasonable resistance value for R<sub>3</sub>.  $R_3 = 20 k\Omega$

- 2. Calculate gain required for V<sub>i1</sub>. For this design, half of the output swing is devoted to each input.

$$|G_{VII}| = \left| \frac{\frac{V_{oMax} - V_{oMin}}{2}}{V_{i \ 1 \ Max} - V_{i \ 1 \ Min}} \right| = \left| \frac{\frac{4.9V - (-4.9V)}{2}}{2.5V - (-2.5V)} \right| = 0.98 \frac{V}{V} = -0.175 dB$$

3. Calculate the value of  $R_1$ .

$$|G_{Vi1}| = \frac{R_3}{R_1} \rightarrow R_1 = \frac{R_3}{|G_{Vi1}|} = \frac{20k\Omega}{0.98V/V} = 20.4k\Omega \approx 20.5k\Omega \text{ (Standard Value)}$$

4. Calculate gain required for V<sub>i2</sub>. For this design, half of the output swing is devoted to each input.

$$|G_{V2}| = \left| \frac{\frac{V_{oMax} - V_{oMin}}{2}}{V_{i \ 2 \ Max} - V_{i \ 2 \ Min}} \right| = \left| \frac{\frac{4.9V - (-4.9V)}{2}}{250mV - (-250mV)} \right| = 9.8\frac{V}{V} = 19.82dB$$

5. Calculate the value of R<sub>2</sub>.

$$|G_{Vi2}| = \frac{R_3}{R_2} \rightarrow R_2 = \frac{R_3}{|G_{Vi2}|} = \frac{20k\Omega}{9.8V/V} = 2.04k\Omega \approx 2.05k\Omega \text{ (Standard Value)}$$

Calculate the small signal circuit bandwidth to ensure it meets the 10-kHz requirement. Be sure to use the noise gain (NG), or non-inverting gain, of the circuit. When calculating the noise gain note that R<sub>1</sub> and R<sub>2</sub> are in parallel.

$$GBP_{OPA170} = 1.2MHz$$

$$\begin{split} NG = & \left(1 + \frac{R_3}{R_1 \| R_2}\right) = \left(1 + \frac{20 k\Omega}{1.86 k\Omega}\right) = 11.75 \frac{V}{V} = 21.4 dB \\ BW = \frac{GBP}{NG} = \frac{1.2 M Hz}{11.75 V/V} = 102 kHz \end{split}$$

This requirement is met because the closed-loop bandwidth is 102kHz and the design goal is 10kHz.

7. Calculate the minmum slew rate to minimize slew-induced distortion.

- $V_{p} = \frac{SR}{2 \times \pi \times f} \rightarrow SR > 2 \times \pi \times f \times V_{p}$ SR > 2 × \pi × 10kHz × 4.9V = 307.87  $\frac{kV}{s} = 0.31 \frac{V}{\mu s}$

- SR<sub>OPA170</sub>=0.4V/µs, therefore it meets this requirement.

- 8. To avoid stability issues ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\begin{split} \frac{1}{2 \times \pi \times (C_{cm} + C_{diff}) \times (R_1 \| R_2 \| R_3)} &> \frac{GBP}{NG} \\ \frac{1}{2 \times \pi \times (3pF + 3pF) \times 1.7 k\Omega} &> \frac{1.2 MHz}{11.75 V/V} \\ 15 \ .6 MHz > 102 kHz \end{split}$$

- $C_{cm}$  and  $C_{diff}$  are the common-mode and differential input capacitances.

- Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

#### **Design Simulations**

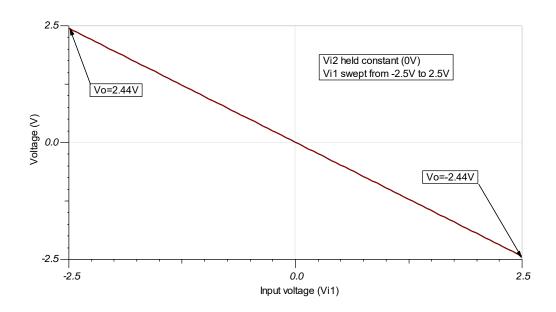

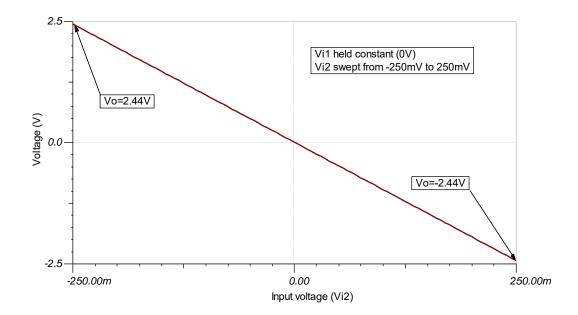

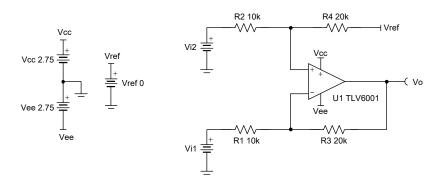

#### **DC Simulation Results**

This simulation sweeps V<sub>i1</sub> from –2.5V to 2.5V while V<sub>i2</sub> is held constant at 0V. The output is inverted and ranges from –2.44V to 2.44V.

This simulation sweeps  $V_{i2}$  from –250mV to 250mV while  $V_{i1}$  is held constant at 0V. The output is inverted and ranges from –2.44V to 2.44V.

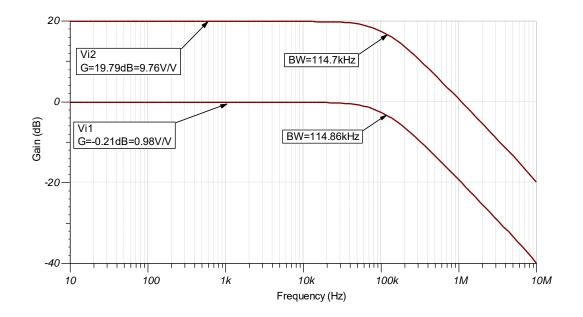

#### **AC Simulation Results**

This simulation shows the bandwidth of the circuit. Note that the bandwidth is the same for either input. This is because the bandwidth depends on the noise gain of the circuit, not the signal gain of each input. These results correlate well with the calculations.

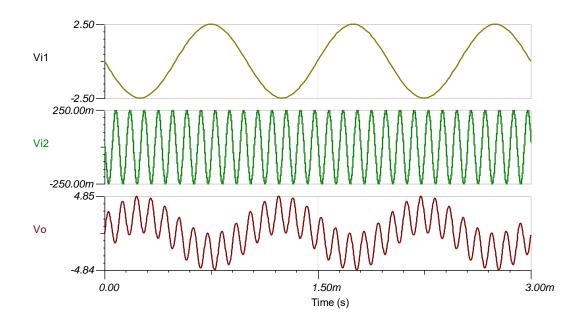

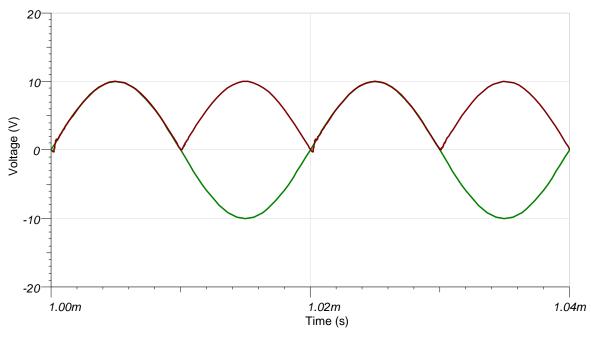

#### **Transient Simulation Results**

This simulation shows the inversion and summing of the two input signals.  $V_{i1}$  is a 1-kHz, 5- $V_{pp}$  sine wave and  $V_{i2}$  is a 10-kHz, 500-m $V_{pp}$  sine wave. Since both inputs are properly amplified or attenuated, the output is within specification.

#### **Design References**

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs.

#### **Design Featured Op Amp**

| OP                        | OPA170                 |  |  |

|---------------------------|------------------------|--|--|

| V <sub>ss</sub>           | 2.7V to 36V            |  |  |

| V <sub>inCM</sub>         | (Vee-0.1V) to (Vcc-2V) |  |  |

| V <sub>out</sub>          | Rail-to-rail           |  |  |

| V <sub>os</sub>           | 0.25mV                 |  |  |

| l <sub>q</sub>            | 110µA                  |  |  |

| l <sub>b</sub>            | 8pA                    |  |  |

| UGBW                      | 1.2MHz                 |  |  |

| SR                        | 0.4V/µs                |  |  |

| #Channels                 | 1, 2, 4                |  |  |

| www.ti.com/product/opa170 |                        |  |  |

## **Design Alternate Op Amp**

| LMC                        | LMC7101       |  |  |

|----------------------------|---------------|--|--|

| V <sub>ss</sub>            | 2.7V to 15.5V |  |  |

| V <sub>inCM</sub>          | Rail-to-rail  |  |  |

| V <sub>out</sub>           | Rail-to-rail  |  |  |

| V <sub>os</sub>            | 110µV         |  |  |

| l <sub>q</sub>             | 0.8mA         |  |  |

| l <sub>b</sub>             | 1pA           |  |  |

| UGBW                       | 1.1MHz        |  |  |

| SR                         | 1.1V/µs       |  |  |

| #Channels                  | 1             |  |  |

| www.ti.com/product/Imc7101 |               |  |  |

# Analog Engineer's Circuit: Op Amps SBOA274–February 2018

# Difference Amplifier (Subtractor) Circuit

#### **Design Goals**

| Input (V <sub>i2</sub> -V <sub>i1</sub> ) |                       | Output            |                   | CMRR (min) |                 | Supply          |                  |

|-------------------------------------------|-----------------------|-------------------|-------------------|------------|-----------------|-----------------|------------------|

| V <sub>idiffMin</sub>                     | V <sub>idiffMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | dB         | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| -1.25V                                    | 1.25V                 | -2.5V             | 2.5V              | 50         | 2.75V           | -2.75V          | 0V               |

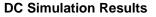

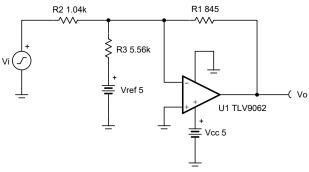

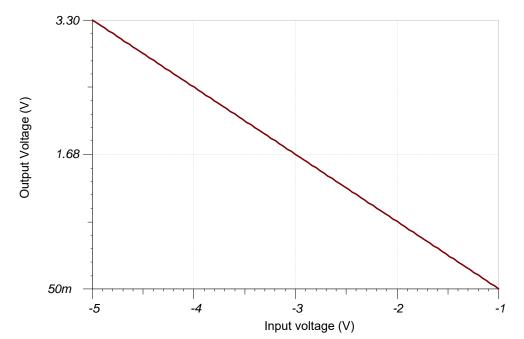

#### **Design Description**

This design inputs two signals,  $V_{i1}$  and  $V_{i2}$ , and outputs their difference (subtracts). The input signals typically come from low-impedance sources because the input impedance of this circuit is determined by the resistive network. Difference amplifiers are typically used to amplify differential input signals and reject common-mode voltages. A common-mode voltage is the voltage common to both inputs. The effectiveness of the ability of a difference amplifier to reject a common-mode signal is known as common-mode rejection ratio (CMRR). The CMRR of a difference amplifier is dominated by the tolerance of the resistors.

Copyright © 2018, Texas Instruments Incorporated

#### **Design Notes**

- Use the op amp in a linear operating region. Ensure that the inputs of the op amp do not exceed the common-mode range of the device. Linear output swing is usually specified under the A<sub>OL</sub> test conditions.

- 2. The input impedance is determined by the input resistive network. Make sure these values are large when compared to the output impedance of the sources.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gainbandwidth product (GBP). Additional filtering can be accomplished by adding a capacitors in parallel to R<sub>3</sub> and R<sub>4</sub>. Adding capacitors in parallel with R<sub>3</sub> and R<sub>4</sub> will also improve stability of the circuit if highvalue resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the *Design References* section.

#### **Design Steps**

The complete transfer function for this circuit is shown below.

$$V_{0} = V_{11} \times \left(-\frac{R_{3}}{R_{1}}\right) + V_{12} \times \left(\frac{R_{4}}{R_{2}+R_{4}}\right) \times \left(1+\frac{R_{3}}{R_{1}}\right) + Vref \times \left(\frac{R_{2}}{R_{2}+R_{4}}\right) \times \left(1+\frac{R_{3}}{R_{1}}\right)$$

If  $R_1 = R_2$  and  $R_3 = R_4$  the transfer function for this circuit simplifies to the following equation.

$$V_0 = (V_{i2} - V_{i1}) \times \frac{R_3}{R_1} + Vref$$

- Where the gain, G, is R<sub>3</sub>/R<sub>1</sub>.

- 1. Determine the starting value of  $R_1$  and  $R_2$ . The relative size of  $R_1$  and  $R_2$  to the signal impedance of the source affects the gain error.

$$R_1 = R_2 = 10k\Omega$$

2. Calculate the gain required for the circuit.

$$G = \frac{V_{oMax} - V_{oMin}}{V_{idiffMax} - V_{idiffMin}} = \frac{2.5V - (-2.5V)}{1.25V - (-1.25V)} = 2\frac{V}{V} = 6.02dB$$

3. Calculate the values for R<sub>3</sub> and R<sub>4</sub>.

$$G = 2\frac{V}{V} = \frac{R_3}{R_1} \rightarrow 2 \times R_1 = R_3 = R_4 = 20 k\Omega$$

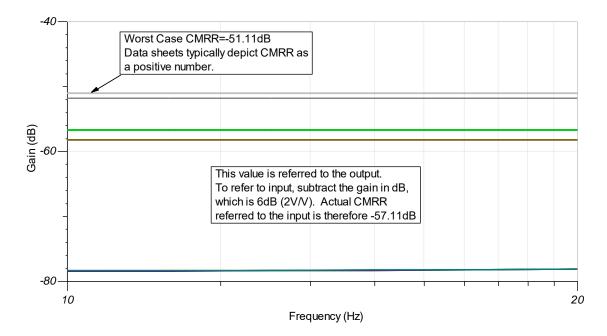

4. Calculate resistor tolerance to meet the minimum common-mode rejection ratio (CMRR). For minimum (worst-case) CMRR,  $\alpha$  = 4. For a more probable, or typical value of CMRR,  $\alpha$  = 0.33.

$$\mathsf{CMRR}_{\mathsf{dB}} \cong 20 \log 10 \left( \frac{1+\mathsf{G}}{\alpha \times \varepsilon} \right)$$

$$\epsilon = \frac{1+G}{\alpha \times 10^{\left(\frac{CMRR_{dB}}{20}\right)}} = \frac{3}{4 \times 10^{\left(\frac{50}{20}\right)}} = 0.024 = 0.24\% \rightarrow \text{Use} \quad 0.1 \ \% \text{ resistors}$$

5. For quick reference, the following table compares resistor tolerance to minimum and typical CMRR values assuming G = 1 or G = 2. As shown above, as gain increases so does CMRR.

| Tolerance    | G=1 Minimum (dB) | G=1 Typical (dB) | G=2 Minimum (dB) | G=2 Typical (dB) |

|--------------|------------------|------------------|------------------|------------------|

| 0.01%=0.0001 | 74               | 95.6             | 77.5             | 99.2             |

| 0.1%=0.001   | 54               | 75.6             | 57.5             | 79.2             |

| 0.5%=0.005   | 40               | 61.6             | 43.5             | 65.2             |

| 1%=0.01      | 34               | 55.6             | 37.5             | 59.2             |

| 5%=0.05      | 20               | 41.6             | 23.5             | 45.2             |

TEXAS INSTRUMENTS

www.ti.com

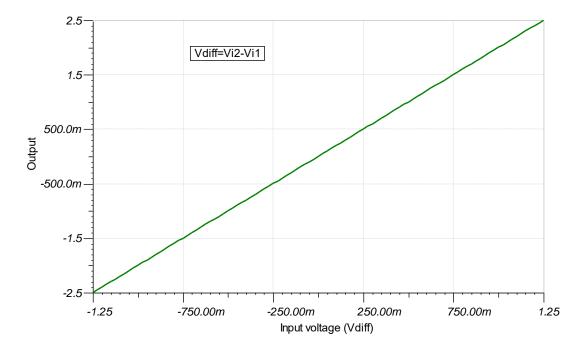

**Design Simulations**

## **CMRR Simulation Results**

#### **Design References**

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs. For more information on difference amplifier CMRR, please read *Overlooking the obvious: the input impedance of a difference amplifier*.

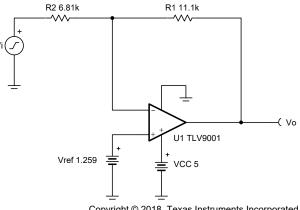

#### **Design Featured Op Amp**

| TLV6001                    |              |  |

|----------------------------|--------------|--|

| V <sub>ss</sub>            | 1.8V to 5.5V |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |

| V <sub>out</sub>           | Rail-to-rail |  |

| V <sub>os</sub>            | 750µV        |  |

| l <sub>q</sub>             | 75μΑ         |  |

| I <sub>b</sub>             | 1pA          |  |

| UGBW                       | 1MHz         |  |

| SR                         | 0.5V/µs      |  |

| #Channels                  | 1, 2, 4      |  |

| www.ti.com/product/tlv6001 |              |  |

#### **Design Alternate Op Amp**

| OPA320                    |              |  |

|---------------------------|--------------|--|

| V <sub>ss</sub>           | 1.8V to 5.5V |  |

| V <sub>inCM</sub>         | Rail-to-rail |  |

| V <sub>out</sub>          | Rail-to-rail |  |

| V <sub>os</sub>           | 40µV         |  |

| l <sub>q</sub>            | 1.5mA        |  |

| I <sub>b</sub>            | 0.2pA        |  |

| UGBW                      | 20MHz        |  |

| SR                        | 10V/µs       |  |

| #Channels                 | 1, 2         |  |

| www.ti.com/product/opa320 |              |  |

Analog Engineer's Circuit: Op Amps SBOA275-February 2018

# Integrator Circuit

#### **Design Goals**

| Input            |                  | Output           |                   | Supply            |                 |                 |

|------------------|------------------|------------------|-------------------|-------------------|-----------------|-----------------|

| f <sub>Min</sub> | f <sub>0dB</sub> | f <sub>Max</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> |

| 100Hz            | 1kHz             | 100kHz           | -2.45V            | 2.45V             | 2.5V            | -2.5V           |

#### **Design Description**

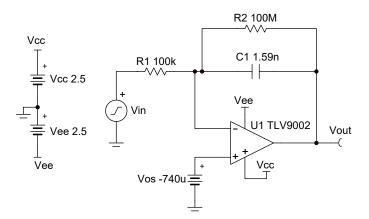

The integrator circuit outputs the integral of the input signal over a frequency range based on the circuit time constant and the bandwidth of the amplifier. The input signal is applied to the inverting input so the output is inverted relative to the polarity of the input signal. The ideal integrator circuit will saturate to the supply rails depending on the polarity of the input offset voltage and requires the addition of a feedback resistor,  $R_2$ , to provide a stable DC operating point. The feedback resistor limits the lower frequency range over which the integration function is performed. This circuit is most commonly used as part of a larger feedback/servo loop which provides the DC feedback path, thus removing the requirement for a feedback resistor.

Copyright © 2018, Texas Instruments Incorporated

#### **Design Notes**

- 1. Use as large of a value as practical for the feedback resistor.

- 2. Select a CMOS op amp to minimize the errors from the input bias current.

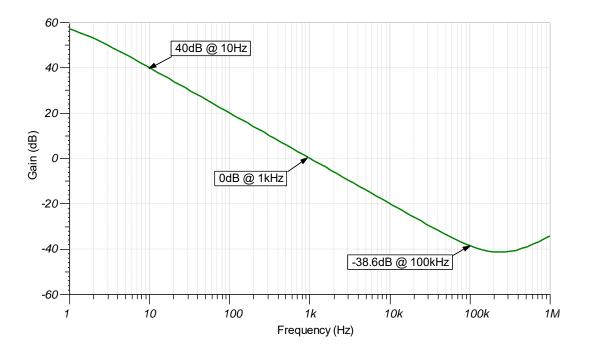

- 3. The gain bandwidth product (GBP) of the amplifier will set the upper frequency range of the integrator function. The effectiveness of the integration function is usually reduced starting about one decade away from the amplifier bandwidth.

- 4. An adjustable reference needs to be connected to the non-inverting input of the op amp to cancel the input offset voltage or the large DC noise gain will cause the circuit to saturate. Op amps with very low offset voltage may not require this.

#### **Design Steps**

The ideal circuit transfer function is given below.

$$V_{out} = -\frac{1}{R_1 \cdot C_1} \int_0^t V_{in}(t) dt$$

1. Set  $R_1$  to a standard value.

$$R_1 = 100 k\Omega$$

2. Calculate  $C_{1}$  to set the unity-gain integration frequency.

$$C_1 = \frac{1}{2 \times \pi \times R_1 \times f_{0dB}} = \frac{1}{2 \times \pi \times 100 k\Omega \times 1 \text{ kHz}} = 1.59 \text{nF}$$

3. Calculate  $R_2$  to set the lower cutoff frequency a decade less than the minimum operating frequency.

$$R_2 \ge \frac{10}{2 \times \pi \times C_1 \times f_{Min}} \ge \frac{10}{2 \times \pi \times 1.59 n F \times 10 Hz} \ge 100 M\Omega$$

4. Select an amplifier with a gain bandwidth at least 10 times the desired maximum operating frequency. GBP  $\ge 10 \times f_{Max} \ge 10 \times 100$ kHz  $\ge 1$  MHz

#### **Design Simulations**

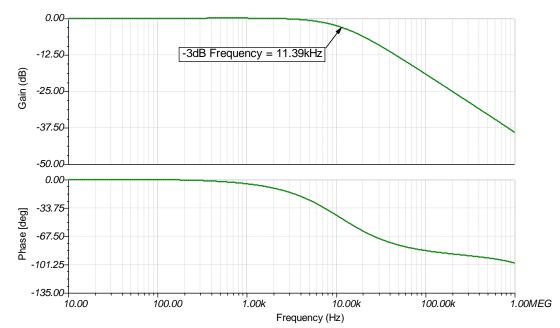

#### AC Simulation Results

#### **Transient Simulation Results**

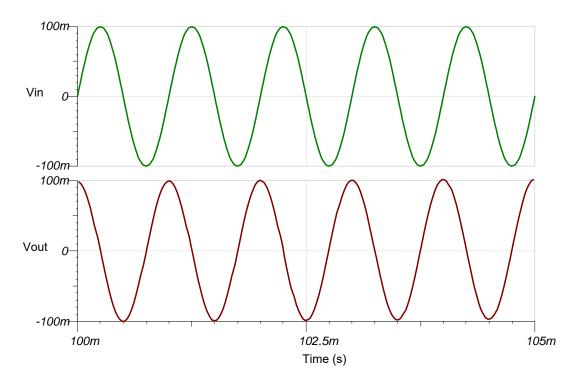

A 1-kHz sine wave input yields a 1-kHz cosine output.

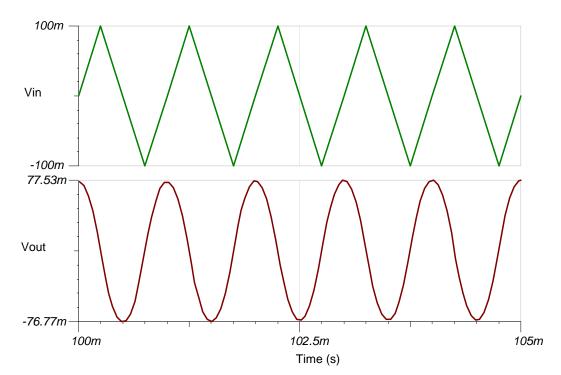

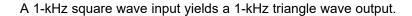

### A 1-kHz triangle wave input yields a 1-kHz sine wave output.

#### **Design References**

See TIPD191, www.ti.com/tool/tipd191.

## **Design Featured Op Amp**

| TLV9002           |                |  |

|-------------------|----------------|--|

| V <sub>cc</sub>   | 1.8V to 5.5V   |  |

| V <sub>inCM</sub> | Rail-to-rail   |  |

| V <sub>out</sub>  | Rail-to-rail   |  |

| V <sub>os</sub>   | 0.4mV          |  |

| l <sub>q</sub>    | 0.06mA         |  |

| I <sub>b</sub>    | 5pA            |  |

| UGBW              | 1MHz           |  |

| SR                | 2V/µs          |  |

| #Channels         | 1, 2, 4        |  |

| www.ti.com/pi     | roduct/tlv9002 |  |

# Design Alternate Op Amp

| OPA376                    |                                                    |  |

|---------------------------|----------------------------------------------------|--|

| V <sub>cc</sub>           | 2.2V to 5.5V                                       |  |

| V <sub>inCM</sub>         | (V <sub>ee</sub> -0.1V) to (V <sub>cc</sub> -1.3V) |  |

| V <sub>out</sub>          | Rail-to-rail                                       |  |

| V <sub>os</sub>           | 0.005mV                                            |  |

| l <sub>q</sub>            | 0.76mA                                             |  |

| l <sub>b</sub>            | 0.2pA                                              |  |

| UGBW                      | 5.5MHz                                             |  |

| SR                        | 2V/µs                                              |  |

| #Channels                 | 1, 2, 4                                            |  |

| www.ti.com/product/opa376 |                                                    |  |

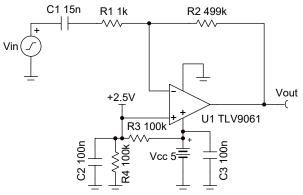

# **Differentiator Circuit**

#### **Design Goals**

| Ing              | out              | Output            |                   | Supply          |                 |                  |

|------------------|------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| f <sub>Min</sub> | f <sub>Max</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| 100Hz            | 5kHz             | 0.1V              | 4.9V              | 5V              | 0V              | 2.5V             |

#### **Design Description**

The differentiator circuit outputs the derivative of the input signal over a frequency range based on the circuit time constant and the bandwidth of the amplifier. The input signal is applied to the inverting input so the output is inverted relative to the polarity of the input signal. The ideal differentiator circuit is fundamentally unstable and requires the addition of an input resistor, a feedback capacitor, or both, to be stable. The components required for stability limit the bandwidth over which the differentiator function is performed.

#### Copyright © 2018, Texas Instruments Incorporated

#### **Design Notes**

- 1. Select a large resistance for  $R_2$  to keep the value of  $C_1$  reasonable.

- 2. A capacitor can be added in parallel with R<sub>2</sub> to filter the high-frequency noise of the circuit. The capacitor will limit the effectiveness of the differentiator function starting about half a decade (approximately 3.5 times) away from the filter cutoff frequency.

- 3. A reference voltage can be applied to the non-inverting input to set the DC output voltage which allows the circuit to work single-supply. The reference voltage can be derived from a voltage divider.

- 4. Operate within the linear output voltage swing (see Aol specification) to minimize non-linearity errors.

#### **Design Steps**

The ideal circuit transfer function is given below.

Vout =

$$-R_2 \times C_1 \times \frac{dV_{in}(t)}{dt}$$

- 1. Set  $R_2$  to a large standard value.  $R_2 = 499 k\Omega$

- 2. Set the minimum differentiation frequency at least half a decade below the minimum operating frequency.

$$C_1 \ge \frac{3.5}{2 \times \pi \times R_2 \times f_{min}} \ge \frac{3.5}{2 \times \pi \times 499 k\Omega \times 100 Hz} \ge 11.1 \text{ nF} \approx 15 \text{nF} \text{ (Standard Value)}$$

3. Set the upper cutoff frequency at least half a decade above the maximum operating frequency.

$$R_1 \leq \frac{1}{3.5 \times 2 \times \pi \times C_1 \times f_{Max}} \leq \frac{1}{7 \times \pi \times 15 nF \times 2.5 kHz} \leq 1.2 k\Omega \approx 1 \ k\Omega \quad (Standard \ Value)$$

4. Calculate the necessary op amp gain bandwidth product (GBP) for the circuit to be stable.

$$GBP \! > \! \frac{R_{1} \! + \! R_{2}}{2 \! \times \! \pi \! \times \! R_{1}^{2} \! \times \! C_{1}} \! > \! \frac{499 \! k \Omega \! + \! 1 \, k \Omega}{2 \! \times \! \pi \! \times \! 1 \, k \Omega^{2} \! \times \! 15 n F} \! > \! 5 \, . \, 3MHz$$

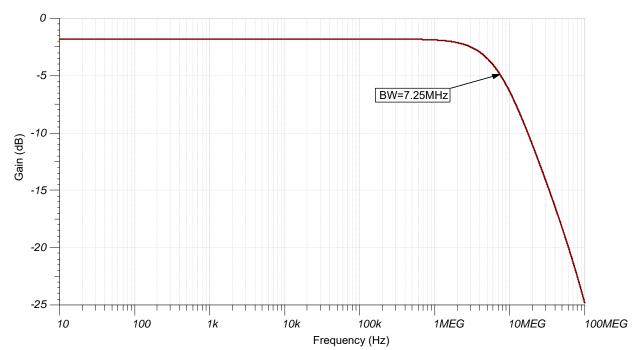

- The bandwidth of the TLV9061 is 10MHz, therefore this requirement is met.

- 5. If a feedback capacitor,  $C_F$ , is added in parallel with  $R_2$ , the equation to calculate the cutoff frequency follows.

$$f_{C} = \frac{1}{2 \times \pi \times R_{2} \times C_{F}}$$

6. Calculate the resistor divider values for a 2.5-V reference voltage.

$$R_{3} = \frac{V_{cc} - V_{ref}}{V_{ref}} \times R_{4} = \frac{5V - 2.5V}{2.5V} \times R_{4} = R_{4}$$

$$R_{3} = R_{4} = 100 k\Omega \quad (Standard \quad Values)$$

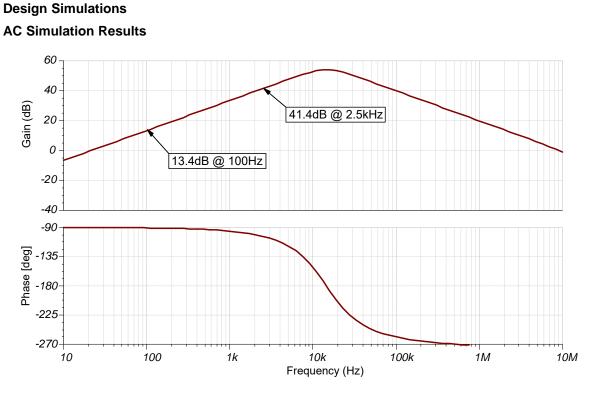

TEXAS INSTRUMENTS

www.ti.com

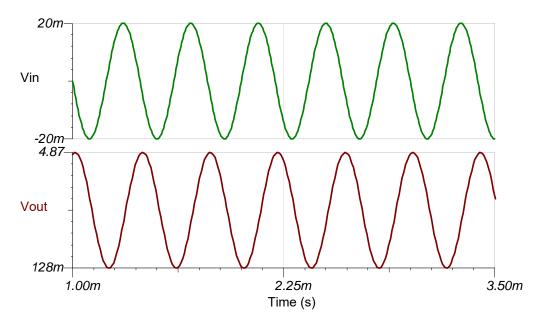

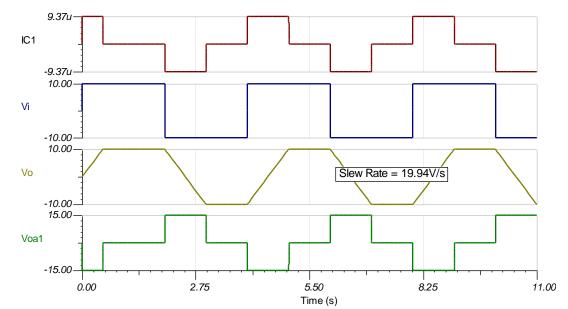

#### **Transient Simulation Results**

A 2.5-kHz sine wave input yields a 2.5-kHz cosine output.

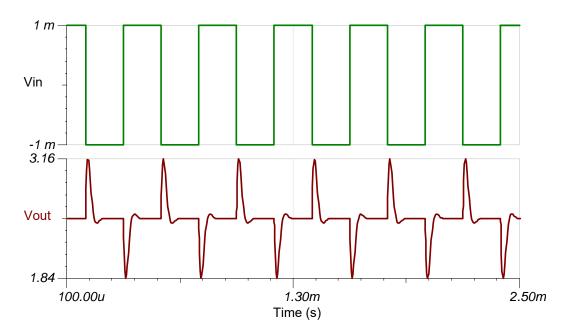

A 2.5-kHz square wave input produces an impulse output.

## A 100-Hz triangle wave input yields a square wave output.

## **Design Featured Op Amp**

| TLV9061                    |              |  |  |

|----------------------------|--------------|--|--|

| V <sub>cc</sub>            | 1.8V to 5.5V |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |

| V <sub>os</sub>            | 0.3mV        |  |  |

| l <sub>q</sub>             | 0.538mA      |  |  |

| I <sub>b</sub>             | 0.5pA        |  |  |

| UGBW                       | 10MHz        |  |  |

| SR                         | 6.5V/µs      |  |  |

| #Channels                  | 1, 2, 4      |  |  |

| www.ti.com/product/tlv9061 |              |  |  |

# Design Alternate Op Amp

| OPA374                    |              |  |

|---------------------------|--------------|--|

| V <sub>cc</sub>           | 2.3V to 5V   |  |

| V <sub>inCM</sub>         | Rail-to-rail |  |

| V <sub>out</sub>          | Rail-to-rail |  |

| V <sub>os</sub>           | 1mV          |  |

| Ι <sub>q</sub>            | 0.585mA      |  |

| I <sub>b</sub>            | 0.5pA        |  |

| UGBW                      | 6.5MHz       |  |

| SR                        | 0.4V/µs      |  |

| #Channels                 | 1, 2, 4      |  |

| www.ti.com/product/opa374 |              |  |

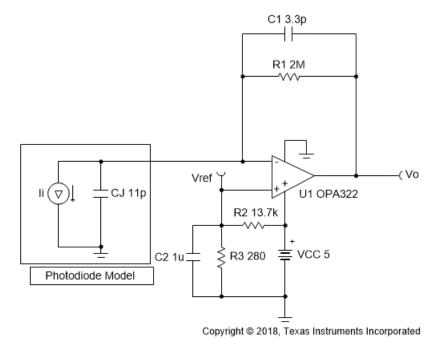

# Analog Engineer's Circuit: Op Amps SBOA268–February 2018

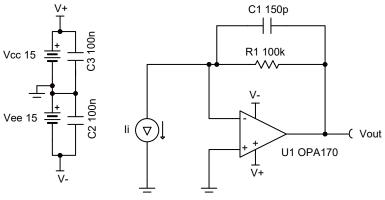

# Transimpedance Amplifier Circuit

#### **Design Goals**

| Input             |                   | Output            |                   | BW             | Supply          |                 |

|-------------------|-------------------|-------------------|-------------------|----------------|-----------------|-----------------|

| l <sub>iMin</sub> | I <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f <sub>p</sub> | V <sub>cc</sub> | V <sub>ee</sub> |

| 0A                | 50µA              | 0V                | 5V                | 10kHz          | 15V             | –15V            |

#### **Design Description**

The transimpedance op amp circuit configuration converts an input current source into an output voltage. The current to voltage gain is based on the feedback resistance. The circuit is able to maintain a constant voltage bias across the input source as the input current changes which benefits many sensors.

Copyright © 2018, Texas Instruments Incorporated

- 1. Use a JFET or CMOS input op amp with low bias current to reduce DC errors.

- 2. A bias voltage can be added to the non-inverting input to set the output voltage for 0-A input currents.

- 3. Operate within the linear output voltage swing (see A<sub>ol</sub> specification) to minimize non-linearity errors.

#### **Design Steps**

1. Select the gain resistor.

$$R_{1} = \frac{V_{oMax} - V_{oMin}}{I_{iMax}} = \frac{5V - 0V}{50\mu A} = 100 k\Omega$$

2. Select the feedback capacitor to meet the circuit bandwidth.

$$\begin{split} &C_1 \leq \frac{1}{2 \times \pi \times R_1 \times f_p} \\ &C_1 \leq \frac{1}{2 \times \pi \times 100 k\Omega \times 10 kHz} \leq 159 pF \approx 150 pF \text{ (Standard Value)} \end{split}$$

3. Calculate the necessary op amp gain bandwidth (GBW) for the circuit to be stable.

$$GBW \! > \! \frac{C_i \! + \! C_1}{2 \! \times \! \pi \! \times \! R_1 \! \times \! C_1^2} \! > \! \frac{6 \! p F \! + \! 150 \! p F}{2 \! \times \! \pi \! \times \! 100 \! k \Omega \! \times \! (150 \! p F)^2} \! > \! 11.03 \text{kHz}$$

where  $C_i\!=\!C_s\!+\!C_d\!+\!C_{cm}\!=\!0pF\!+\!3pF\!+\!3pF\!=\!6pF$  given

- C<sub>s</sub>: Input source capacitance

- C<sub>d</sub>: Differential input capacitance of the amplifier

- $C_{cm}$ : Common-mode input capacitance of the inverting input

TEXAS INSTRUMENTS

www.ti.com

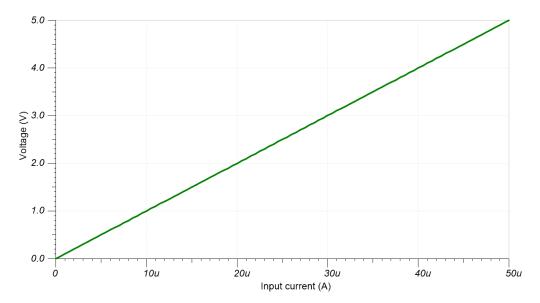

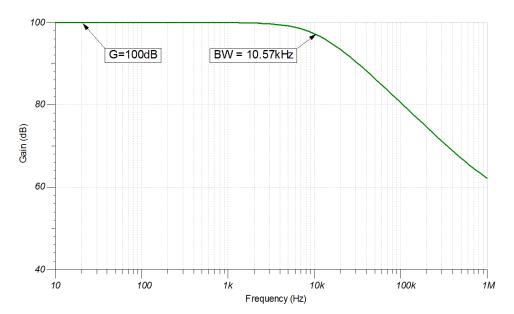

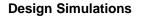

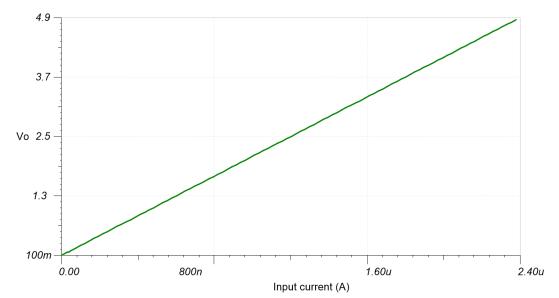

### **Design Simulations**

### **AC Simulation Results**

#### **Design References**

See TIPD176, www.ti.com/tool/tipd176.

# **Design Featured Op Amp**

| OPA170                    |                                    |  |  |

|---------------------------|------------------------------------|--|--|

| V <sub>cc</sub>           | 2.7V to 36V                        |  |  |

| V <sub>inCM</sub>         | $(V_{ee}$ –0.1V) to $(V_{cc}$ –2V) |  |  |

| V <sub>out</sub>          | Rail-to-rail                       |  |  |

| V <sub>os</sub>           | 0.25mV                             |  |  |

| l <sub>q</sub>            | 0.11mA                             |  |  |

| l <sub>b</sub>            | 8pA                                |  |  |

| UGBW                      | 1.2MHz                             |  |  |

| SR                        | 0.4V/µs                            |  |  |

| #Channels                 | 1, 2, 4                            |  |  |

| www.ti.com/product/opa170 |                                    |  |  |

# Design Alternate Op Amp

| OPA145                    |                                                    |  |  |

|---------------------------|----------------------------------------------------|--|--|

| V <sub>cc</sub>           | 4.5V to 36V                                        |  |  |

| V <sub>inCM</sub>         | (V <sub>ee</sub> –0.1V) to (V <sub>cc</sub> –3.5V) |  |  |

| V <sub>out</sub>          | Rail–to–rail                                       |  |  |

| V <sub>os</sub>           | 40µV                                               |  |  |

| l <sub>q</sub>            | 0.445mA                                            |  |  |

| I <sub>b</sub>            | 2pA                                                |  |  |

| UGBW                      | 5.5MHz                                             |  |  |

| SR                        | 20V/µs                                             |  |  |

| #Channels                 | 1, 2, 4                                            |  |  |

| www.ti.com/product/opa145 |                                                    |  |  |

Analog Engineer's Circuit: Op Amps SBOA215-February 2018

# Single-Supply, Low-Side, Unidirectional Current-Sensing Solution with Output Swing to GND Circuit

#### **Design Goals**

| Inj               | out               | Output            |                   | Supply          |                 |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| l <sub>iMin</sub> | l <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| 0A                | 1A                | 0V                | 4.9V              | 5V              | 0V              | 0V               |

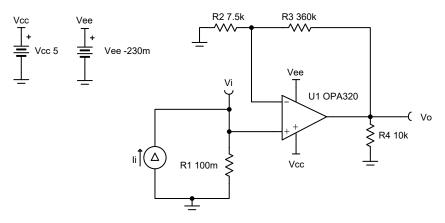

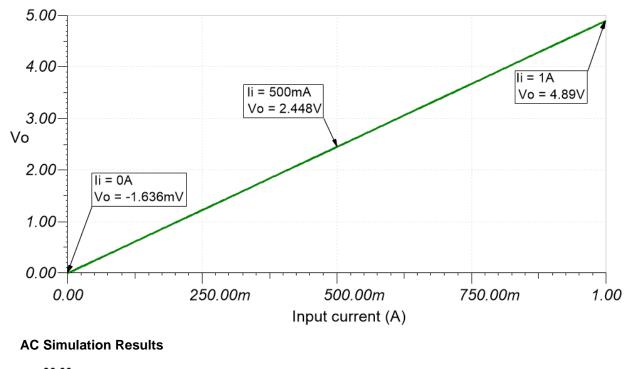

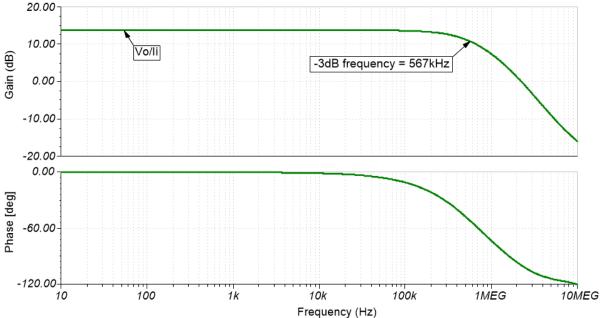

#### **Design Description**

This single-supply, low-side, current sensing solution accurately detects load current between 0A to 1A and converts it to a voltage between 0V to 4.9V. The input current range and output voltage range can be scaled as necessary and larger supplies can be used to accommodate larger swings. A negative charge pump (such as the LM7705) is used as the negative supply in this design to maintain linearity for output signals near 0V.

Copyright © 2018, Texas Instruments Incorporated

- 1. Use precision resistors to minimize gain error.

- 2. For light load accuracy, the negative supply should extend slightly below ground.

- 3. A capacitor placed in parallel with the feedback resistor will limit bandwidth and help reduce noise.

#### **Design Steps**

1. Determine the transfer function.

$$V_0 = I_j \times R_1 \times \left(1 + \frac{R_3}{R_2}\right)$$

2. Define the full-scale shunt voltage and shunt resistance.

3. Select gain resistors to set the output range.  $V_{iMax} = 100 \text{mV}$  and  $V_{oMax} = 4.9 \text{V}$

$$V_{iMax} = 100 \text{ for and } V_{oMax} = 2$$

$$Gain = \frac{V_{oMax}}{V_{iMax}} = \frac{4.9V}{100 \text{ mV}} = 49\frac{V}{V}$$

$$Gain = 1 + \frac{R_3}{R_2} = 49\frac{V}{V}$$

4. Select a standard value for  $R_2$  and  $R_3$ .

$R_2\!=\!7.5\!\mathrm{k}\Omega$  (0.05% Standard Value)

$$R_3 = 48 \times R_2 = 360 k\Omega (0.05\% \text{ Standard Value})$$

Texas

### Design Simulations

TRUMENTS

#### **Design References**

See TIPD129, www.ti.com/tool/tipd129.

#### **Design Featured Op Amp**

| OPA320            |                           |  |  |

|-------------------|---------------------------|--|--|

| V <sub>cc</sub>   | 1.8V to 5.5V              |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |

| V <sub>os</sub>   | 40µV                      |  |  |

| l <sub>q</sub>    | 1.5mA/Ch                  |  |  |

| l <sub>b</sub>    | 0.2pA                     |  |  |

| UGBW              | 10MHz                     |  |  |

| SR                | 10V/µs                    |  |  |

| #Channels         | 1, 2                      |  |  |

| www.ti.com/p      | www.ti.com/product/opa320 |  |  |

#### **Design Alternate Op Amp**

| TLV9002                    |              |  |  |

|----------------------------|--------------|--|--|

| V <sub>cc</sub>            | 1.8V to 5.5V |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |

| V <sub>os</sub>            | 400µV        |  |  |

| l <sub>q</sub>             | 60µA         |  |  |

| I <sub>b</sub>             | 5pA          |  |  |

| UGBW                       | 1MHz         |  |  |

| SR                         | 2V/µs        |  |  |

| #Channels                  | 1, 2, 4      |  |  |

| www.ti.com/product/tlv9002 |              |  |  |

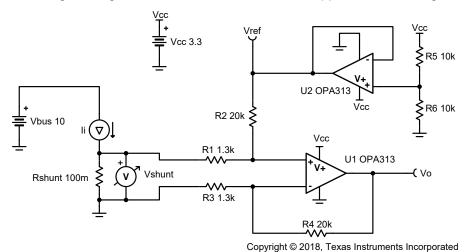

# Low-Side, Bidirectional Current Sensing Circuit

#### **Design Goals**

| Ing               | Input             |                   | Output            |                 | Supply          |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| l <sub>iMin</sub> | I <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| -1A               | 1A                | 110mV             | 3.19V             | 3.3V            | 0V              | 1.65V            |

#### **Design Description**

This single-supply low-side, bidirectional current sensing solution can accurately detect load currents from –1A to 1A. The linear range of the output is from 110mV to 3.19V. Low-side current sensing keeps the common-mode voltage near ground, and is thus most useful in applications with large bus voltages.

- 1. To minimize errors, set  $R_3 = R_1$  and  $R_4 = R_2$ .

- 2. Use precision resistors for higher accuracy.

- 3. Set output range based on linear output swing (see A<sub>ol</sub> specification).

- 4. Low-side sensing should not be used in applications where the system load cannot withstand small ground disturbances or in applications that need to detect load shorts.

#### **Design Steps**

1. Determine the transfer equation given  $R_4 = R_2$  and  $R_1 = R_3$ .

$$V_{o} = \left(I_{i} \times R_{shunt} \times \frac{R_{4}}{R_{3}}\right) + V_{ref}$$

$$V_{ref} = V_{cc} \times \left(\frac{R_{6}}{R_{5} + R_{6}}\right)$$

2. Determine the maximum shunt resistance.

$$R_{shunt} = \frac{V_{shunt}}{I_{imax}} = \frac{100mV}{1A} = 100m\Omega$$

- 3. Set reference voltage.

- a. Since the input current range is symmetric, the reference should be set to mid supply. Therefore, make  $R_5$  and  $R_6$  equal.  $R_5 = R_6 = 10k\Omega$

- 4. Set the difference amplifier gain based on the op amp output swing. The op amp output can swing from 100mV to 3.2V, given a 3.3-V supply.

$$\begin{split} & \text{Gain} = \frac{V_{\text{oMax}} - V_{\text{oMin}}}{R_{\text{shunt}} \times (I_{\text{iMax}} - I_{\text{iMin}})} = \frac{3.2 \,\text{V} - 100 \text{mV}}{100 \text{m}\Omega \times (1 \text{ A} - (-1 \text{ A}))} = 15 \text{ .5 } \frac{\text{V}}{\text{V}} \\ & \text{Gain} = \frac{R_4}{R_3} = 15 \text{ .5 } \frac{\text{V}}{\text{V}} \\ & \text{Choose } R_1 = R_3 = 1.3 \text{k}\Omega \text{ (Standard Value)} \\ & R_2 = R_4 = 15 \text{ .5 } \frac{\text{V}}{\text{V}} \times 1.3 \text{k}\Omega = 20 \text{ .15 } \text{k}\Omega \approx 20 \text{k}\Omega \text{ (Standard Value)} \end{split}$$

TEXAS INSTRUMENTS

www.ti.com

### **Design Simulations**

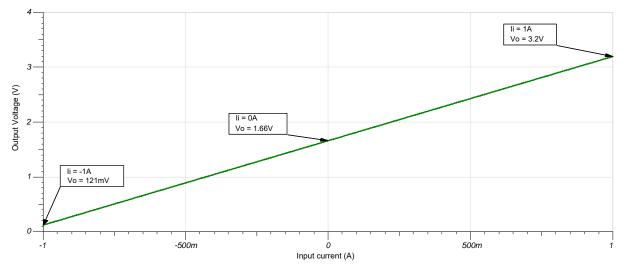

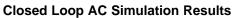

**DC Simulation Results**

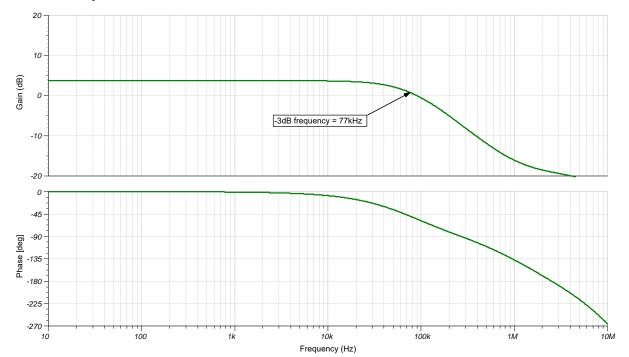

#### **Transient Simulation Results**

## Design References

See TIPD175, www.ti.com/tipd175.

#### **Design Featured Op Amp**

| OP                | OPA313                    |  |  |  |

|-------------------|---------------------------|--|--|--|

| V <sub>cc</sub>   | 1.8V to 5.5V              |  |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |  |

| V <sub>os</sub>   | 500µV                     |  |  |  |

| l <sub>q</sub>    | 50µA/Ch                   |  |  |  |

| I <sub>b</sub>    | 0.2pA                     |  |  |  |

| UGBW              | 1MHz                      |  |  |  |

| SR                | 0.5V/µs                   |  |  |  |

| #Channels         | 1, 2, 4                   |  |  |  |

| www.ti.com/p      | www.ti.com/product/opa313 |  |  |  |

#### **Design Alternate Op Amp**

| TLV9062           |                            |  |  |

|-------------------|----------------------------|--|--|

| V <sub>cc</sub>   | 1.8V to 5.5V               |  |  |

| V <sub>inCM</sub> | Rail-to-rail               |  |  |

| V <sub>out</sub>  | Rail-to-rail               |  |  |

| V <sub>os</sub>   | 300µV                      |  |  |

| l <sub>q</sub>    | 538µA/Ch                   |  |  |

| I <sub>b</sub>    | 0.5pA                      |  |  |

| UGBW              | 10MHz                      |  |  |

| SR                | 6.5V/µs                    |  |  |

| #Channels         | 1, 2, 4                    |  |  |

| www.ti.com/p      | www.ti.com/product/tlv9062 |  |  |

# **Design Alternate Op Amp**

| OPA376            |                           |  |  |

|-------------------|---------------------------|--|--|

| V <sub>cc</sub>   | 2.2V to 5.5V              |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |

| V <sub>os</sub>   | 5µV                       |  |  |

| l <sub>q</sub>    | 760µA/Ch                  |  |  |

| l <sub>b</sub>    | 0.2pA                     |  |  |

| UGBW              | 5.5MHz                    |  |  |

| SR                | 2V/µs                     |  |  |

| #Channels         | 1, 2, 4                   |  |  |

| www.ti.com/p      | www.ti.com/product/opa376 |  |  |

# Analog Engineer's Circuit: Op Amps SBOA210–January 2018

# 3-Decade, Load-Current Sensing Circuit

#### **Design Goals**

| Input             |                   | Output            |                   | Supply          |                 |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| l <sub>iMin</sub> | l <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| 10µA              | 10mA              | 100mV             | 4.9V              | 5.0V            | 0V              | 0V               |

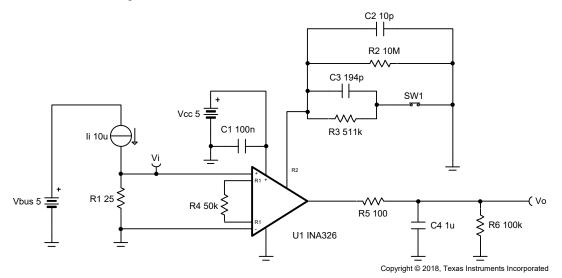

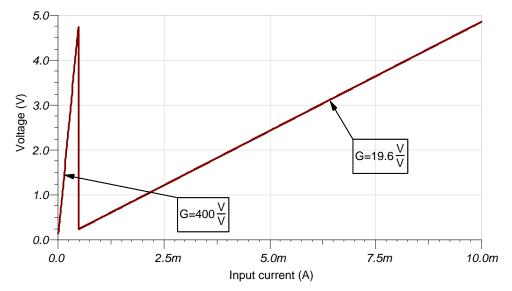

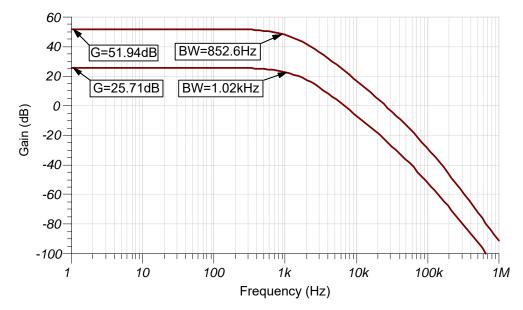

#### **Design Description**

This single-supply, low-side, current-sensing solution accurately detects load current between  $10\mu$ A and 10mA. A unique yet simple gain switching network was implemented to accurately measure the three-decade load current range.

- 1. Use a maximum shunt resistance to minimize relative error at minimum load current.

- 2. Select 0.1% tolerance resistors for R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, and R<sub>4</sub> in order to achieve approximately 0.1% FSR gain error.

- 3. Use a switch with low on-resistance (R<sub>on</sub>) to minimize interaction with feedback resistances, preserving gain accuracy.

- 4. Minimize capacitance on INA326 gain setting pins.

- 5. Scale the linear output swing based on the gain error specification.

### **Design Steps**

1. Define full-scale shunt resistance.

$$R_1 = \frac{V_{iMax}}{I_{iMax}} = \frac{250 \text{mV}}{10 \text{mA}} = 25\Omega$$

2. Select gain resistors to set output range.

$$\begin{split} G_{IiMax} &= \frac{V_{oMax}}{V_{iMax}} = \frac{V_{oMax}}{R_1 \times I_{iMax}} = \frac{4.9V}{25\Omega \times 10mA} = 19.6\frac{V}{V} \\ G_{IiMin} &= \frac{V_{oMin}}{V_{iMin}} = \frac{V_{oMin}}{R_1 \times I_{iMin}} = \frac{100mV}{25\Omega \times 10\mu A} = 400\frac{V}{V} \\ R_2 &= \frac{R_4 \times G_{IiMin}}{2} = \frac{50k\Omega \times 400\frac{V}{V}}{2} = 10M\Omega \\ R_2 ||R_3 &= \frac{R_4 \times G_{IiMax}}{2} = \frac{50k\Omega \times 19.6\frac{V}{V}}{2} = 490k\Omega \\ R_3 &= \frac{490k\Omega \times R_2}{R_2 - 490k\Omega} = 515.25k\Omega \approx 511k\Omega \text{ (Standard Value)} \end{split}$$

3. Select a capacitor for the output filter.

$$f_p = \frac{1}{2 \times \pi \times R_5 \times C_4} = \frac{1}{2 \times \pi \times 100 \Omega \times 1 \mu F} = 1.59 \text{kHz}$$

4. Select a capacitor for gain and filtering network.

$$\begin{split} C_2 &= \frac{1}{2 \times \pi \times R_2 \times f_p} = \frac{1}{2 \times \pi \times 10 M\Omega \times 1.59 \text{kHz}} = 10 \text{pF} \\ C_3 &= \frac{1}{2 \times \pi \times (R_2 \| R_3) \times f_p} - C_2 = \frac{1}{2 \times \pi \times (10 M\Omega \| 511 \text{k}\Omega) \times 1.59 \text{kHz}} - 10 \text{pF} \end{split}$$

$C_3 = 196 pF \approx 194 pF$  (Standard Value)

TEXAS INSTRUMENTS

www.ti.com

# **Design Simulations**

**DC Simulation Results**

#### **Design References**

See TIPD104, www.ti.com/tool/tipd104.

## **Design Featured Op Amp**

| INA               | INA326                    |  |  |  |

|-------------------|---------------------------|--|--|--|

| V <sub>ss</sub>   | 1.8V to 5.5V              |  |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |  |

| V <sub>os</sub>   | 0.1mV                     |  |  |  |

| l <sub>q</sub>    | 3.4mA                     |  |  |  |

| I <sub>b</sub>    | 2nA                       |  |  |  |

| UGBW              | 1kHz                      |  |  |  |

| SR                | Filter limited            |  |  |  |

| #Channels         | 1                         |  |  |  |

| www.ti.com/p      | www.ti.com/product/ina326 |  |  |  |

Analog Engineer's Circuit: Op Amps SBOA212–January 2018

# **PWM Generator Circuit**

#### **Design Goals**

| Input             |                   | Output            |                   | Supply          |                 |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| -2.0V             | 2.0V              | 0V                | 5V                | 5V              | 0V              | 2.5V             |

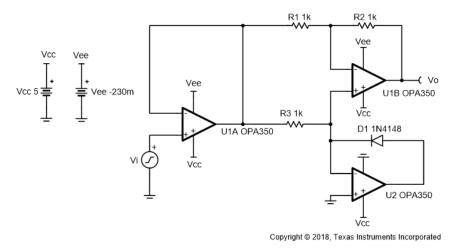

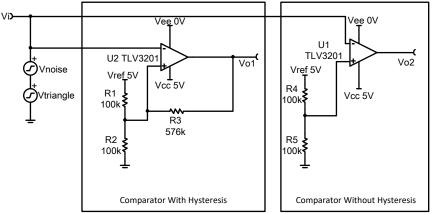

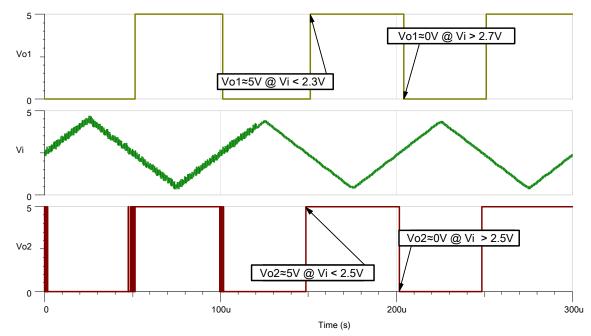

#### **Design Description**

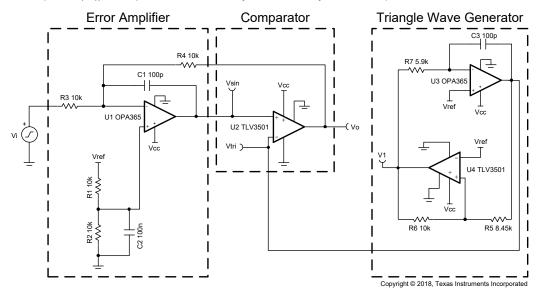

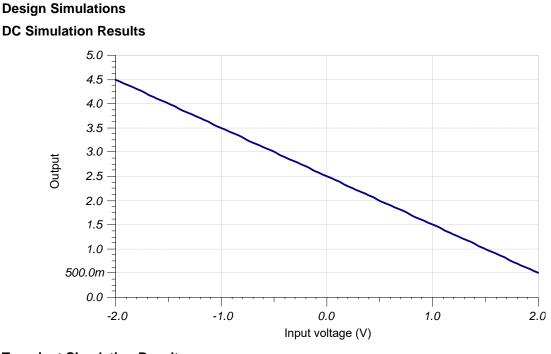

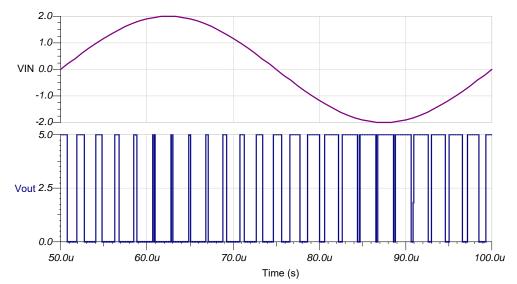

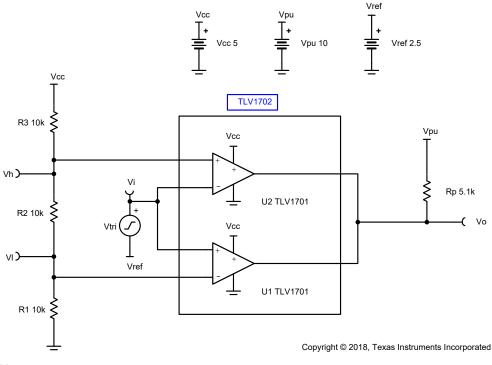

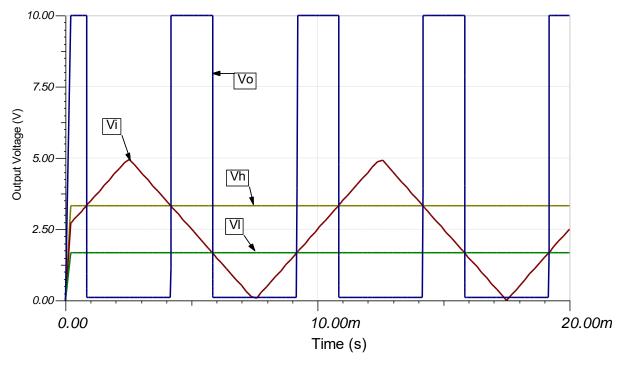

This circuit utilizes a triangle wave generator and comparator to generate a 500 kHz pulse-widthmodulated (PWM) waveform with a duty cycle that is inversely proportional to the input voltage. An op amp and comparator ( $U_3$  and  $U_4$ ) generate a triangle waveform which is applied to the inverting input of a second comparator ( $U_2$ ). The input voltage is applied to the non-inverting input of  $U_2$ . By comparing the input waveform to the triangle wave, a PWM waveform is produced.  $U_2$  is placed in the feedback loop of an error amplifier ( $U_1$ ) to improve the accuracy and linearity of the output waveform.

- 1. Use a comparator with push-pull output and minimal propagation delay.

- 2. Use an op amp with sufficient slew rate, GBW, and voltage output swing.

- 3. Place the pole created by  $C_1$  below the switching frequency and well above the audio range.

- 4. V<sub>ref</sub> must be low impedance (for example, output of an op amp).

#### **Design Steps**

1. Set the error amplifier inverting signal gain.

$$Gain = -\frac{R_4}{R_3} = -1\frac{V}{V}$$

Select R<sub>3</sub> = R<sub>4</sub> = 10kΩ

2. Determine  $R_1$  and  $R_2$  to divide  $V_{ref}$  to cancel the non-inverting gain.

$$V_{o_{-dc}} = \left(1 + \frac{R_4}{R_3}\right) \left(\frac{R_2}{R_1 + R_2}\right) \times Vref$$

R<sub>1</sub>=R<sub>2</sub>=R<sub>3</sub>=R<sub>4</sub>=10kΩ, V<sub>o\_dc</sub>=2.5V

3. The amplitude of V<sub>tri</sub> must be chosen such that it is greater than the maximum amplitude of V<sub>i</sub> (2.0V) to avoid 0% or 100% duty cycle in the PWM output signal. Select V<sub>tri</sub> to be 2.1V. The amplitude of V<sub>1</sub> = 2.5V.

$$\begin{split} & \mathsf{V}_{tri} \ (\mathsf{Amplitude}) = \frac{\mathsf{R}_5}{\mathsf{R}_6} \times \mathsf{V}_1(\mathsf{Amplitude}) \\ & \mathsf{Select} \ \mathsf{R}_6 \ \mathsf{to} \ \mathsf{be} \ 10 \mathsf{k}\Omega, \quad \mathsf{then} \ \mathsf{compute} \ \mathsf{R}_5 \\ & \mathsf{R}_5 = \frac{\mathsf{V}_{tri}(\mathsf{Amplitude}) \times \mathsf{R}_6}{\mathsf{V}_1 \ (\mathsf{Amplitude})} = 8 \cdot 4\mathsf{k}\Omega \approx 8 \cdot 45\mathsf{k}\Omega \ (\mathsf{Standard} \ \mathsf{Value}) \end{split}$$

4. Set the oscillation frequency to 500kHz.

$$\begin{split} f_t &= \frac{R_6}{4 \times R_7 \times R_5 \times C_3} \\ \text{Set } C_3 &= 100 \text{pF}, \text{ then compute } R_7 \\ R_7 &= \frac{R_6}{4 \times f_t \times R_5 \times C_3} = 5.92 \text{k}\Omega \approx 5.90 \text{k}\Omega \text{ (Standard Value)} \end{split}$$

5. Choose C<sub>1</sub> to limit amplifier bandwidth to below switching frequency.

6. Select  $C_2$  to filter noise from  $V_{ref}$ .  $C_2 = 100nF$  (Standard Value)

$$f_{\text{div}} = \frac{1}{2 \times \pi \times C_2 \times \frac{R_1 \times R_2}{R_1 + R_2}} = 320 \text{Hz}$$

TEXAS INSTRUMENTS

www.ti.com

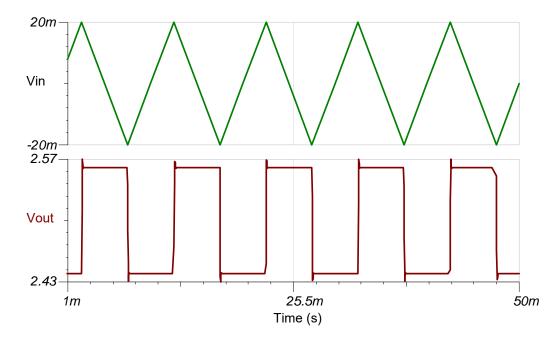

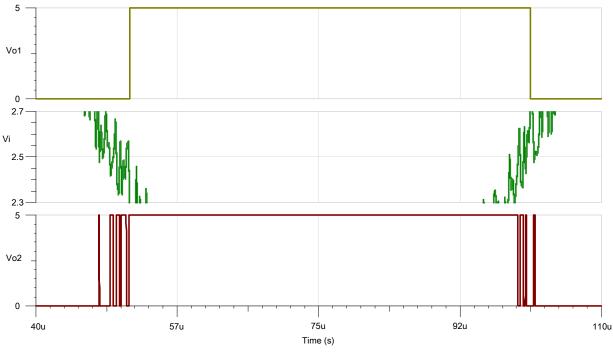

### **Transient Simulation Results**

#### **Design References**

See TIPD108, www.ti.com/tool/tipd108

#### **Design Featured Op Amp**

| OPA2365           |                            |  |  |  |  |

|-------------------|----------------------------|--|--|--|--|

| V <sub>ss</sub>   | 2.2V to 5.5V               |  |  |  |  |

| V <sub>inCM</sub> | Rail-to-rail               |  |  |  |  |

| V <sub>out</sub>  | Rail-to-rail               |  |  |  |  |

| V <sub>os</sub>   | 100µV                      |  |  |  |  |

| l <sub>q</sub>    | 4.6mA                      |  |  |  |  |

| I <sub>b</sub>    | 2pA                        |  |  |  |  |

| UGBW              | 50MHz                      |  |  |  |  |

| SR                | 25V/µs                     |  |  |  |  |

| #Channels         | 2                          |  |  |  |  |

| www.ti.com/pr     | www.ti.com/product/opa2365 |  |  |  |  |

#### **Design Comparator**

| TLV3502                    |              |  |  |  |  |

|----------------------------|--------------|--|--|--|--|

| V <sub>ss</sub>            | 2.2V to 5.5V |  |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |  |  |

| V <sub>os</sub>            | 1mV          |  |  |  |  |

| l <sub>q</sub>             | 3.2mA        |  |  |  |  |

| l <sub>b</sub>             | 2pA          |  |  |  |  |

| UGBW                       | -            |  |  |  |  |

| SR                         | -            |  |  |  |  |

| #Channels                  | 2            |  |  |  |  |

| www.ti.com/product/tlv3502 |              |  |  |  |  |

# **Design Alternate Op Amp**

| OF                         | OPA2353      |  |  |  |  |

|----------------------------|--------------|--|--|--|--|

| V <sub>ss</sub>            | 2.7V to 5.5V |  |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |  |  |

| V <sub>os</sub>            | 3mV          |  |  |  |  |

| lq                         | 5.2mA        |  |  |  |  |

| I <sub>b</sub>             | 0.5pA        |  |  |  |  |

| UGBW                       | 44MHz        |  |  |  |  |

| SR                         | 22V/µs       |  |  |  |  |

| #Channels                  | 2            |  |  |  |  |

| www.ti.com/product/opa2353 |              |  |  |  |  |

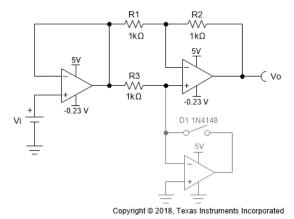

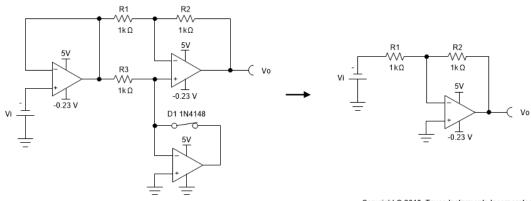

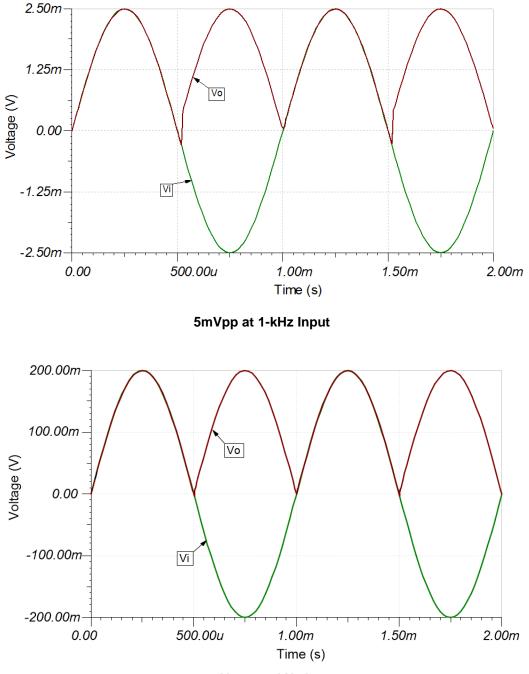

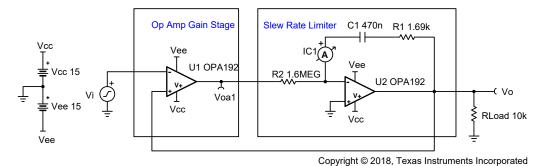

# Analog Engineer's Circuit: Op Amps SBOA222-February 2018

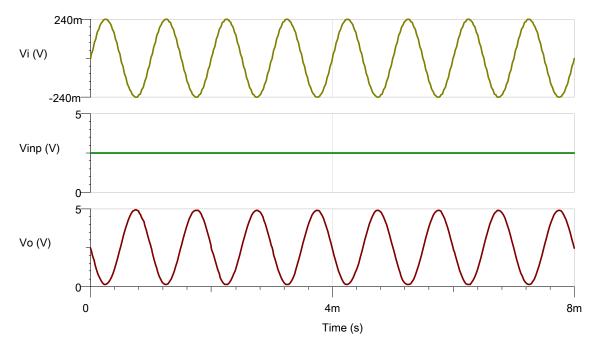

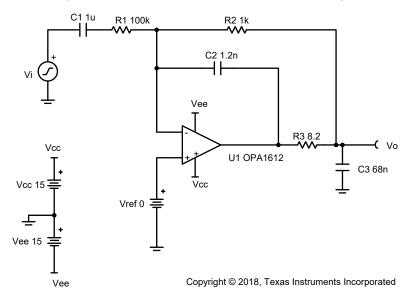

# AC Coupled (HPF) Inverting Amplifier Circuit

#### **Design Goals**

| Input             |                   | Output            |                   | Supply          |                 |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

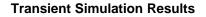

| -240mV            | 240mV             | 0.1V              | 4.9V              | 5V              | 0V              | 5V               |

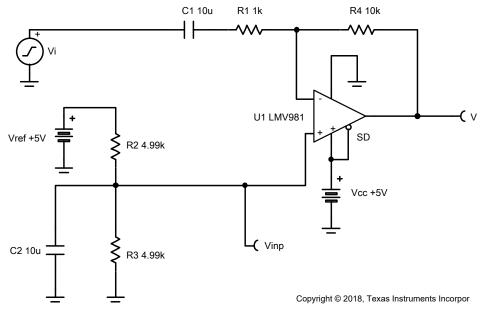

#### **Design Description**

This circuit amplifies an AC signal and shifts the output signal so that it is centered at half the power supply voltage. Note that the input signal has zero DC offset so it swings above and below ground. The key benefit of this circuit is that it accepts signals which swing below ground even though the amplifier does not have a negative power supply.

- 1.  $R_1$  sets the AC input impedance.  $R_4$  loads the op amp output.

- 2. Use low feedback resistances to reduce noise and minimize stability concerns.

- 3. Set the output range based on linear output swing (see A<sub>ol</sub> specification).

- 4. The cutoff frequency of the circuit is dependent on the gain bandwidth product (GBP) of the amplifier. Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>4</sub>. Adding a capacitor in parallel with R<sub>4</sub> will also improve stability of the circuit if high-value resistors are used.

#### **Design Steps**

1. Select  $R_1$  and  $R_4$  to set the AC voltage gain.  $R_1=1 \ k\Omega$  (Standard Value)

$$R_4 \!=\! R_1 \! \times \left| G_{ac} \right| \!=\! 1 \; k\Omega \times \left| -10 \frac{V}{V} \right| \!=\! 10 k\Omega \; (\text{Standard Value})$$

2. Select  $R_2$  and  $R_3$  to set the DC output voltage to 2.5V.  $R_3 = 4.99 k\Omega$  (Standard Value)

$$R_2 = \frac{R_3 \times V_{ref}}{V_{DC}} - R_3 = \frac{4.99 k_{\Omega} \times 5V}{2.5V} - 4.99 k_{\Omega} = 4.99 k_{\Omega}$$

3. Choose a value for the lower cutoff frequency,  $f_i$ , then calculate  $C_1$ .

4. Choose a value for  $f_{div}$ , then calculate  $C_2$ .

$$\begin{split} f_{div} &= 6.4\text{Hz} \\ R_{div} &= \frac{R_2 \times R_3}{R_2 + R_3} = \frac{4.99 \text{k}\Omega \times 4.99 \text{k}\Omega}{4.99 \text{k}\Omega + 4.99 \text{k}\Omega} = 2.495 \text{k}\Omega \\ C_2 &= \frac{1}{2 \times \pi \times R_{div} \times f_{div}} = \frac{1}{2 \times \pi \times 2.495 \text{k}\Omega \times 6.4\text{Hz}} = 9.96 \mu\text{F} \approx 10 \mu\text{F} \text{ (Standard Value)} \end{split}$$

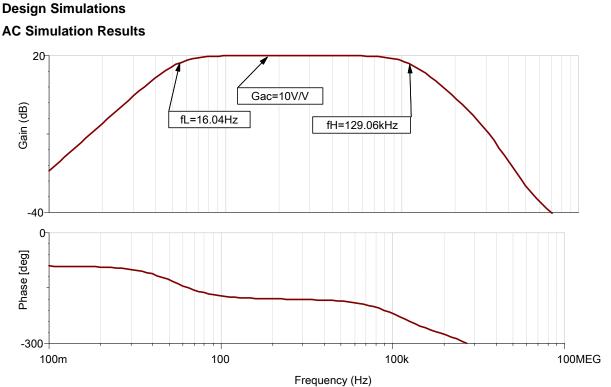

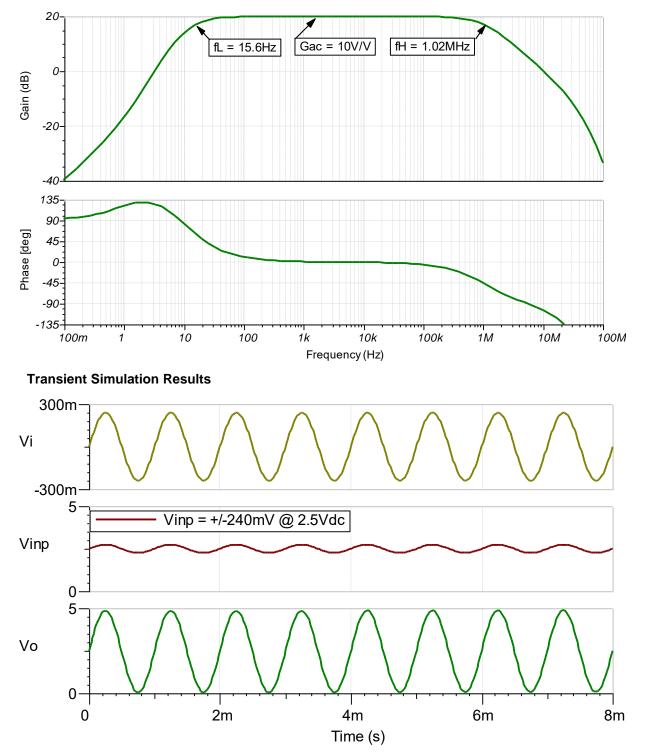

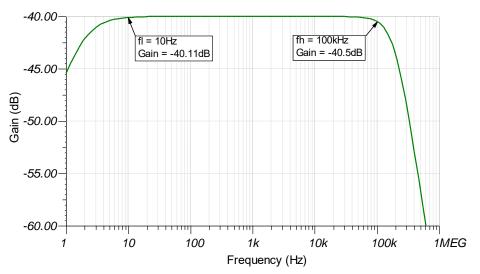

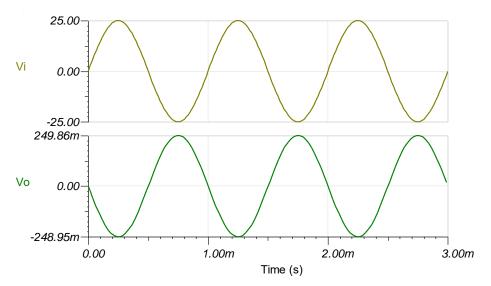

5. The upper cutoff frequency,  $f_h$ , is set by the noise gain of this circuit and the gain bandwidth (GBW) of the device (LMV981).